**Zeitschrift:** Bulletin des Schweizerischen Elektrotechnischen Vereins

**Herausgeber:** Schweizerischer Elektrotechnischer Verein ; Verband Schweizerischer Elektrizitätswerke

**Band:** 57 (1966)

**Heft:** 1

**Artikel:** Einige Probleme integrierter Digitalschaltungen

**Autor:** Guggenbühl, W.

**DOI:** <https://doi.org/10.5169/seals-916552>

#### **Nutzungsbedingungen**

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. [Mehr erfahren](#)

#### **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. [En savoir plus](#)

#### **Terms of use**

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. [Find out more](#)

**Download PDF:** 15.01.2026

**ETH-Bibliothek Zürich, E-Periodica, <https://www.e-periodica.ch>**

# Einige Probleme integrierter Digitalschaltungen<sup>1)</sup>

Von W. Guggenbühl, Zürich

621.38-181.4:62.374.32:511

Nach den Definitionen der Begriffe integrierte Schaltung und Digitalschaltung werden Probleme der Schaltungstechnik diskutiert. Der erste Teil befasst sich mit einigen Eigenschaften der integrierten Schaltelemente. Beispiele ausgeführter Schaltungen illustrieren verschiedene gegenüber der klassischen Bauart neue Aspekte der Schaltungstechnik. Der zweite Teil befasst sich mit der Frage des Geschwindigkeits-Leistungsproduktes und der Störfestigkeit von Digitalschaltungen. Die Frage der auftretenden Störungen wird diskutiert und einige Massnahmen zur Verbesserung der Störfestigkeit angegeben.

Après avoir défini ce qu'on entend par «circuit intégré» et par «circuit digital», l'auteur discute certains problèmes que pose la technique des circuits électroniques. Dans la première partie de l'article il décrit quelques propriétés des éléments de circuits intégrés et montre, au moyen d'exemples réalisés, par quels aspects la nouvelle technique des circuits se distingue de la technique classique. La seconde partie de l'article traite de la question du produit vitesse-puissance et de la résistance des circuits digitaux aux effets perturbateurs. L'auteur nous entretient des dérangements possibles et de quelques mesures aptes à les éviter.

## 1. Begriffs-Erläuterungen

Der Begriff der *integrierten Schaltung* wird in dieser Arbeit als im wesentlichen bekannt vorausgesetzt. Die Grundlagen des Aufbaus und der Herstellung integrierter Schaltungen sind im Rahmen verschiedener Tagungen und Vorträgen wiederholt besprochen worden [1, 2, 3]<sup>2)</sup>.

Die folgenden Ausführungen beziehen sich hauptsächlich auf die heute im Brennpunkt des Interesses stehenden Silizium-Monoblock-Schaltungen (silicon monolytic circuits), wenn auch viele der Überlegungen auf andere Typen (wie z. B. Dünnschichtschaltungen) anwendbar sind. Bei den Silizium-Schaltungen handelt es sich bekanntlich um Mikro-Miniatur-Anordnungen, bei denen alle Schaltelemente (Transistoren, Dioden, Widerstände, Kapazitäten) mit Hilfe derselben technologischen Verfahren in einem Siliziumplättchen erzeugt und durch aufgedampfte metallische Leiter mit-

Effekte dieser Isolationstechnik (parasitäre Elemente) wird später eingegangen.

Der zweite der zu definierenden Begriffe betrifft die *Digitalschaltungen*. In Digitalschaltungen hat jedes Schaltelement nur zwei Zustände zu unterscheiden. Dazu ist z. B. jede Art Schalter geeignet; viele der früheren Rechenmaschinen sind denn auch mit Relais gebaut worden, wobei die beiden logischen Niveaus (O und L) durch den geöffneten und den geschlossenen Zustand gegeben sind. Geschwindigkeitsüberlegungen verlangen elektronische Schalter, unter denen die Transistoren und Dioden im letzten Jahrzehnt eine dominierende Stellung errungen haben. Bei den zu behandelnden integrierten Schaltungen geht die Frage nicht nach dem eigentlichen Schalterelement — hier werden wie früher Transistoren und Dioden verwendet — sondern nach der Art der Kombination dieser Elemente zu logischen Verknüpfungseinheiten. In diesen logischen Schaltungen werden die Zustände verschiedener Schalter nach bestimmten Regeln miteinander zu einem Resultat kombiniert, das wieder für die Stellung weiterer Schalter mitverantwortlich wird. Da in der Folge wiederholt von solchen Grundschaltungen die Rede ist, sollen kurz einige Begriffe klargestellt werden.

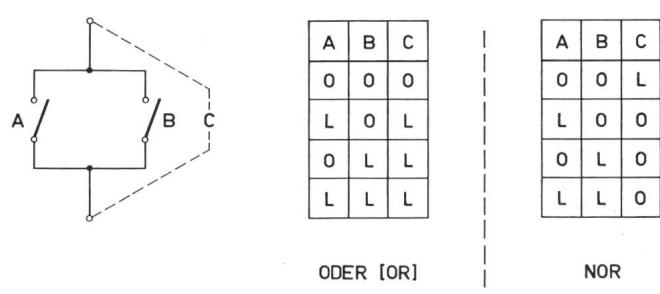

Bei der Zerlegung digitaler Systeme in möglichst wenige, gleichartige logische Grundeinheiten findet man, dass mindestens eine der beiden einfachen Verknüpfungsschaltungen UND, ODER verbunden mit einem Inverter gebraucht wird. Die Fig. 2 und 3 erläutern diese beiden Operationen mit Hilfe von Ersatzbildern und Funktionstabellen. Wählt man mechanische Schalter als logische Entscheidungselemente und legt man fest, dass L einem geschlossenen, O einem offenen Pfad entsprechen soll, so repräsentiert die Parallelschaltung von zwei Kontakten (Fig. 2) die ODER-Verknüpfung (engl. OR). Es genügt hier nämlich, dass *entweder A oder B* geschlossen (L) ist, um den Pfad C zu schliessen. Demgegenüber stellen zwei seriegeschaltete Kontakte eine UND-Ver-

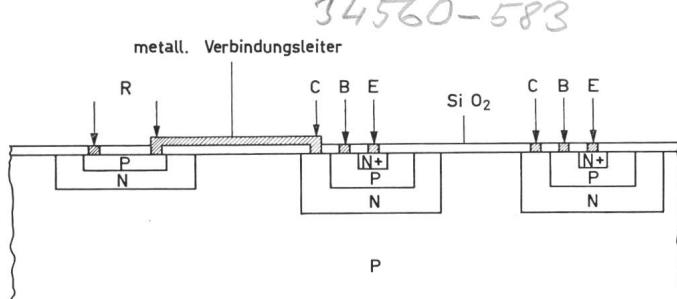

Fig. 1

Prinzipieller Aufbau einer Silizium-Monoblock-Schaltung

(zwei Transistoren und ein Widerstand)

E Emitter; B Basis; C Kollektor; R Widerstand; SiO<sub>2</sub> Siliziumdioxyschicht

einander verbunden werden. Fig. 1 zeigt als Beispiel einige in einem Si-Plättchen eingebettete Schaltelemente (zwei Transistoren und einen Widerstand). Die gegenseitige Isolation dieser Elemente erfolgt mit Hilfe des Silizium-Grundplättchens (Substrat) in das diese Elemente eingebettet sind; legt man diese P-leitende Si-Zone an den negativsten Punkt der Schaltung, so werden die einzelnen Schaltelemente durch zwei gegeneinander geschaltete gesperrte Dioden voneinander isoliert, da jedes der Elemente mit dem Substrat durch einen gesperrten P-N-Übergang verbunden ist. Es ist das Bestreben der meisten Schaltungshersteller mit möglichst wenig Isolationsdioden auszukommen, d. h. möglichst viele Schaltelemente in derselben Isolationsregion unterzubringen. Die Grösse des Siliziumplättchens, die wesentlich in den Preis der Schaltung eingeht, wird dann minimal. Auf weitere

<sup>1)</sup> Vortrag, gehalten an der Elektroniktagung der «fera 65» am 27. August 1965 in Zürich.

<sup>2)</sup> Siehe Literatur am Schluss des Aufsatzes.

Zur Definition der ODER- und NOR-Verknüpfungen

A, B Einzelschalter; C resultierender Schaltpfad; L Schalter geschlossen; O Schalter offen

Fig. 3

Zur Definition der UND- und NAND-Verknüpfung

Erklärungen siehe Fig. 2

knüpfung (engl. AND) dar (Fig. 3), da *sowohl A als auch B* geschlossen sein muss, um den Gesamtpfad C zu schliessen.

Die Verwendung von Transistoren in logischen Verknüpfungsschaltungen bringt zusätzlich eine Umkehrung der logischen Niveaus ( $L \rightarrow 0$ ,  $0 \rightarrow L$ ) entsprechend der Phasenumkehrung in Emitterbasisverstärkern.

Anstelle der ODER-Verknüpfung tritt deshalb bei Verwendung von Transistoren die NICHT—ODER = NOR-Funktion, anstelle der UND-(AND)-Funktion die NAND-Beziehung. Die entsprechenden Funktionstabellen sind in den Fig. 2 und 3 angegeben. Zu einer vollständigen logischen Familie gehören auch Speicher- oder Flip-Flop-Schaltungen. Man kann zeigen, dass diese aus einer Kombination von Grundschaltungen aufgebaut werden können, so dass sich eine gesonderte Besprechung in diesem Rahmen erübrigt.

Dem Digital-Spezialisten ist es nicht neu, als Grundbausteine genormte Verknüpfungsschaltungen zu verwenden und sich nicht bei jeder neuen Anwendung eine Schaltung nach Mass aus Einzelementen zu entwickeln. Fast jede grössere Firma hat zu diesem Zweck ihr Baukastensystem entwickelt oder kauft die betreffenden Schaltungen bei einem dafür spezialisierten Hersteller. Bedeutet also die Verwendung integrierter Schaltungen in diesem Sinne keinen wesentlichen Schritt — wenn man von der Tatsache absieht, dass unter Umständen die Herstellung der Schaltung in andere Hände übergeht — so gibt es doch einen ganzen Kreis technischer Fragen, die sich beim Übergang auf diese Technik stellen, aus dem einige Punkte herausgegriffen und diskutiert werden sollen.

## 2. Eigenschaften integrierter Schaltelemente

Beim Entwurf einer integrierten Schaltung steht man verglichen mit der Technik diskreter Komponenten, vor folgenden zusätzlichen Problemen <sup>3)</sup>:

1. Schaltelemente können, was Temperaturabhängigkeit und Fabrikationsstreuung betrifft, nicht mit der Qualität konventioneller Bauelementen hergestellt werden und ihre Typen-Vielfalt ist wesentlich eingeengt.

Insbesondere sind Bauelemente mit grossen Widerstands- und Kapazitätswerten schwer herzustellen und Induktivitäten praktisch ganz ausgeschlossen. Als Erleichterung beim Entwurf integrierter Schaltungen hilft die Tatsache, dass wenigstens das Verhältnis der Werte von Paaren integrierter Schaltelemente über grössere Temperaturbereiche relativ eng toleriert werden kann.

2. Alle Schaltelemente haben, als Folge der Isolierung durch Dioden, eine Streukapazität gegen das Substrat und zeigen unter Umständen auch andere unerwünschte parasitäre Eigenschaften.

<sup>3)</sup> Die hier aufgeführten Probleme beziehen sich vor allem auf die in Fig. 1 gezeichnete Grundform der integrierten Si-Monoblockschaltungen. Durch Anwendung neuerer Herstellungsverfahren mit zusätzlichen Fabrikationsschritten (Unterdiffusion [4], aufgedampfte Widerstände [3], dielektrische Isolation [13]) können bessere Eigenschaften erreicht werden.

3. Das gegenseitige Preisverhältnis der verschiedenen Schaltelemente ist gegenüber den klassischen Bauelementen verschoben. Transistoren sind am billigsten, gefolgt von Widerständen und Kondensatoren.

Zur Illustration dieser Probleme werden die hauptsächlichsten Bauformen der Elemente in integrierter Technik kurz diskutiert.

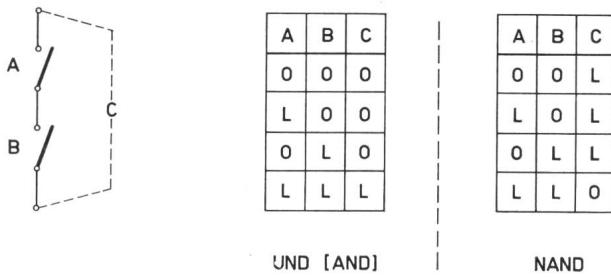

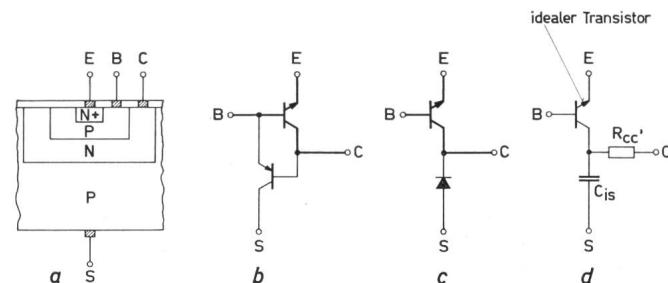

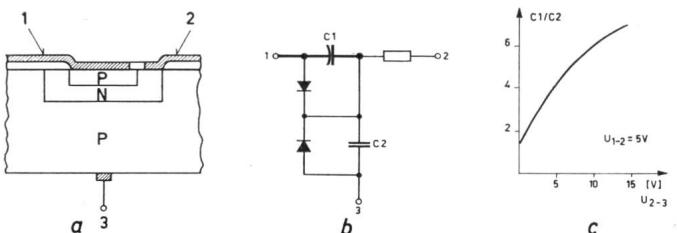

Der **Transistor**, von dessen modernster Herstellungsform, der Planartechnik, die ganze integrierte Silizium-Technik ausgegangen ist, kann relativ einfach und vor allem kleinflächig hergestellt werden. Er erscheint mit dem Substrat zusammen als Vierschichtelement (Fig. 4a), wie es z. B. von den gesteuerten Gleichrichtern her bekannt ist. Ein etwas oberflächliches Ersatzbild aus der Technik der «Controlled Rectifiers» zeigt diese Vierschichtstruktur als Kombination eines N-P-N- und eines P-N-P-Transistors (Fig. 4b), wobei aber im vorliegenden Fall des integrierten Transistors der P-N-P-Transistor ein unerwünschtes (parasitäres) Element ist. Das Ersatzschaltbild reduziert sich, sofern man die P-N-Übergänge zwischen Basis und Kollektor und zwischen Kollektor und Substrat in Sperrrichtung betreibt (was dem normalen Betrieb des Transistors als Verstärker entspricht) auf eine einfache gesperrte Diode zwischen Kollektor und Substrat (Fig. 4c) die bei der heutigen Vollkommenheit der Siliziumtechnik praktisch nur durch ihre Sperrschiichtkapazität stört. Außerdem ist der Zuleitungswiderstand zum Kollektor relativ gross (Fig. 4d).

Anders liegen die Verhältnisse, wenn integrierte Transistoren als Schalter betrieben werden. Beim üblichen «gesättigten» Schalterbetrieb wird im «ein» Zustand die Kollektor-Basis-Diode flusspolarisiert. Dasselbe gilt nun nach Fig. 4b aber auch für den Emitter des parasitären P-N-P-Transistors, der unter diesen Umständen Minoritätsträger ins Substrat (seinen Kollektor) hinein injiziert. Dieser unerwünschte Strom wird heute bei den integrierten Schaltungen meistens durch eine künstliche Verschlechterung des P-N-P-Transistors mit Hilfe von eindiffundierten, lebensdauertötenden Störstellen (Gold) auf ein erträgliches Mass reduziert. Durch diese Gewaltmassnahmen werden aber auch die Eigenschaften der N-P-N-Transistoren verschlechtert. Von der Golddiffusion kann abgesehen werden, wenn man nur nichtsättigende Transistorschalter verwendet.

**Dioden** können aus Transistoren hergestellt werden, indem man zwei Elektroden (meist Basis und Kollektor) miteinander verbindet. Im übrigen gelten dieselben Gesichtspunkte wie für Transistoren.

Fig. 4

Parasitäre Eigenschaften integrierter Transistoren

a bipolarer Transistor mit Substrat; b Ersatzschaltbild als Kombination eines N-P-N- und P-N-P-Transistors; c Isolationsdiode bei Sperrpolarisierung von B-C und C-S; d Kleinsignal-Ersatzschaltbild der «passiven» parasitären Elemente

$C_{is}$  Kapazität der Isolationsdiode;  $R_{cc'}$  Kollektorzuleitungswiderstand; S Substrat

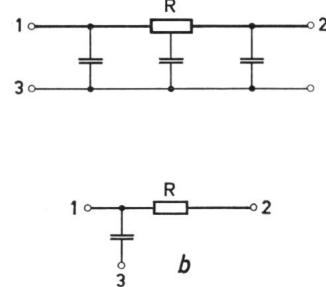

Fig. 5

**Parasitäre Eigenschaften integrierter Widerstände**

a Aufbau eines integrierten Widerstandes; b Ersatzschaltbilder; R Widerstand; 1, 2 Anschluss des Widerstandes; 3 Anschluss der Isolationsregion

**Widerstände** (Fig. 5) werden meistens zusammen mit dem Basis-Diffusionsvorgang der Transistoren hergestellt (ausnahmsweise zusammen mit dem Emitter oder Kollektor). Sie liegen im ersten Fall in einem N-leitenden Isolationsbett. Wird dieses an den positivsten Punkt der Schaltung gelegt, so können alle Widerstände der Schaltung in diese eine Isolationszone hineingebaut werden. Trotzdem beanspruchen die Widerstände relativ viel Siliziumoberfläche, weil sie, besonders im Falle grösserer Widerstandswerte, in relativ langen mäanderförmigen Faden gebaut werden müssen. Die verwendete Diffusionstechnik erlaubt nur die Herstellung von Widerständen mit relativ grossen Toleranzen und Temperaturkoeffizienten, wenn man vom «Gleichlauf» der Eigenschaften paarweise im selben Plättchen herstellter Elemente absieht.

Die Skala der realisierbaren Widerstandswerte ist bescheiden. Hochohmige Widerstände beanspruchen eine grosse Fläche auf dem Siliziumplättchen.

Auch die Widerstände sind mit kapazitiven Streueffekten gegen das Substrat behaftet. Diese müssten genau genommen als verteilte RC-Leitung in die Rechnung einbezogen werden (wobei der Kapazitätsbelag über die Widerstandslänge als Folge des Spannungsabfalles variiert). Eine vereinfachte Berechnung erfasst den Widerstand als RC-Glied (Fig. 5b).

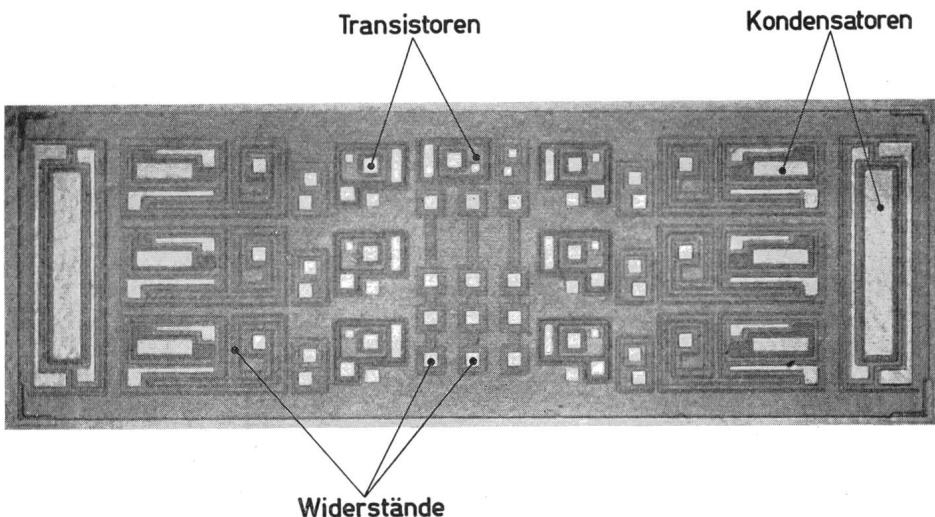

Der **Kondensator** ist das unbeliebteste der realisierbaren, integrierten Schaltelemente. Oft wird die Sperrschiichtkapazität eines P-N-Übergangs (in Sperrrichtung gepolt) verwendet, wenn kapazitive Effekte in integrierter Technik notwendig sind.

Fig. 6a zeigt den Aufbau eines auf diese Weise integrierten Kondensators. Das Ersatzbild in Fig. 6b zeigt einen beträchtlichen «inneren» Zuleitungswiderstand zu den Kondensatorplatten und vor allem eine grosse Streukapazität gegen das Substrat. Es ist leider nicht zu vermeiden, dass diese Streukapazität auch bei günstiger Gleichspannungs-Polarisierung stark ins Gewicht fällt, wie dies die Kurve in Fig. 6c zeigt [4]. Die Kapazität muss außerdem polarisiert werden (negative Vorspannung der Diode), wenn man nicht zwei Dioden gegeneinander schaltet. Etwas günstiger liegen die Verhältnisse bei Kondensatoren, die auf der Oberfläche des Siliziumplättchens deponiert, das Siliziumdioxyd (sonst als Oberflächen-Schutzschicht in der Planartechnik benutzt) als Dielektrikum verwenden. Auch hier bleiben die Streukapazitäten und die beanspruchten Flächen gross.

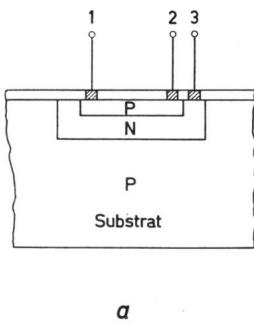

Fig. 7 illustriert die sich in Praxis ergebenden Flächenverhältnisse anhand einer älteren integrierten Schaltung (Texas Instrument, Serie 51, 1961). Es fallen vor allem die grossen von Kapazitäten und Widerständen beanspruchten Flächen auf.

Fig. 6

**Parasitäre Eigenschaften integrierter Kapazitäten**

a Aufbau einer integrierten Kapazität des Sperrschiichttyps; b Ersatzschaltbild; c Verhältnis von Nutz/Streukapazität für typische Betriebsdaten und Materialkonstanten [4]

$C_1$  Nutzkapazität;  $C_2$  Streukapazität;  $U_{1-2}$  Gleichspannung über Nutzkapazität;  $U_{2-3}$  Gleichspannung über Isolationsdiode

Für eine eingehende Diskussion der integrierten Schaltelemente sei auf ein kürzlich erschienenes Buch verwiesen [4].

### 3. Integrierte Digitalsschaltungen

Die geschilderten, veränderten Gesichtspunkte bezüglich der Schaltelemente haben zur Folge, dass in der integrierten Technik die blosse Kopie einer bereits bekannten und bewährten Schaltung mit konzentrierten Bauelementen in den meisten Fällen nicht zweckmäßig erscheint. Die folgenden Figuren sollen einen Eindruck von dieser «neuen» Schaltungstechnik vermitteln.

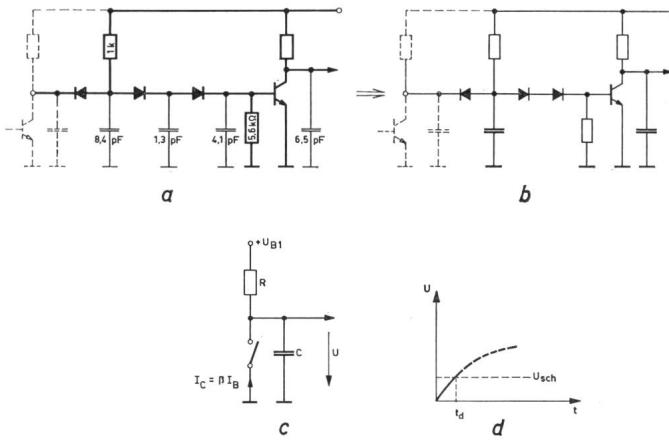

Als Demonstrationsbeispiel diene eine Verknüpfungsschaltung der so genannten *Dioden-Transistor-Logikfamilie DTL* (Fig. 8a). Man über-

Fig. 7

**Ansicht eines Halbleiterplättchens älterer Bauart mit eingebauten integrierten Schaltelementen**

(Texas Instruments Serie 51 ohne metallische Verbindungen)

Man beachte die grossflächigen Kondensatoren

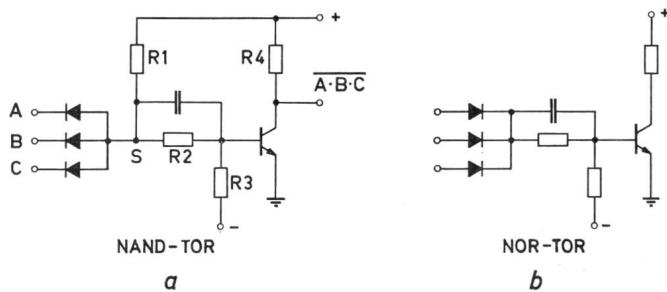

Fig. 8

**Dioden-Transistor-Logik-Schaltungen (DTL) klassischer Bauart***a* NAND-Tor; *b* NOR-Tor $R_1 \dots R_6$  Widerstand;  $S$  Summationspunkt;  $A, B, C$  logischer Eingang

zeugt sich durch einige einfache Überlegungen, dass es sich um ein NAND-Tor handelt (beim Beispiel Fig. 8a), wenn man die heute übliche Definition der logischen Niveaus (positive Quellenspannung = L, Masse = O) anwendet. Es müssen alle Eingänge A, B und C auf Quellenspannungspotential (= L) sein, damit der Transistor leitet und damit sein Ausgang auf Masse (= O) ist oder umgekehrt, genügt ein an Masse (= O) liegender Eingang, um den Punkt S der Schaltung ungefähr auf Masse zu legen und damit die Basis des Transistors mit Hilfe des Teilers  $R_2 - R_3$  negativ zu polarisieren und diesen zu sperren (Ausgang L). Der Kondensator dient zur Erhöhung der Schaltgeschwindigkeit.

Ein grosser Teil der heute praktisch verwendeten digitalen Baukastensysteme mit diskreten Schaltelementen verwendet diese DTL-Koppeltechnik. Einige der Gründe für ihre weite Verbreitung sind die logische Flexibilität, die relativ gute Störfestigkeit und der günstig ausgewogene Kompromiss zwischen der Anzahl der einzelnen Schaltelemente und ihren Preisen. Zur logischen Flexibilität (vielseitige Verwendbarkeit) trägt vor allem die Tatsache bei, dass die NOR-Funktion ebenso leicht realisiert werden kann (Fig. 8b), und dass die von den Dioden gebildeten AND und OR Verknüpfungsteile in Kaskade direkt hintereinander geschaltet werden können, wobei Transistoren nur von Zeit zu Zeit zur Umkehrung oder zur Wiederherstellung der ge normten logischen Niveaus gebraucht werden.

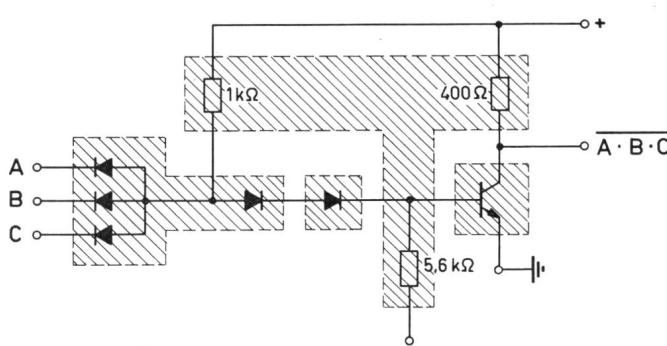

Kein Hersteller von Silizium-Monoblock-Schaltungen hat die DTL-NAND-Schaltung in der Form von Fig. 8a kopiert. Die dem klassischen Vorbild am nächsten stehende, praktisch gebrauchte integrierte Schaltung ist in Fig. 9 gezeichnet. Die schraffierten Zonen bezeichnen die Schalt-

elemente, die in einer Isolationsregion untergebracht werden können. Die Anzahl Zonen ist einer der Gesichtspunkte für die Elemente-Packungsdichte auf dem Si-Plättchen. Es fällt auf, dass ein Teil des in Fig. 8a für die Erzeugung der Transistor-Basisssperrspannung vorgesehenen Teilers  $R_2 - R_3$  durch die der integrierten Technik besser angepassten Dioden ersetzt ist. Man spricht von sog. Niveauverschiebungsdioden.

Der Polarisierungswiderstand (in Fig. 9 nach einer negativen Quelle geführt) wird in vielen Fällen mit der Masse verbunden. Die Anzahl der in Serie zum Transistoreingang verwendeten Dioden (Niveaudioden) bestimmt die Spannung, die am Eingang benötigt wird, um den Transistor leitend zu machen, und damit die Störunempfindlichkeit der Schaltung. Auf die NOR-Variante der klassischen Dioden-Transistor-Logik (Fig. 8b) wird meistens verzichtet; ein Ersatz dafür bildet die Möglichkeit der Parallelschaltung der Kollektoren verschiedener NAND-Tore. Der Ausgang wird dann O, wenn eines oder mehrere der einspeisenden NAND-Tore Strom liefern und damit eine zusätzliche ODER-Verknüpfungsmöglichkeit bildet.

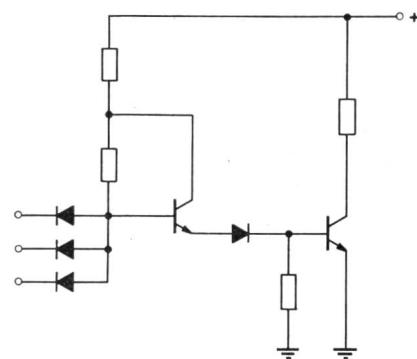

Fig. 10

Modifiziertes DTL-NAND-Tor

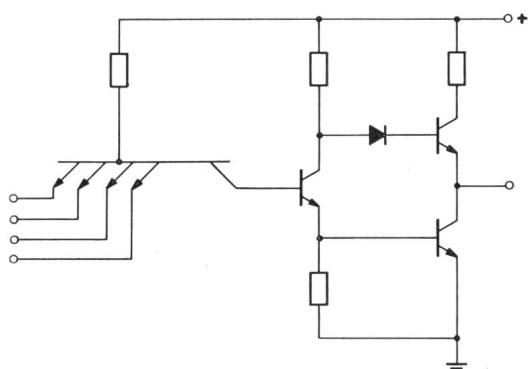

Eine weitergehende Abwandlung des DTL-NAND-Tores (Fig. 10) macht davon Gebrauch, dass es in der integrierten Technik ebenso einfach ist einen Transistor wie eine Diode zu erzeugen; sie ersetzt deshalb eine der Niveaudioden der Fig. 9 durch einen Transistor und verbessert mit Hilfe der zusätzlichen Verstärkung gewisse Schaltungseigenschaften.

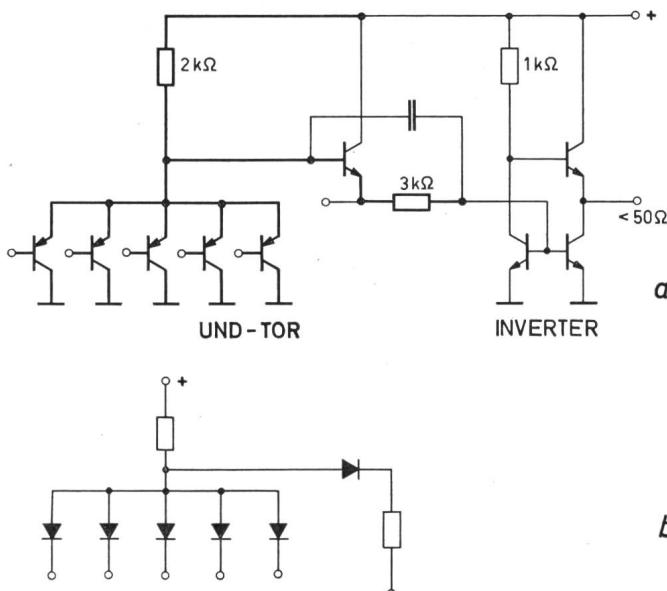

Einen weit grösseren Schritt bedeutet die Schaltungs variante der Fig. 11a. Die zugrunde liegende Ursprungsschaltung ist hier nur noch mit Mühe erkennbar. Als Hilfe zum Verständnis der Schaltung ist deshalb die äquivalente Diodenvariante in Fig. 11b eingezeichnet. Die Dioden des eigentlichen UND-Tores sind durch Transistoren in Emitter folgerschaltung (P-N-P-Typen mit gemeinsamen Substrat Kollektor) ersetzt, auch die Niveauverschiebungsdiode ist «transistorisiert». Die Grundidee ist offenbar wieder, die potentiell ohnehin vorhandenen Transistoren mit ihrer Verstärkung zu Gunsten der Eigenschaften der Gesamtschaltung zu nutzen. Bemerkenswert an der Schaltung in Fig. 11a ist ausserdem der Ersatz des Invertertransistors durch eine Gruppe von drei Transistoren mit dem Ziel, eine möglichst kleine Ausgangsimpedanz zu erzeugen. Diese Schaltung wäre bezüglich Anzahl Schaltelementen zur Zeit der diskreten Bauelemente zweifellos als zu aufwendig bezeichnet worden.

Der Zug in der integrierten Technik, die leichte Herstellbarkeit der Transistoren nach Möglichkeit auszunützen, hat

Fig. 9

**Integriertes DTL-NAND-Tor mit Niveaudioden (Grundform)**

Schraffierte Flächen: Gruppen von Schaltelementen mit gemeinsamer Isolation gegen Substrat

Erklärungen siehe Fig. 8

Fig. 11

Modifiziertes DTL-NAND-Tor

a Schaltschema; b dem UND-Tor-Teil äquivalente Diodenschaltung

zu einer weiteren Abwandlung der Diodenlogik geführt, die heute allgemein als Transistor-Transistorlogik (TTL oder T<sup>2</sup>L) bezeichnet wird. Das Vorhandensein verschiedener, teilweise gegeneinander geschalteter Dioden in der in Fig. 9 gezeigten Ursprungsform der besprochenen Schaltungsreihe hat den Gedanken nahegelegt, die Diodenkombinationen am Eingang der Schaltung durch Transistoren zu ersetzen. Dabei fällt besonders ins Gewicht, dass die integrierte Technik Transistoren mit mehreren Emitterdioden und gemeinsamem Kollektor geradezu anbietet. Es kann nun die ganze Eingangsdiodengruppe mitsamt einer Niveau-Verschiebungsdiode durch einen Mehrfachemitter-Transistor ersetzt werden. Fig. 12 zeigt ein praktisch verwendetes Schema dieser TTL-Gruppe. Die Transistor-Transistorlogik ist nun allerdings kein exaktes Äquivalent der Diodenlogik. Ein Transistor besteht ja nicht nur aus zwei gegeneinander geschalteten Dioden; im vollständigen Ersatzbild sind auch die Minoritätsinjektionsströme, mit denen sich Emitter- und Kollektordiode gegenseitig beschicken, zu berücksichtigen. Diese gegenseitige Verkoppelung der Dioden bringt Vorteile, aber auch zusätzliche Probleme, die die Transistor-Transistor-Logikschaltungen zu einer Untergruppe mit ihren besonderen charakteristischen Eigenheiten werden lassen. An der Schaltung in Fig. 12 ist wiederum die Inverterschaltung mit niederohmiger Ausgangsimpedanz bemerkenswert.

Fig. 12

Transistor-Transistor-Logik (TTL)

NAND-Tor

Die vorangegangene Diskussion ist von der klassischen DTL-Schaltung ausgegangen, um verschiedene, durch die Andersartigkeit der neuen Technik nahegelegte Modifikationen dieser Grundfamilie aufzuzeigen. Die Übersicht wäre jedoch einseitig, wenn sie nicht durch zwei andere Koppungstechniken, die in der Praxis grosse Bedeutung erlangt haben, ergänzt würde.

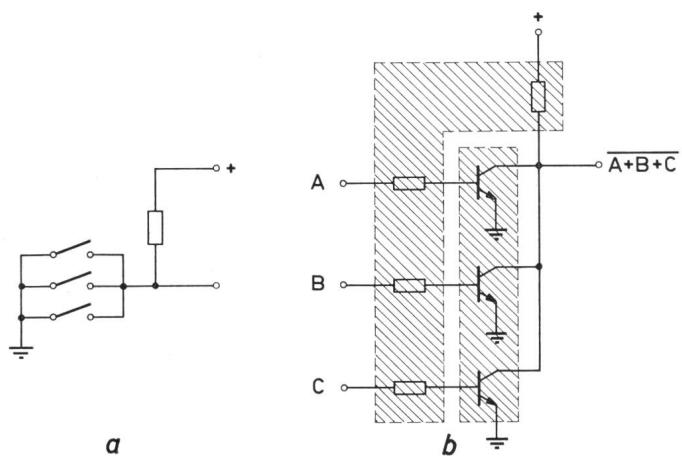

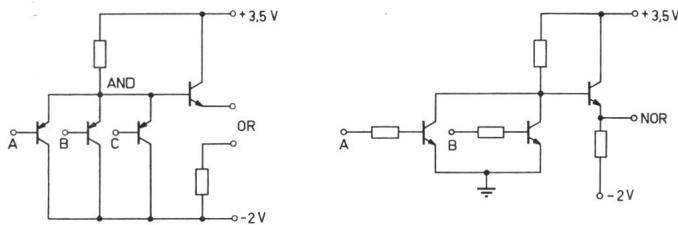

Die erste dieser Gruppen betrifft die Familie der sog. direkt gekoppelten Transistorlogik. Sie wurde früher meistens durch die Abkürzung DCTL (direct coupled transistor logic), in neuerer Zeit häufiger durch die Buchstabengruppe RTL (resistor-transistor-logic), bezeichnet. Die Grundidee dieser Verknüpfungsschaltungen besteht im Ersatz der in der Fig. 2 gezeichneten mechanischen Kontakte durch Transistorschalter. Der Ersatz der parallelgeschalteten Kontakte der Fig. 13a (ODER-Verknüpfung) durch Transistoren (Fig. 13b) ergibt als Folge der Phasenumkehr der Transistoren (Negation) eine sog. NOR-Schaltung, wie man sich leicht durch Nachkontrolle der einzelnen Fälle der Funktionentabelle in Fig. 2 überzeugen kann. Wie in Fig. 9 bezeichnen auch hier die schraffierten Regionen Elementengruppen, die in derselben Isolationsregion untergebracht werden können.

Fig. 13

Direktgekoppelte Logik (DCTL oder RTL) NOR-Tor

Schraffierte Flächen: Isolationsregionen

a Prinzip; b ausgeführte Schaltung

Erklärungen siehe Fig. 8

Die Tatsache, dass nur zwei Isolationsregionen benötigt werden, erklärt die grosse Bedeutung dieser Variante in der Frühzeit der integrierten Schaltungen. Sie wird heute noch wegen des kleinen Leistungsbedarfes und der günstigen Produktionskosten häufig verwendet.

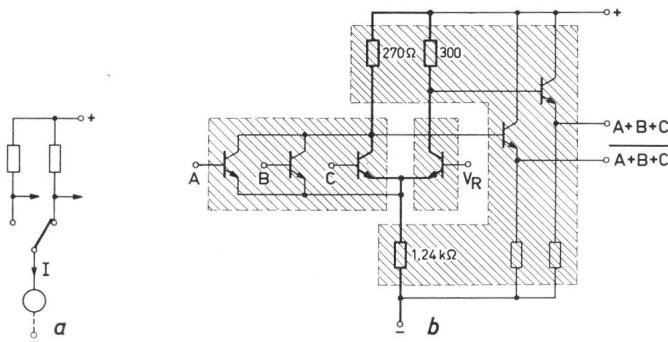

Unter den Digitalschaltungen hoher Geschwindigkeit nimmt die sog. emittergekoppelte (ECL) oder Stromschaltungs-Logik (current mode logic CML) eine wichtige Stellung ein. Aus der Schaltungstechnik der diskreten Elemente ist bekannt, dass der Transistor als Schalter dann besonders schnell arbeitet, wenn man verhindern kann, dass er im leitenden Zustand sättigt, d. h. seine Kollektordiode ins Flussgebiet umpolst. Das Verfahren zur Vermeidung der Sättigung, das den ECL-Schaltungen zugrunde liegt, wird anhand von Fig. 14a erläutert. Durch einen Umschalter führt man den aus einer hochohmigen Quelle eingespeisten Strom  $I$  wahlweise entweder dem einen oder dem anderen Belastungswiderstand zu und unterscheidet damit die logischen Größen O und L.

Fig. 14

**Emittergekoppelte Logikschaltung (ECL)**

a Prinzip; b ausgeföhrtes OR-NOR-Tor. Schraffierte Flächen: Isolationsregionen

I Quellenstrom;  $V_R$  Referenzspannung

Weitere Erklärungen siehe Fig. 8

Die in Fig. 14b gezeichnete integrierte Stromlogikschaltung zeigt diesen nun mit Transistoren in Differentialschaltung aufgebauten Umschalter (dick gezeichnet). Die «Stromquelle» besteht aus der negativen Spannungsquelle mit dem Seriowiderstand 1,24 kΩ. Zur Realisierung einer logischen Verknüpfung muss der Umschalter durch verschiedene Eingänge beeinflusst werden können; dies ist durch die Parallelschaltung dreier Transistoren für den Schalterpfad links realisiert. Es genügt, dass einer der Eingänge A, B, C gleich L wird, um den Strom durch den linken Lastwiderstand (270 Ω) zu steuern (ODER). Bei richtiger Dimensionierung wird die Spannung über dem Transistorschalter nicht Null, d. h. die Sättigung wird vermieden. Die Emitterfolger dienen zur Impedanzwandlung und zur Rückverschiebung der Ausgangsspannungsniveaus auf den für die nachfolgenden Basiskreise notwendigen Gleichspannungspiegel. Diese ECL-Schaltung stellt relativ hohe Anforderungen an die Stabilität der Gleichstrom-Arbeitspunkte der Transistoren, die nur dank der engen Toleranzen der Widerstandsverhältnisse, die bei integrierten Schaltungen möglich sind, eingehalten werden kann. ECL-Tore zeichnen sich durch grosse logische Flexibilität aus (OR- und NOR-Ausgänge).

Die Frage nach dem in einem spezifischen Fall anzuwendenden Schaltungstyp, die beim Einsatz von integrierten Schaltungen wohl als erste an den Verbraucher herantritt, ist nicht einfach und allgemein gültig zu beantworten. Da die Bedeutung zahlreicher technischer Gesichtspunkte, wie logische Flexibilität, Störsicherheit, Temperaturbereich, «Fan in, Fan out», Geschwindigkeit, Preis, im Rahmen eines Gesamtsystems abzuschätzen ist, wird sich wohl kaum eine einzige und absolut beste Lösung herauskristallisieren lassen.

Wo in der Technik viele Parameter gegeneinander abzuwegen sind, gibt es auch viele Meinungen über die «beste» Lösung. Es sprengt den Rahmen dieser Arbeit alle Vor- und Nachteile der einzelnen Schaltungsvarianten zu diskutieren. Aus der Fülle der Gesichtspunkte, die den Verbraucher interessieren, seien zwei herausgegriffen und etwas eingehender besprochen: das Geschwindigkeits-Leistungsprodukt und die Störempfindlichkeit.

#### 4. Geschwindigkeits-Leistungsprodukt

Es ist ein altes Ziel der elektronischen Schaltungstechnik die Verlustleistung der Schaltungskreise möglichst klein zu halten. Diese Forderung erhält im Fall der integrierten Schaltungen mit ihrer hohen potentiellen Baudichte noch mehr

Gewicht. Beim Übergang von der Röhren- zur Transistor-technik konnte dank der neuartigen physikalischen Vorgänge, die für den Verstärkermechanismus in Transistoren verantwortlich sind, parallel zur Volumenreduktion eine wesentliche Leistungseinsparung realisiert werden. Da sich die Art der Schaltelemente beim Schritt von den Transistor-schaltungen mit diskreten Elementen zu den integrierten Schaltungen nicht grundsätzlich geändert hat — es werden immer noch bipolare Transistoren und Dioden verwendet — so hat in diesem Falle die Leistungsreduktion mit der geometrischen Verkleinerung nicht Schritt gehalten. Es sprechen sogar bei integrierten Schaltungen verschiedene Gründe (grössere Element-Toleranzen, grössere Streukapazitäten) dafür, dass die Verlustleistung bei vergleichbarer Geschwindigkeit grösser wird als bei einer gleichen, aus diskreten Elementen aufgebauten Schaltung. Die erreichbare Baudichte wird denn auch heute bei grösseren Systemen nicht von der Geometrie der Schaltungen, sondern von den Problemen der Wärmeabfuhr her bestimmt.

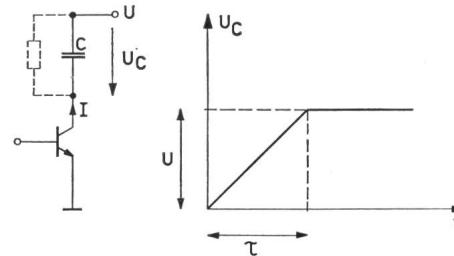

Über die Frage der Verkleinerung der Verlustleistung ist in letzter Zeit viel diskutiert worden [5]. Man kann physikalisch begründen, dass die logische Schaltungstechnik grundsätzlich nicht ohne Verlustleistung auskommen kann [6]; allerdings liegen die theoretisch pro logische Entscheidung geforderte Minimalenergie weit unter den heute in praktischen Systemen realisierten Verlusten. Ein technisch wichtiges Resultat dieser Untersuchungen ist ferner der Zusammenhang zwischen Verlustleistung und Schaltgeschwindigkeit in Digitalschaltungen. Zur Diskussion dieser Frage wird das Schaltungsmodell meistens weitgehend vereinfacht. Nach der Vernachlässigung aller technologischen Nebeneffekte wie Trägheit der Schalter usw. bleibt bei einem System, in dem die beiden logischen Niveaus durch ihre elektrostatischen Potentiale unterschieden werden, als physikalisch wesentlicher Vorgang die *Umladung einer Kapazität* übrig. Wird weiter angenommen, dass diese Umladung mit einem konstanten Strom  $I$  erfolgt (wie es z. B. durch einen Transistor gemäss Fig. 15 realisiert werden könnte), so beträgt die pro Schaltvorgang aufgewendete Energie:

$$E = U^2 C \quad (1)$$

Diese Energie muss während der Umschaltzeit  $\tau$  aufgebracht werden, so dass die mittlere Leistung  $P$ :

$$P = \frac{U^2 C}{\tau} \quad (2)$$

beträgt.

Diese Leistung wäre theoretisch nur dann dauernd aufzubringen, wenn das System mit maximaler Schaltsequenz läuft. Ein zeitweiser langsamerer Lauf würde weniger mitt-

Fig. 15

**Zur Frage des Geschwindigkeits-Verlustleistungsprodukts [Gl. (2)]**

C Kapazität; I Ladestrom; U Speisespannung;  $U_C$  Spannung über C;  $\tau$  Aufladezeit; t Zeit

Fig. 16

Zur Ableitung des Geschwindigkeits-Verlustleistungsprodukts einer praktischen Schaltung [Gl. (3)]

$$P_{td} \approx U_{B1} U_{sch}$$

a DTL-Schaltung mit Streukapazitäten; b vereinfachte Version von a; c stark vereinfachte Ersatzschaltung; d Kurvenform beim Ausschalten der Schaltung c;  $C$  Ersatzkapazität;  $I_g$  Kollektorstrom;  $\beta$  Stromverstärkungsfaktor;  $I_B$  Basisstrom;  $R$  Ladewiderstand;  $U$  Spannung über  $C$ ;  $U_{B1}$  Speisespannung;  $U_{sch}$  Schwellenspannung;  $t$  Zeit;  $t_d$  Verzögerungszeit

lere Leistung erfordern. Gl. (2) besagt, dass bei festgelegtem Spannungshub  $U$  und gegebener Kapazität  $C$  der Schaltung das Produkt aus Anstiegszeit  $\tau$  und Verlustleistung  $P$  konstant ist. Die bei einer bestimmten Schaltgeschwindigkeit aufzubringende Leistung fällt mit abnehmendem Spannungshub und Kapazität. Gl. (2) ist nicht für beliebige Werte von  $C$  praktisch anwendbar. Es wurde gezeigt [7], dass die Wellenimpedanz des freien Raumes und die Unbestimmtheitsrelation bei extrem kleinen Schaltzeiten den Anwendungsbereich von Gl. (2) einschränken.

Praktische Schaltungen entsprechen dem geschilderten Modell in verschiedener Hinsicht nicht genau<sup>4)</sup>. Wählt man als Beispiel wieder das Dioden-Logik-NAND-Tor, so wird man bei der Aufstellung eines Ersatzbildes in einem ersten Schritt (Fig. 16a) jedem der Schaltelemente eine Streukapazität gegen Erde zuordnen. Die zum Teil relativ grossen Kapazitätswerte sind durch die Isolationsdiode bedingt. Bei einer Reduktion auf das wesentliche der Schaltung (unter Verzicht auf Genauigkeit) wird man zunächst diese Kapazitäten in je einen Eingangs- und Ausgangsspeicher zusammenfassen (Fig. 16b) und schliesslich in einem letzten Schritt auch diese beiden Speicher vereinigen (Fig. 16c). Dioden und Transistoren sind dabei als schnell (verglichen mit den Umladeeffekten der Schaltungskapazität) vorausgesetzt.

Beim Öffnen des Schaltkontakte ist der wesentliche Teil  $t_d$  der Umladezeit des Kondensators im reduzierten Ersatzbild Fig. 16c beendet, wenn die Spannung über  $C$  die Schwellen  $U_{sch}$  erreicht hat, bei der der nachfolgende Schalter zu leiten beginnt. Die Zeit  $t_d$ , die in der Kondensatoraufladekurve der Fig. 16d eingetragen ist, wird als Verzögerungszeit der Stufe bezeichnet. Berechnet man wieder die der Quelle während des Umschaltvorgangs entnommene mittlere Leistung  $P$ , so folgt für das Geschwindigkeits-Leistungsprodukt mit den Bezeichnungen der Fig. 16c:

<sup>4)</sup> Die einzige bis heute bekannte Inverterschaltung, die nur während den Umschaltphasen Leistung konsumiert, verwendet komplementäre MOS-Transistoren des «Enhancement Typs» [8]. Sie ist erst im Laboratorium verfügbar.

$$P_{td} \approx C U_{B1} U_{sch} \quad (3)$$

$$(\text{Voraussetzung } U_{sch} \ll U_{B1})$$

Anstelle der Formel (2) ergibt sich somit ein Ausdruck, der Verlustleistung, Geschwindigkeit und die übrigen Schaltungsdaten durch eine im wesentlichen ähnliche Beziehung verknüpft. Wieder ist das Produkt Leistung  $\times$  Schaltzeit konstant, d. h. nur von den Spannungen und Kapazitäten abhängig. Man beachte, dass bei dieser praktischen Schaltung die Verlustleistung in einem der logischen Zustände (Schalter geschlossen) dauernd vernichtet wird, d. h. auch dann, wenn nur selten geschaltet wird.

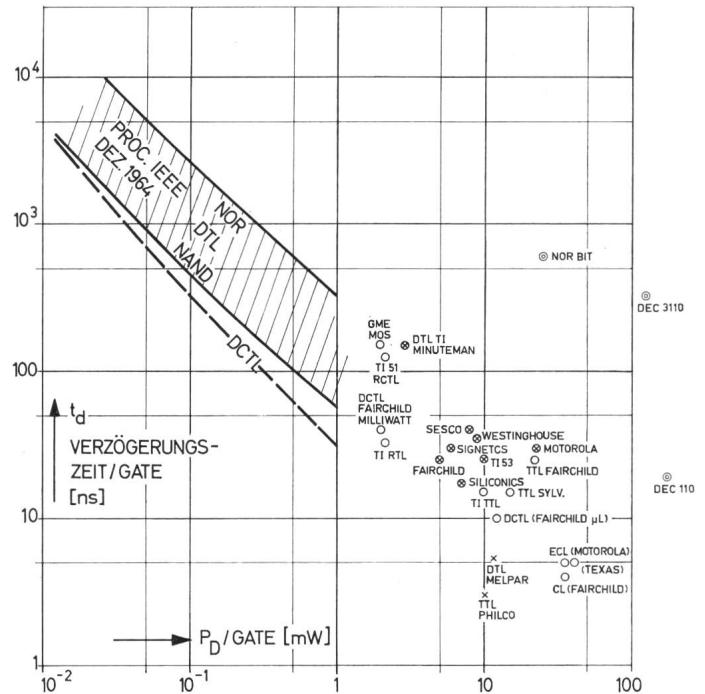

Als praktische Folgerung aus den Gl. (2) und (3) ist zu erwarten, dass die Verlustleistung von Digitalschaltungen proportional zu ihrer Geschwindigkeit (d. h. umgekehrt prop. zu  $t_d$ ) ansteigt. Eine Zusammenstellung der heute auf dem Markt befindlichen integrierten Schaltungen in Fig. 17 bestätigt dieses Gesetz. Die Grösse der Streuung des Schaltzeit-Leistungsproduktes, das nach Gl. (3) je nach Speisespannung, logischem Hub und Schaltkapazität verschieden sein kann, ist offenbar bei den heute handelsüblichen Typen relativ gering.

Man entnimmt der Fig. 17, dass das Gebiet der hohen Geschwindigkeit heute hauptsächlich von den emittergekoppelten Typen (ECL), dasjenige der kleinen Leistungen und langsam Geschwindigkeiten von den direktgekoppelten Systemen (DCTL, RTL) und das zentrale Feld von den diodengekoppelten (DTL) oder Transistor-Transistorlogik (TTL) beherrscht wird. Dabei gibt es einige Ausnahmen.

In Fig. 17 sind neben den integrierten Schaltungen auch einige ältere Digitalsysteme eingetragen (Doppelringe), die jedoch zum Teil noch oft Verwendung finden. Es fällt auf, dass die Verlustleistungen dieser Schaltungen um Grössen-

Fig. 17

Verzögerungszeit als Funktion der Verlustleistung einiger kommerziell erhältlicher integrierter Schaltungen

○ DCTL, RTL, TTL, ECL (Schaltungen); Ⓜ DTL (Schaltungen);  $\times$  Schaltungen im Versuchsstadium;  $\circ$  ältere digitale Baukastensysteme (diskrete Elemente)

links sind theoretische Resultate [12] über Kleineistungsschaltungen eingetragen

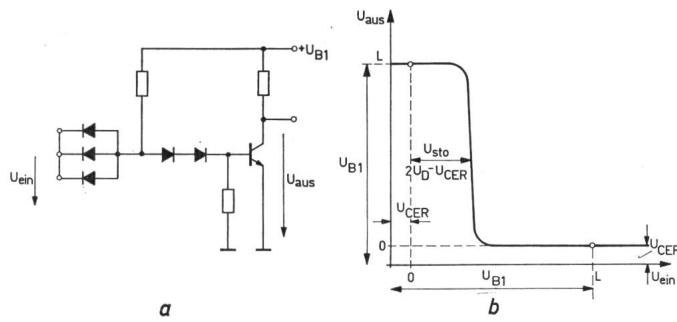

Fig. 18

**Zur Definition des Störabstandes in logischen Schaltungen

(Beispiel DTL-Schaltung)**

a Meßschaltung; b statische Transfercharakteristik

$O, L$  logarithmisches Niveau;  $U_{B1}$  Speisespannung;  $U_D$  Flußspannung der Niveaudioden;  $U_{CER}$  Kollektorrestspannung;  $U_{st0}$  Störabstand des Niveaus  $O$

ordnungen über den heutigen modernen Systemen liegen. Dies mag zum Teil von den langsamsten Transistoren herrühren, die in diesen Systemen Verwendung finden und deren Umschaltung etwas mehr Leistung erfordert. Ein anderer Teil der Leistung geht jedoch auf Kosten grösseren logischen Hubes und damit konservativerer Dimensionierung. Der aus Fig. 17 ersichtliche Übergang zu kleinen Leistungen bringt vor allem Probleme der Störempfindlichkeit.

Diesen Fragen ist der letzte Abschnitt der Arbeit gewidmet.

**5. Störempfindlichkeit**

Digitalschaltungen haben den Ruf grosser Betriebssicherheit. Die Eigenschaft, nur zwei Betriebszustände pro Schaltelement unterscheiden zu müssen, macht sie weitgehend unabhängig von Verstärkungsänderungen, Speisespannungsschwankungen usw. Auch Störspannungen bleiben ohne Einfluss, solange sie einen bestimmten Schwellwert, der zur Erzeugung einer Fehlinformation (z. B.  $O$  statt  $L$ ) ausreicht, nicht überschreiten. Grössere Störspannungen erzeugen allerdings willkürliche und, falls sie auf einen Speicher gelangen, dauernde Fehler im System.

Es gibt viele Anwendungsbereiche digitaler Steuerungen, z. B. Werkzeugmaschinensteuerungen, bei denen solche Fehler, auch wenn sie selten vorkommen, völlig untragbar sind, da sie den Verlust eines unter Umständen teuren Werkteils bedeuten.

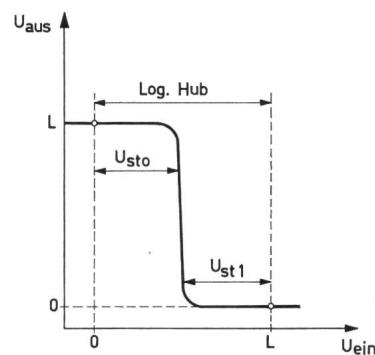

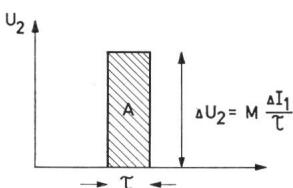

Die Störempfindlichkeit von Digitalschaltungen wird heute meistens anhand der statischen Transfercharakteristik (Ausgangsspannung als Funktion der Eingangsspannung) einer Torschaltung diskutiert. Diese Charakteristik hat die typische Form gemäss Fig. 18 (für ein DTL-NAND-Tor gezeichnet). Die Ausgangsspannung startet bei Eingangsspannung  $U_{ein} = 0$  mit dem Niveau der Speisespannung  $U_{B1}$  (logisch  $L$ ) und bei steigender Eingangsspannung bei einer typischen Schwellenspannung auf den Sättigungsspannungswert  $U_{CER}$  des Schalttransistors abzufallen. Da die Eingangsspannung  $U_{ein}$  immer gleich der Ausgangsspannung der vorangehenden Torschaltung ist, sind die beiden Arbeitspunkte der Schaltung eindeutig durch die Koordinaten  $(U_{CER}, U_{B1})$  und  $(U_{B1}, U_{CER})$  festgelegt. Man definiert nun als Störfestigkeit (engl. noise margin) der Schaltung die spannungsmässigen Abstände der beiden Arbeitspunkte vom Kippniveau. In Fig. 18 ist dieser Spannungsbetrag für das niedrigere der Eingangsniveaus der DTL-Schaltung angegeben; er baut sich auf aus den Schwellenspannungen der Niveaudioden  $2U_D$

abzüglich der Kollektorrestspannung  $U_{CER}$  des vorangehenden Transistors.

Aus Fig. 19, in der die mit der Transfercharakteristik zusammenhängenden Begriffe nochmals zusammengestellt sind, erkennt man leicht, dass die Summe der beiden Störabstände  $U_{st0}$  oder  $U_{st1}$  gleich dem Spannungsunterschied zwischen den zwei logischen Niveaus, dem sog. logischen Hub  $\Delta U$ , ist.

Im Fall symmetrischer Verhältnisse ist somit  $U_{st} = \Delta U/2$ ; in allen anderen Fällen ist der kleinere der beiden Störabstände weniger gross. Da der Spannungshub  $\Delta U$  wesentlich die Verlustleistung der Schaltung bestimmt [siehe z. B. Gl. (2)] erklärt sich nun auch die Abhängigkeit der Störfestigkeit von der Verlustleistung.

Man kann gegen diese spannungsmässige Definition des Störabstandes verschiedenes einwenden. Sie hat ihren Ursprung in der Vorstellung, dass eine niederohmige Quelle den hochohmigen Eingang der nachfolgenden Schaltung ansteuere, eine Vorstellung, die nicht für alle, aber doch für viele der logischen Schaltungen zutrifft. Zweifelsohne müssten bei einer genaueren Betrachtung die Abschlusswiderstände der in Frage stehenden Leitung in die Diskussion einzogen werden (Frage der Störleistung).

Ein weiterer Einwand richtet sich gegen die ausschliessliche Betrachtung der Eingangssignalleitung; Störungen können auch auf der Erdleitung, der Speiseleitungen und der Ausgangsleitung ankommen. Schliesslich ist noch zu beachten, dass Störungen in Digitalsystemen äusserst selten in der Form von Gleichspannungspegel-Verschiebungen auftreten; die überwiegende Anzahl Störungen erscheint in Form von Impulsen. Sucht man nach einem Mass für die Empfindlichkeit der Schaltungen in Bezug auf solche Störspitzen, so wird man für eine qualitative Betrachtung wieder das vereinfachte Ersatzbild Fig. 16c zu Hilfe nehmen. Der besprochene statische, spannungsmässige Störabstand entspricht in Fig. 16c der Schwellenspannung  $U_{sch}$ . Um die Stufe durch einen Impuls umzukippen, muss dieser mindestens die Ladung  $Q = CU_{sch}$  auf dem Kondensator plazieren können; mit anderen Worten, für den Störabstand ist ausser der statischen Schwelle, die selbstverständlich überschritten werden muss, die Speicherladung  $Q$  massgebend.

Die Entstehung der Störimpulse auf den Verbindungsleitungen zwischen den Toren kann zwei Ursachen haben:

- Übersprechen von Nachbarleitungen.

- Einstreuung von aussen.

Fig. 19

**Störabstand und logischer Hub**

$U_{st1}$  Störabstand des Niveaus  $L$

Weitere Erklärungen siehe Fig. 18

Fig. 20

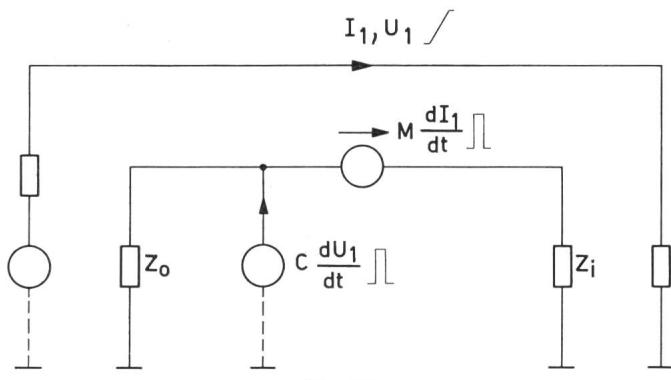

**Zur Frage des Übersprechens zwischen Signalleitungen**

$C$  gegenseitige Kapazität;  $I_1$  Strom auf Leitung 1;  $M$  Gegeninduktivität;  $U_1$  Spannung auf Leitung 1;  $Z_0$  Speisimpedanz der Leitung 2;  $Z_i$  Lastimpedanz der Leitung 2

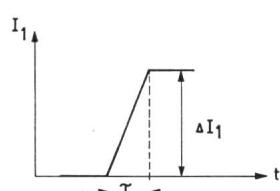

Im ersten Fall können die Störungen einigermaßen rechnerisch erfasst werden. Sind die Laufzeiten der Signale zwischen den Toren kleiner als die Anstiegszeiten der übertragenen Größen, so können die Übersprechsignale nach Fig. 20 diskutiert werden. Das Signal  $U_1$ ,  $I_1$  auf der oberen Leitung der Fig. 20 induziert auf die danebenliegende Leitung eine Spannung  $M(dI_1/dt)$  und einen Strom  $C(dU_1/dt)$ . Dem kapazitiven Übersprechen kann meistens mit Hilfe kleiner Ausgangsimpedanzen  $Z_0$  entgegengewirkt werden; sie sorgen dafür, dass sich keine wesentlichen Störspannungen an der Eingangsimpedanz  $Z_i$  der nachfolgenden Stufe aufbauen können. Diese Überlegung erklärt den Wert der niederohmigen Ausgangsstufen von logischen Schaltungen. Sie sind in jedem Fall bei längeren Verbindungsleitungen erforderlich. Bei den induktiven Übersprechspannungen ist die Fläche  $\Delta U_2 \tau$  der übersprechenden Signale möglichst klein zu halten. Man kann zwar zeigen, dass diese «Fläche» gemäß Fig. 21 bei gleichbleibenden Strom- und Spannungsamplituden von der Anstiegszeit  $\tau$  unabhängig ist; doch treten bei schnellen Schaltungen trotzdem verschärftete Probleme auf.

Entweder ist der Wert der aufzuladenden Kapazität  $C$  kleiner oder die Schaltungen niederohmiger und damit die Schaltströme  $I_1$  grösser als bei langsamem Stufen. Es ist deshalb unvermeidlich, dass die Störanfälligkeit der Schaltungen mit steigender Geschwindigkeit zunimmt. Gegenmassnahmen sind besonders sorgfältiger, verdrahtungstechnischer Aufbau (verdrillt oder induktionsarme, flächenförmige Erd- und Speisezuführungen usw.)

Der Vollständigkeit halber sei noch erwähnt, dass diese Betrachtungen für extrem schnelle Schaltungen mit Anstiegszeiten, die kürzer oder gleich lang wie die Signalausbreitungszeiten sind, nicht zutreffen. Die Probleme sind in diesen Fällen mit der Leitungstheorie zu behandeln.

Alle auf dem Markt befindlichen integrierten Baukastensysteme bieten bezüglich dieser

Fig. 21

Verhältnisse beim induktiven Übersprechen von Leitung 1 auf Leitung 2 der Fig. 20

Fläche  $A = \text{proportional } M \cdot \Delta I_1$ ;  $U_2$  Spannung auf Leitung 2

Weitere Bezeichnungen siehe Fig. 20

Fig. 21

inneren Eigenstörungen keine wesentlichen Probleme, sofern beim Entwurf der Verdrahtung die notwendige Sorgfalt angewendet wird. Je höher die Schaltgeschwindigkeit, umso kritischer wird diese Forderung.

Weit mehr Sorgen bereiten im allgemeinen die von aussen in ein System einlaufenden Störungen. Sie werden z. B. erzeugt durch Motorschalter, Relais, Blitzschlag usw. Hier wirkt sich die in der modernen Digitaltechnik im Zuge der Integration vorgenommene Leistungsreduktion voll aus. Während die logischen Hübe und damit die Ansprechschwellen verkleinert und die Geschwindigkeiten gesteigert werden, ist die Grösse der äusseren Störenergie im allgemeinen gleich geblieben. Als Massnahmen gegen diese Störerscheinungen helfen nur verstärkte Abschirmmassnahmen der digitalen Geräte, Filterung aller Eingangsleitungen, Minimalisierung der Bandbreite des Systems, Gleichstromkopplung usw.

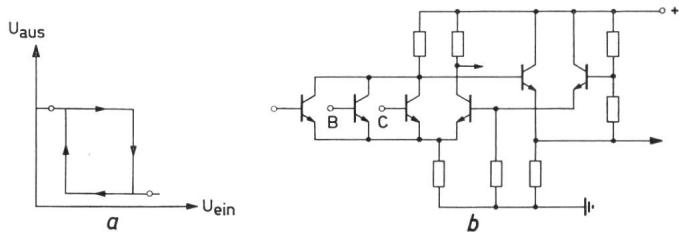

Es sind in der letzten Zeit verschiedene integrierte Schaltungen vorgeschlagen und zum Teil realisiert worden, die sich durch eine erhöhte Störfestigkeit auszeichnen. Die beiden ersten Vorschläge beziehen sich auf Schaltungen hoher Geschwindigkeit, bei denen das Störproblem am meisten Beachtung erfordert. So ist im Falle der emittergekoppelten Logik (im Zusammenhang mit Fig. 14 besprochen) die Einführung einer Hysterese vorgeschlagen worden [9]. Neben dem vergrösserten Störabstand, der nun im Optimalfall gleich dem ganzen logischen Hub sein kann (Fig. 22a), soll diese Schaltung auch weniger schwinganfällig sein als die gewöhnliche ECL-Logik. Die bisher nur als Laboratoriumsmuster gebaute Schaltung zeigt Fig. 22b.

Fig. 22

Emittergekoppelte Schaltung mit Hysterese [9]

a statische Transfercharakteristik; b Schaltung

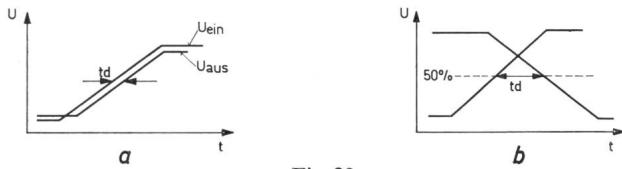

Das wesentliche Geschwindigkeitsmass einer Torschaltung ist die Verzögerungszeit  $t_d$ , mit der es ein nachfolgendes Tor zu schalten vermag, während die Anstiegszeit  $\tau$  eigentlich von sekundärer Bedeutung ist. Da alle «inneren» Übersprechschwierigkeiten in einem Digitalsystem mit abnehmender Anstiegszeit zunehmen, ist es nach [10] das Ziel eines guten Schaltungsentwurfs, das Verhältnis Verzögerungszeit/Anstiegszeit zu minimalisieren. Kleine Verhältniswerte sind aber nur bei nichtinvertierenden Torschaltungen zu erreichen; bei invertierenden Schaltungen sind Anstiegs- und Verzögerungszeit von derselben Grössenordnung. Die in Fig. 23 gezeichneten Tore [10] arbeiten mit relativ flachen Anstiegsflanken; die Empfehlung geht dahin, wo immer möglich die bezüglich Verzögerungszeit schnellen nichtinvertierenden AND-OR-Tore zu verwenden. Mit dieser Methode sollen beträchtliche Einsparungen an teurem Verdrahtungsaufwand möglich sein.

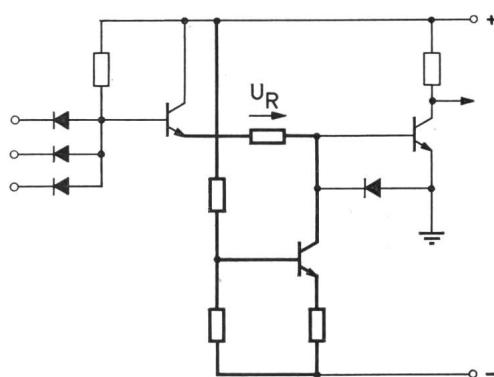

Schliesslich sind auch integrierte Diodenlogik-Systeme mit erhöhter Störfestigkeit entworfen und gebaut worden [11] (Fig. 24). Anstelle der Niveauverschiebungsdioden, die die Störfestigkeit des 0-Niveaus bestimmen, ist hier in die be-

Fig. 23

**Komplementäre Logik**

mit gutem Verhältnis Anstiegszeit/Verzögerungszeit [10]

a UND - ODER-Schaltung; b NOR-Schaltung

$U$  Spannung am Eingang bzw. Ausgang;  $t_d$  Verzögerungszeit

treffende Leitung ein Widerstand eingefügt. Eine spezielle, in der Fig. 24 dick gezeichnete Schaltung schickt einen Strom über diesen Widerstand und erhöht durch den dort hervorgerufenen Spannungsabfall  $U_R$  die statische Störspannungsschwelle. Diese kann mit Hilfe der Speisespannungen verändert werden.

Schliesslich können auch systemtechnische Massnahmen die Störfestigkeit eines digitalen Systems erhöhen, indem die einzelnen Teile (z. B. Zählschaltungen) durch gegenseitige Verkopplung so abgesichert werden, dass die Schädlichkeit von Impulsen, die in das System einlaufen, sehr unwahrscheinlich wird. Ob diese Massnahme, die auf einen erhöhten Schaltungsaufwand zugunsten grösserer Störfestigkeit herausläuft, weitgehende Verbreitung findet, wird die Zukunft zeigen.

**Literatur**

- [1] K. Hübner: Revue et discussion des techniques nouvelles pour l'électronique microminiaturisée. Bull. SEV 55(1964)26, S. 1285...1292.

- [2] H. Hinrichs: Die Planartechnik bei Transistoren und integrierten Schaltungen. Scientia electr. 10(1964)4, S. 97...122.

Fig. 24

Diodenlogik mit einstellbarer Schwellenspannung [11]

$U_R$  zusätzliche Schwellenspannung

- [3] J. W. Lathrop: Semiconductor Network Technology 1964. Proc. IEEE 52(1964)12, S. 1430...1444.

- [4] R. M. Warner, J. N. Fordemwalt and C. S. Meyer: Integrated Circuits, Design Principles and Fabrication. McGraw-Hill New York 1965.

- [5] W. W. Gärtner: Nanowatt Devices. Proc. IEEE 53(1965)6, S. 592...604.

- [6] R. Landauer: Irreversibility and Heat Generation in the Computing Process, IBM J. Res. Developm. 5(1961)3, S. 183...191.

- [7] R. W. Keyes: On Power Dissipation in Semi-Conductor Computing Elements. Proc. IRE 50(1962)12, S. 2485.

- [8] R. W. Ahrons and M. M. Mitchell: MOS Micropower Complementary Transistor Logic. 1965 International Solid-State Circuits Conference, Digest of Technical Papers, Lewis Winner, Publisher, New York 1965, S. 80...81.

- [9] B. T. Murphy, H. A. Waggener and J. E. Iwersen: Nonsaturating Monolytic Logic Circuits with Improved Stability. 1965 International Solid-State Circuits Conference, Digest of Technical Papers, Lewis Winner, Publisher, New York 1965, S. 8...9.

- [10] R. B. Seeds, W. R. Smith and R. D. Nevala: Integrated Complementary Nanosecond Logic. Proc. IEEE 52(1964)12, S. 1584...1590.

- [11] W. C. Seelbach, R. A. Gissel and P. B. Foster: Variable Threshold Logic Family. 1965 International Solid-State Circuits Conference, Digest of Technical Papers, Lewis Winner, Publisher, New York 1965, S. 40...41.

- [12] J. D. Meindl, L. F. Wagner, O. Pitzalis and R. Gilson: Static and Dynamic Performance of Micropower Transistor Logic Circuits. Proc. IEEE 52(1964)12, S. 1575...1583.

- [13] D. A. Maxwell, R. H. Beeson and D. F. Allison: The Minimization of Parasitics in Integrated Circuits by Dielectric Isolation. Trans. IEEE Electron Devices ED-12(1965)1, S. 20...25.

**Adresse des Autors:**

Dr. W. Guggenbühl, Privatdozent ETH, Contraves AG, 8052 Zürich.

## Einfluss der statischen Elektrizität auf Sicherheit und Wirtschaftlichkeit im Betrieb

Von H. Haase, Hamburg

537.2 : 658.382.3

Statische Elektrizität beeinflusst als Begleiterscheinung technischer Vorgänge in zunehmendem Masse Wirtschaftlichkeit und Sicherheit im Betrieb. Nach Beschreibung der möglichen Auswirkungen werden die physikalischen Voraussetzungen für das Zustandekommen von Aufladungen diskutiert. Es folgen die Schilderung der typischen Merkmale elektrostatischer Vorgänge und der Nachweis- und Messmethoden. Dann werden die Bekämpfungsmethoden angegeben und schliesslich die Beurteilungsgrundlagen für statische Elektrizität als Störung und Gefahr behandelt.

La production d'électricité statique accompagnant certains processus techniques influence dans une mesure croissante le rendement et la sécurité des exploitations. Après en avoir décrit les conséquences possibles, l'auteur traite des conditions physiques de l'apparition de charges statiques. Puis il décrit les indices révélateurs de phénomènes électrostatiques, ainsi que les méthodes de détection et de mesure. Il indique ensuite les moyens de combattre ces phénomènes. Pour terminer, il examine selon quelles bases d'appréciation les dérangements et les dangers dus à l'électricité statique doivent être jugés.

### 1. Einleitung

Das lebhafte Interesse, welches der statischen Elektrizität in jüngster Zeit wieder entgegengebracht wird, hängt eng mit dem jetzigen Stand der Technik zusammen. So treten bei der Herstellung, Verarbeitung und Verwendung neuer Stoffe und bei hohen Geschwindigkeiten zahlreicher Vor-

gänge Erscheinungen auf, welche zuerst Gilbert um 1600 als «elektrisch» bezeichnet hatte und deren Erforschung im 18. Jahrhundert intensiv betrieben wurde.

Das mehr spielerische Interesse der damaligen Zeit an den merkwürdigen Phänomenen der Elektrostatik schwand in dem Masse, wie es gelang, die Elektrochemie und vor