**Zeitschrift:** Bulletin des Schweizerischen Elektrotechnischen Vereins

**Herausgeber:** Schweizerischer Elektrotechnischer Verein ; Verband Schweizerischer Elektrizitätswerke

**Band:** 56 (1965)

**Heft:** 25

**Artikel:** Eigenschaften und Anwendungen der neuen Feldeffekttransistoren

**Autor:** Strutt, M.J.O.

**DOI:** <https://doi.org/10.5169/seals-916432>

### Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. [Mehr erfahren](#)

### Conditions d'utilisation

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. [En savoir plus](#)

### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. [Find out more](#)

**Download PDF:** 22.02.2026

**ETH-Bibliothek Zürich, E-Periodica, <https://www.e-periodica.ch>**

# BULLETIN

DES SCHWEIZERISCHEN ELEKTROTECHNISCHEN VEREINS

Gemeinsames Publikationsorgan des Schweizerischen Elektrotechnischen Vereins (SEV)

und des Verbandes Schweizerischer Elektrizitätswerke (VSE)

## Eigenschaften und Anwendungen der neuen Feldeffekttransistoren<sup>1)</sup>

Von M. J. O. Strutt, Zürich

621.382.323

### 1. Haupttypen von Feldeffekttransistoren

Heute sind Feldeffekttransistoren (FET) technisch so wichtig geworden, dass es in den USA keinen einzigen Transistorhersteller gibt, der nicht grosszügige Forschungs- und Entwicklungsarbeiten auf diesem Gebiet durchführt. Zweifellos werden die Feldeffekttransistoren in absehbarer Zeit für viele Zwecke die älteren Transistor-Typen (kurz Bipolartransistoren genannt) verdrängen.

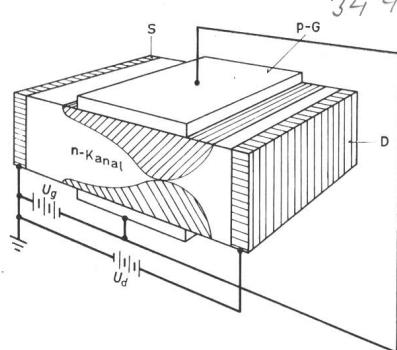

Der erste Typ der FET ist bereits 1952 von W. Shockley [1; 2]<sup>2)</sup> vorgeschlagen worden. Wir werden ihn den «junction»-Typ nennen. Es ist interessant, dass ein entsprechendes Baulement bereits 1935 von O. Heil in einer Britischen Patentschrift (439457) beschrieben wurde. Die wesentliche Konstruktion geht aus Fig. 1 hervor. Wie bei allen FET sind die Elektroden mit S (source), G (gate) und D (drain) bezeichnet worden. In der Bundesrepublik Deutschland sind hiefür die Namen «Quelle» (source), «Senke» (drain) und «Gitter» (gate) vorgeschlagen worden. Wir werden aber, wie auch für

Fig. 1

Schematische Konstruktion eines junction gate type-FET

D drain; p-G p-gate; S source

$U_d$  Spannung zwischen D und S;  $U_g$  Spannung zwischen G und S

Bipolartransistoren üblich, die US-Bezeichnungen benutzen. Der Strom von S nach D beruht auf dem Vorhandensein von Majoritätsträgern im zwischenliegenden (hier n) Kanal. Wenn die Spannung von G gegen S negativ wird, dehnt sich die Sperrschicht zwischen den p-Elektroden und dem n-Kanal immer weiter in letzteren hinein aus. In dieser Sperrschicht sind relativ sehr wenig Majoritätsträger vorhanden, d. h. der Widerstand zwischen S und D nimmt zu, wodurch der Strom bedeutend weniger stark mit der Spannung von D gegen S zunimmt. Die Kennlinien eines handelsüblichen junction-FET zeigt Fig. 2.

<sup>1)</sup> Vortrag, gehalten an der Elektronik-Tagung der «fera 1965» vom 27. August 1965 in Zürich.

<sup>2)</sup> Siehe Literatur am Schluss des Aufsatzes.

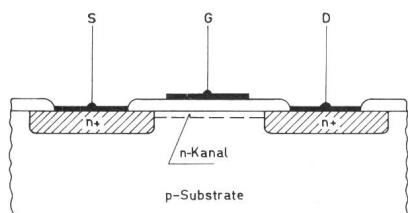

Der zweite Typ der FET unterscheidet sich vom ersten dadurch, dass G gegen den Stromkanal von S nach D isoliert ist. Daher nennt man diesen den «insulated gate»-Typ [3...7]. Er ist viel neueren Datums und wird erst seit wenigen Jahren gebaut. Die grundsätzliche Konstruktion eines «depletion»-Typs (vgl. unten) geht aus Fig. 3 hervor. Wie ersichtlich, findet die Stromleitung zwischen S und D hier durch *Majoritätsträger* in einem n-Kanal statt. Unterhalb dieses n-Kanals befindet sich eine p-Unterlage (substrate). Meistens wird die substrate-Elektrode mit S verbunden. Zwischen G und dem n-Kanal befindet sich eine isolierende Schicht. Wenn G gegen S negativ gemacht wird, so werden die Majoritätsträger aus dem n-Kanal in die p-Schicht abgedrängt und der n-Kanal erhält einen höheren Widerstand. Die Kennlinien eines experimentellen insulated gate depletion-Typs zeigt Fig. 4. Sie sind einigermassen analog zu denen in Fig. 2.

Es drängt sich die Frage auf, weshalb die FET erst jetzt zur Blüte gelangt sind, nachdem wenigstens der junction-Typ bereits so lange bekannt war. Erstens wird durch das bessere Verständnis und durch die fortgeschrittene Technologie der Halbleiter jetzt im Vergleich zu früher eine viel bessere Herstellung der FET ermöglicht. Zweitens sind durch neue technologische Verfahren, wie die Aufdampftechnik im Hochvakuum (besser als  $10^{-7}$  bis  $10^{-8}$  Torr) und durch die Epitaxialtechnik Herstellungsmethoden ermöglicht worden, die es vor 13 Jahren gar nicht gab. Drittens schreitet die Transistorisierung von Schaltkreisen, die früher mit Elektronenröhren betrieben wurden, immer weiter fort (z. B. Fernsehempfänger, Computers). Hiebei tritt der grosse Vorteil der FET gegenüber den Bipolartransistoren zutage, dass jene eine viel höhere Eingangsimpedanz aufweisen (etwa  $10^3$  bis  $10^6$  mal mehr). Dadurch lassen sich die FET wie Elektronenröhren einsetzen, und die Transistorisierung bekannter Schaltungen wird in viel einfacherer Weise ermöglicht. Diese Faktoren haben zu einer wahren Hochblüte der FET geführt.

### 2. Feldeffekttransistor des junction-Typs

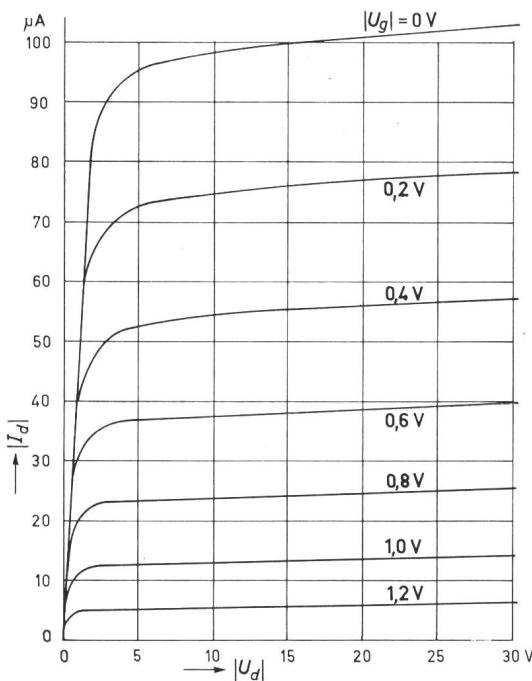

Zunächst soll der allgemeine Verlauf der  $I_d - U_d$ -Kennlinien mit  $U_g$  als Parameter, wie er aus Fig. 2 hervorgeht, an Hand der Konstruktion qualitativ gedeutet werden. Hiezu ist es nützlich, einige Eigenschaften der Leitfähigkeit von Halbleitern für Majoritätsträger als Funktion der elektrischen Feldstärke zu betrachten [8]. Die vorhandenen elektrischen Feldstärken müssen mit einer «kritischen» Feldstärke verglichen werden, welche eng mit der unregelmässigen thermischen Bewegung der Ladungsträger zusammenhängt. Bei einer absolu-

Fig. 2

Kennlinien eines Feldeffektortransistor (FET) nach Fig. 1

$|I_d|$  Strom nach Fig. 7;  $|U_d|$  Spannung nach Fig. 7;

$|U_g|$  Spannung nach Fig. 7

ten Temperatur  $T$  ist der quadratische Mittelwert der thermischen Trägergeschwindigkeit gegeben durch:

$$\overline{v_{th}^2} = \frac{3 k T}{m}$$

wo  $k$  die Boltzmannsche Konstante und  $m$  die effektive Masse der betreffenden Ladungsträger im Halbleiter sind. Die Zunahme der Trägergeschwindigkeit (Driftgeschwindigkeit):  $\Delta v_x$  infolge einer kleinen elektrischen Feldstärke  $E_x$  in der  $x$ -Richtung beträgt:

$$|\Delta v_x| = b_{no} E_x$$

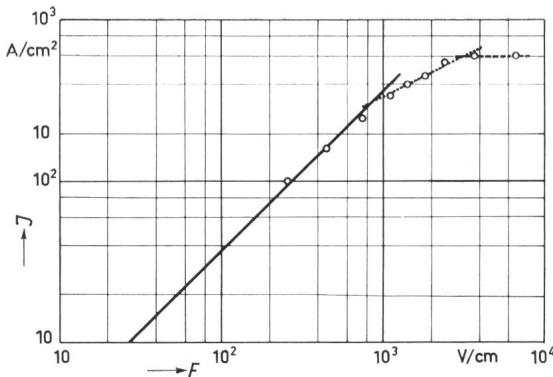

wobei  $b_{no}$  die Trägerbeweglichkeit der kleinen Feldstärken ist. Sobald  $|\Delta v_x|$  ungefähr gleich oder grösser als  $\sqrt{\overline{v_{th}^2}}$  wird, hat die elektrische Feldstärke praktisch keinen Einfluss mehr auf die Geschwindigkeit der Träger. Diese wird daher unabhängig von der Feldstärke; das gleiche gilt von der Stromdichte (Fig. 5). Die kritische Feldstärke ist angenähert gegeben durch:

$$E_{krit.} = \frac{1}{b_{no}} \sqrt{\frac{3 k T}{m}}$$

Wenn die Feldstärke klein gegen diesen Wert ist, wird die Stromdichte proportional zur Feldstärke. Ist die Feldstärke vergleichbar mit  $E_{krit.}$  oder grösser, so wird die Stromdichte

Fig. 3

Schematische Konstruktion eines FET vom insulated gate type (depletion type)

S source; G gate; D drain

feldstärkeunabhängig (Fig. 5) und damit die differentielle Leitfähigkeit sehr gering.

Auf Grund dieser Eigenschaften ist es möglich, die Kennlinien der Fig. 2 qualitativ zu deuten. Im linken Teil dieser Kennlinien ist  $|I_d|$  ungefähr proportional  $|U_d|$ . Hier sind die Feldstärken klein gegen die kritische Feldstärke und deshalb gilt hier das Ohmsche Gesetz angenähert. Dies ist gut aus den Kennlinien in Fig. 6 zu ersehen. Bei grösseren Werten von  $|U_g|$  ist die Neigung der erwähnten Geraden geringer, da der Widerstand des Trägerkanals zwischen  $S$  und  $D$  wächst (Fig. 6). Der Übergang vom geneigten in den horizontalen Teil der Kennlinien hängt nicht bei allen junction-FET-Konstruktionen unmittelbar mit dem Auftreten der kritischen Feldstärke zusammen. Dies kann vielmehr vorwiegend bei kurzen Kanälen der Fall sein. Sobald ein Teil des Kanals blockiert, d. h. trägerfrei wird, hat dieser Teil einen sehr hohen Widerstand. Der Elektronenstrom fliesst im nicht blockierten Teil infolge der positiven Spannung zwischen der Grenze des blockierten n-Kanalabschnittes und  $S$ . Dieser Strom fliesst aus Kontinuitätsgründen durch den blockierten Teil weiter (injizierter Strom) und ist nun unabhängig von  $U_d$  und nur abhängig von  $U_g$ . Letztere Spannung bestimmt hier den Strom, welcher von  $S$  aus in den Kanal hineinfliest. Dieser Mechanismus bestimmt in weitaus den meisten Fällen den fast horizontalen Abschnitt der Kennlinien [9].

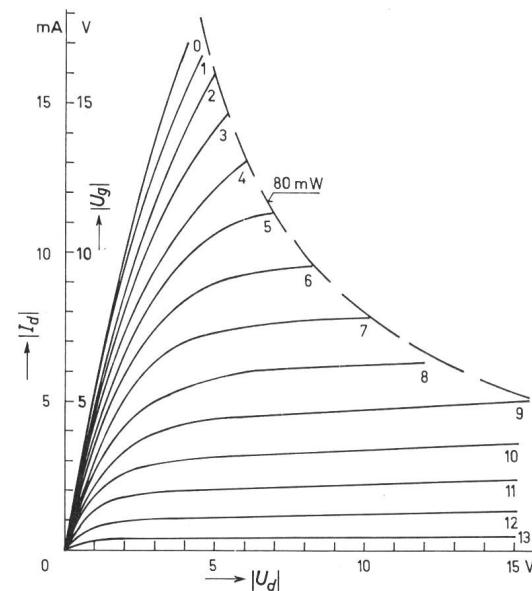

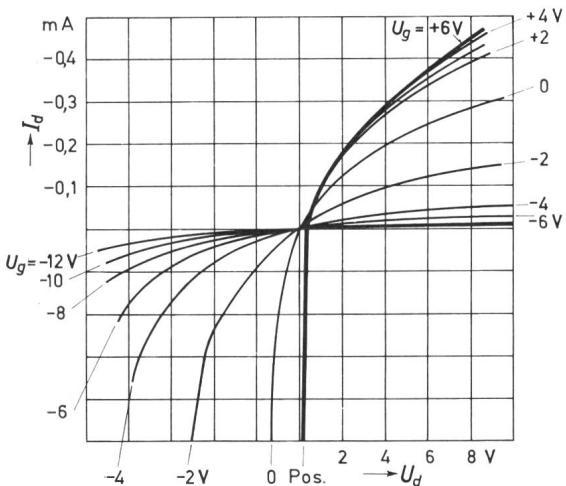

Fig. 4

Kennlinien eines FET nach Fig. 3

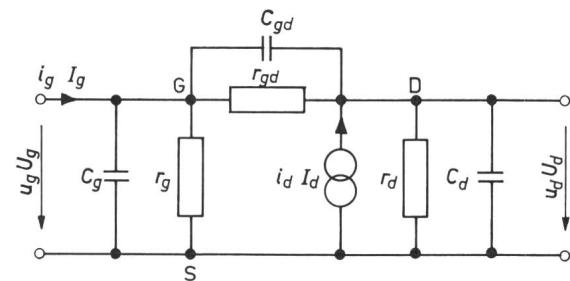

Nachdem in dieser Weise der allgemeine Verlauf des Kennlinienbildes gedeutet worden ist, kommen wir zum Klein-signal-Ersatzschaltbild. Wenn der FET im Bereich der angehährt horizontalen Abschnitte des Kennlinienbildes betrieben wird, können diese Kennlinien im wesentlichen mit denen einer Pentode verglichen werden. In einem Vierpol, wobei  $S$  die gemeinsame Elektrode von Eingang und Ausgang ist, sind in Fig. 7 die positiv gezählten Strom- und Spannungsrichtungen eingezeichnet worden. Im Falle, dass ein n-Kanal vorliegt, ist  $U_d$  positiv und  $I_d$  negativ. Die gleichen Zeichen gelten für  $u_d$  und  $i_d$  (d. h. für kleine Änderungen von  $U_d$  und  $I_d$ ). Hierbei ist  $U_g$  negativ und  $u_g$  positiv. Im Falle eines p-Kanals kehren alle diese Vorzeichen, ausser von  $u_g$ , um. Die

Fig. 5

Stromdichte als Funktion der Feldstärke bei Germanium [8]

$E$  Feldstärke;  $J$  Stromdichte

Stromquelle  $i_d$  wird durch  $u_g$  gesteuert, und in erster Näherung können wir setzen:

$$i_d = \alpha u_g$$

so dass eine proportionale Steuerung vorliegt. Zwischen jeder der Elektroden  $S$ ,  $G$  und  $D$  und den beiden anderen Elektroden ist ein Widerstand parallel zu einer Kapazität vorhanden [10], (Fig. 7). Der Widerstand  $r_d$  entspricht dem Widerstand des Kanals zwischen  $S$  und  $D$ , und  $C_d$  ist die Kapazität zwischen  $S$  und  $D$ . Der Widerstand  $r_g$  ist offenbar durch die Neigung der Kennlinien im rechten Teil der Fig. 2 bestimmt und dementsprechend gross (mehrere  $M\Omega$  bei Si). Der Wert von  $C_d$  beträgt meistens etwa 1 pF. Der Widerstand  $r_{gd}$  zwischen  $G$  und  $D$  ist im Arbeitsbereich (p-n-Übergang gesperrt) ebenfalls sehr gross (z. B. einige  $10^3 M\Omega$  bei Si) und  $C_{gd}$  hat eine analoge Größenordnung wie  $C_d$ . Der Widerstand  $r_g$  ist meistens etwas kleiner als  $r_{gd}$  aber doch sehr gross (z. B. einige  $10^2 M\Omega$  bei Si), während  $C_g$  eine analoge Größenordnung hat wie  $C_d$  und  $C_{gd}$  (Datenblatt Siliconix). Offenbar können die Größen des Schaltschemas in Fig. 7 in einfacher Weise bestimmt werden, wenn erstens  $D$  und  $S$  kurzgeschlossen werden und zwischen  $G$  und  $S$  gemessen, nachher  $G$  und  $S$  kurzgeschlossen und zwischen  $D$  und  $S$  gemessen, schliesslich  $G$  und  $D$  kurzgeschlossen und zwischen  $D$  und  $S$  gemessen. Bei diesen Messungen ist  $u_g = 0$ . Die Grösse von  $\alpha$  kann

Fig. 6

Kennlinien eines junction gate type-FET im Bereich kleiner Ströme  $I_d$  und Spannungen  $U_d$  und  $U_g$  als Parameter

Es handelt sich um einen n-Kanal

bestimmt werden, indem  $D$  und  $S$  kurzgeschlossen werden und  $i_d$  bei bestimmtem  $u_g$  gemessen wird.

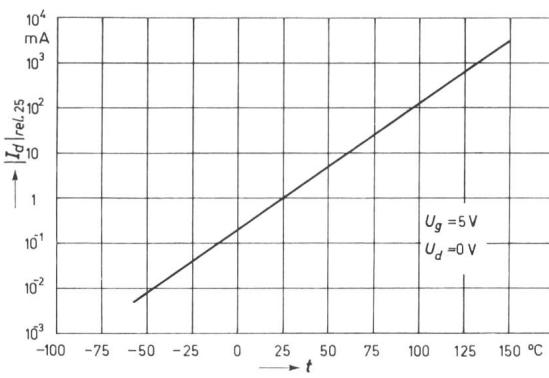

Wenn  $|U_d|$  immer weiter gesteigert wird, tritt schliesslich zwischen  $D$  und  $S$  ein Durchschlag auf. Diese Durchschlagsspannung beträgt z. B. bei dem FET Siliconix 2 N 2606 etwa -32 V (p-Kanal). Die Kenndaten sind temperaturabhängig wie dies z. B. für den erwähnten FET aus Fig. 8 hervorgeht. (Datenblatt Siliconix).

### 3. Feldeffekttransistor des insulated gate-Typs

Der Hauptunterschied gegenüber dem junction-Typ besteht darin, dass die Elektrode  $G$  isoliert ist und somit, abgesehen von Leckströmen, praktisch gar keinen Gleichstrom führen kann. Es sind mehrere Konstruktionen von insulated gate-FET bekannt geworden. Die zwei wichtigsten unterscheiden sich wie folgt:

Bei der ersten Konstruktion (enhancement type) ist für  $U_g = 0$  der Strom  $I_d$  auch Null, und nimmt dann bei richtiger Polung und im Betrag steigenden Werten von  $|U_g|$  zu. Bei dieser Konstruktion hat der Kanal zunächst einen hohen Widerstand, während bei richtig angelegter Spannung  $U_g$  an der Oberfläche des Kanals, durch herangezogene freie Ladungsträger eine zusätzliche Leitfähigkeit geschaffen wird.

Fig. 7

Kleinsignal-Ersatzschaltbild eines junction gate type-FET

Der Quellenstrom  $i_d$  ist durch  $\alpha u_g$  gegeben

$i_d$  kleine Änderung von  $I_d$ ;  $I_d$  Quellenstrom von S nach D;  $i_g$  kleine Änderung von  $I_g$ ;  $I_g$  Eingangsstrom von G;  $u_d$  kleine Änderung von  $U_d$ ;  $U_d$  Spannung von D nach S;  $u_g$  kleine Änderung von  $U_g$ ;  $U_g$  Spannung von G nach S;  $C_d$  Kapazität D-S;  $C_g$  Kapazität G-S;  $C_{gd}$  Kapazität G-D;  $r_d$  Widerstand D-S;  $r_g$  Widerstand G-S;  $r_{gd}$  Widerstand G-D

Bei der zweiten Konstruktion, welche hier ausführlicher behandelt werden soll, hat der Kanal zunächst einen geringen Widerstand. Bei richtig angelegter Spannung  $U_g$  nimmt dann der Widerstand des Kanals beträchtlich zu (depletion type). Diese Konstruktion zeigt Fig. 3 und das entsprechende Kennlinienfeld Fig. 4 (experimenteller Typ aus einer Promotionsarbeit des Instituts für höhere Elektrotechnik der ETH). Aus Fig. 3 geht hervor, dass ein n-Kanal zwischen S und D vorhanden ist. Wenn nun G eine negative und D eine positive Spannung in Bezug auf S erhält, so wird an der Unterseite der Isolationsschicht eine positive Ladung entstehen. Dies geschieht dadurch, dass hier die freien Ladungsträger (Elektronen) des n-Kanals verdrängt werden. Es bleiben dann die ionisierten Donoratome übrig, welche positiv geladen sind. Beim n-p-Übergang zwischen dem n-Kanal und dem p-Substrat entsteht eine Sperrschiicht, welche im n-Kanal eine positive, und im p-Substrat eine negative Ladung infolge der ionisierten negativ geladenen Akzeptoratome aufweist. Durch den von freien Ladungsträgern mehr oder weniger entblößten Teil des n-Kanals wird der Widerstand dieses Kanals,

bei im Beitrag steigender negativer Spannung von  $G$  gegen  $S$  zwischen  $S$  und  $D$  vergrößert. Dies zeigt der linke Teil der Kennlinien in Fig. 4. Sobald ein Teil des n-Kanals gar keine freien Elektronen mehr enthält, wird der Elektronenstrom, welcher  $S$  verlässt, nur noch von der Spannung zwischen  $S$  und dem Rand des positiv geladenen Kanalteils, d. h. durch die Spannung von  $G$  gegen  $S$  und nicht mehr durch  $U_d$  bestimmt. Der Strom wird nahezu unabhängig von  $U_d$ . Der Elektronenstrom geht durch die entstandene Sperrsicht im n-Kanal hindurch nach  $D$  (injizierter Strom). Somit ist der rechte

Fig. 8

**Strom  $|I_d|$  eines junction gate type-FET als Funktion der Temperatur bei festen Spannungen (Siliconix-Datenblatt)**

$|I_d|_{rel. 25} = |I_d|$  relativ zum Wert bei  $25^\circ\text{C}$ ;  $t$  Umgebungstemperatur

nahezu horizontale Teil des Kennlinienfeldes in Fig. 4 deutet.

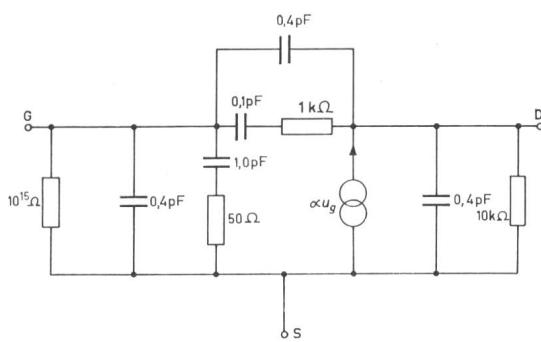

Die gesamte Wirkungsweise dieses insulated gate-FET gleicht etwas jener der junction-FET. Der Unterschied besteht hauptsächlich darin, dass  $G$  gegen  $S$  und  $D$  isoliert ist. Der Widerstand zwischen  $G$  und  $S$  kann z. B. bei Siliziumtypen  $10^{15} \Omega$  betragen. Das Kleinsignal-Ersatzschaltbild in Fig. 7 kann im vorliegenden Fall mit relativ geringen Änderungen benutzt werden. Ein Beispiel [3] des Kleinsignal-Schaltbildes eines insulated gate-FET zeigt Fig. 9 (depletion type) [11;12].

#### 4. Weitere Eigenschaften von Feldeffekttransistoren

Ausser den erwähnten Kenndaten und Eigenschaften ist noch eine Reihe weiterer Eigenschaften bei der Anwendung der FET in elektronischen Schaltungen wichtig.

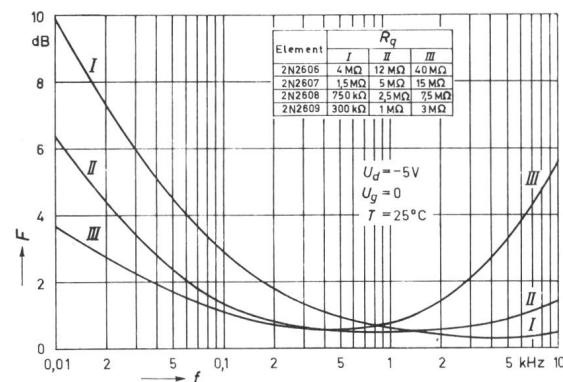

In erster Linie muss für FET in Anfangsverstärkerstufen das Rauschen berücksichtigt werden [13...16]. Bei dem hohen Eingangswiderstand der FET kann bei nicht zu hohen Frequenzen das Rauschen, analog wie bei Trioden und Pentoden, am besten durch den aequivalenten Rauschwiderstand am

Fig. 9

**Kleinsignal-Ersatzschaltbild eines insulated gate type-FET (depletion type)**

Eingang charakterisiert werden [3]. Dieser Rauschwiderstand ist durch die Formel:

$$R_{aeg.} = \frac{0,5}{\alpha} \quad [\Omega]$$

gegeben, wo  $\alpha$  die Steilheit des FET (vgl. Fig. 7, wo  $i_d = \alpha u_g$  ist) bedeutet. Beim junction-FET 2 N 2609 (Siliconix) ist  $\alpha = 3,6 \text{ m mho}$  und somit  $R_{aeg.}$  etwa  $140 \Omega$ . Die Rauschzahl wird:

$$F = 1 + \frac{R_{aeg.}}{R_q}$$

wo  $R_q$  den Quellenwiderstand bedeutet. Bei Anpassung der Quelle an den Eingang des FET ist  $R_q$  sehr gross und somit die Rauschzahl sehr klein. Dies geht für einige junction-FET (Datenblatt Siliconix) aus Fig. 10 hervor. Diese geringen Rauschzahlen  $F$  im Vergleich mit Bipolartransistoren bilden einen grossen Vorteil der FET bei Anwendungen in Anfangsstufenverstärkern.

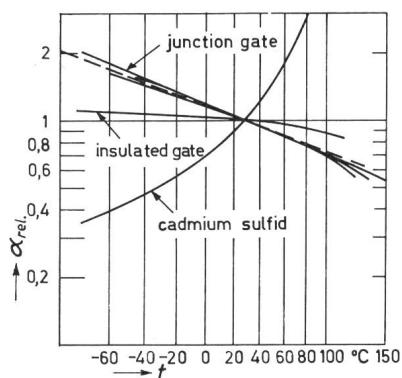

Die Temperaturabhängigkeit der Kenndaten wurde bereits durch Fig. 8 illustriert. In Fig. 11 wird die Temperaturabhängigkeit von  $\alpha$  für einige FET gezeigt [3]. Es ist möglich, diese Temperaturabhängigkeit durch die Konstruktion und durch die gewählten Werkstoffe zu beeinflussen.

Die obere Frequenzgrenze vom FET ist bestimmt durch die verwendbare Drainspannung  $U_d$ . Je höher diese ist, umso kürzer ist die Trägerlaufzeit im S-D-Kanal. Das gilt aber nur in jenem Bereich, wo das Ohmsche Gesetz noch Gültigkeit hat (vgl. Fig. 5). Bei hohen  $U_d$ -Werten wird die Stromdichte unabhängig von  $U_d$  und somit die Beweglichkeit sehr gering.

Fig. 10

**Rauschzahl eines junction gate type-FET als Funktion der Frequenz für verschiedene Elemente und verschiedene Quellenwiderstände  $R_q$**

(Datenblatt Siliconex)

$F$  Zusatzrauschzahl (= Rauschzahl - 1);  $f$  Frequenz;  $R_q$  Quellenwiderstand

Letzten Endes wird die obere Frequenzgrenze durch die dielektrische Relaxationszeit des Kanalmaterials bestimmt [3], und zwar gilt dies sowohl für Feldeffekt- als auch für Bipolartransistoren. Durch parasitäre Reaktanzen wird diese obere Frequenzgrenze in den meisten Fällen stark herabgesetzt. Für den FET kann das gain-Bandbreite-Produkt  $GB$  durch die Formel:

$$GB = \frac{\alpha}{2 \pi C_{gt}}$$

ausgedrückt werden [3]. Hier bedeuten  $\alpha$  die Steilheit und  $C_{gt}$  die Gesamtkapazität von  $G$  gegenüber  $S - D$ . In günstigen Fällen werden Werte zwischen  $10^7$  und  $10^8$  erreicht. Die entsprechenden Werte der heutigen besten Bipolartransistoren sind bedeutend höher.

In Bezug auf Schalteigenschaften kann bemerkt werden, dass es sich bei den FET um Majoritätsträgertransport handelt. Hierdurch treten keine Diffusionskapazitäten wie bei Bipolartransistoren auf, welche mit Minoritätsträgertransport arbeiten. Die Schaltzeit von FET ist ausschließlich durch die

Fig. 11

Der Wert  $\alpha$  (vgl. Schaltschemata von Fig. 7 und 9) als Funktion der Temperatur für verschiedene FET-Typen

$RC$ -Zeit bestimmt [3]. Dies ist die Ladungszeit der Kapazität  $C_g$  (Fig. 7 und 9), die benötigt wird um diese durch den Widerstand  $R$  des Kanals aufzuladen. Mit einer Quelle, welche einen niedrigen Quellenwiderstand hat, können Schaltzeiten bis zu  $10^{-9}$  s mit FET erzielt werden. Wenn am Eingang wieder ein FET verwendet wird, entstehen Schaltzeiten in der Größenordnung von  $10^{-8}$  s.

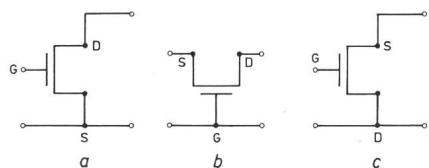

Fig. 12

**Drei verschiedene Schaltungsarten eines FET in einem Vierpol**

Für bestimmte Anwendungen, z. B. in Satelliten, ist es notwendig, dass die Eigenschaften eines Transistors relativ wenig durch radioaktive Strahlung ( $\alpha$ -Teilchen, Neutronen,  $\gamma$ -Strahlung) beeinflusst werden. Bei Bipolartransistoren wird die Lebensdauer der Träger durch Bestrahlung herabgesetzt, wodurch die Parameter ungünstig beeinflusst werden. Bei FET tritt erst eine beträchtliche Beeinflussung durch Strahlung auf, wenn die Dotierung der Werkstoffe geändert wird. Dies liegt wieder daran, dass die FET mit Majoritätsträgertransport

Fig. 13

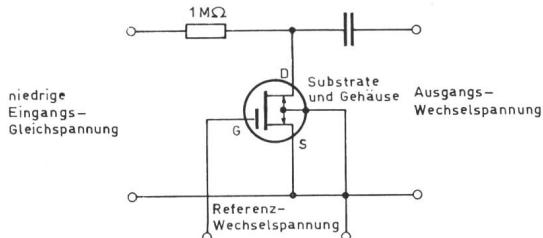

Fig. 15

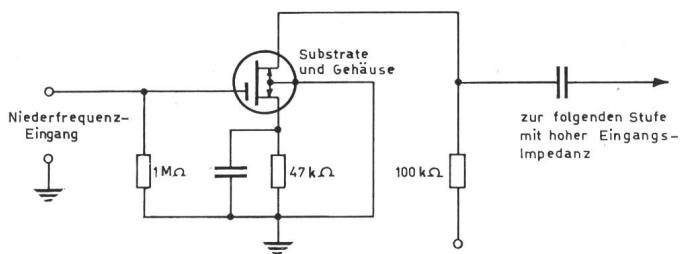

**Anfangsstufenverstärker für den akustischen Frequenzbereich mit einem insulated gate-FET**

(Datenblatt RCA)

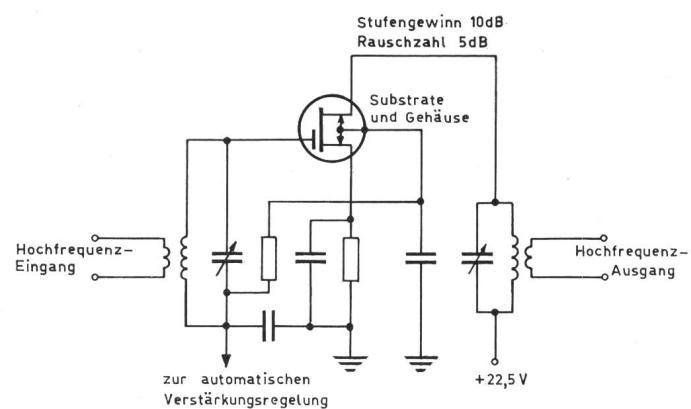

**Fig. 14**

**Abgestimmter Anfangsstufenverstärker für etwa 60 MHz mit einem

insulated gate-FET**

(Datenblatt RCA)

arbeiten. Diese Dotierungsänderung tritt erst bei etwa der zehnfachen Strahlungsdosis auf, welche eine Lebensdaueränderung der Minoritätsträger bewirkt (bei Bipolartransistoren). Daher sind FET etwa zehnmal Strahlungsunempfindlicher als Bipolartransistoren vergleichbarer Abmessungen [3].

Die Eigenschaft der FET, dass in ihnen Majoritätsträgertransport verwendet wird, hat noch eine weitere wichtige Folge. Eine ganze Reihe von Halbleiterwerkstoffen wird dadurch für FET anwendbar, die aber für Bipolartransistoren ungeeignet sind. Die Kriterien für die Anwendbarkeit verschiedener Werkstoffe für FET bestehen darin, dass geeignetes p- bzw. n-Material hergestellt wird, welches in einem Kanal vom gate-Material und vom substrate-Material genügend getrennt werden kann. Die Leitfähigkeit des Kanals muss bei junction-Typen und bei insulated gate depletion-Typen genügend hoch und bei insulated gate enhancement-Typen genügend niedrig sein. Es ist verhältnismässig leicht, FET für Spezialzwecke zu konstruieren, wobei viele Elektrodenformen und Dotierungsprofile angewandt wurden. Bei Bipolartransi-

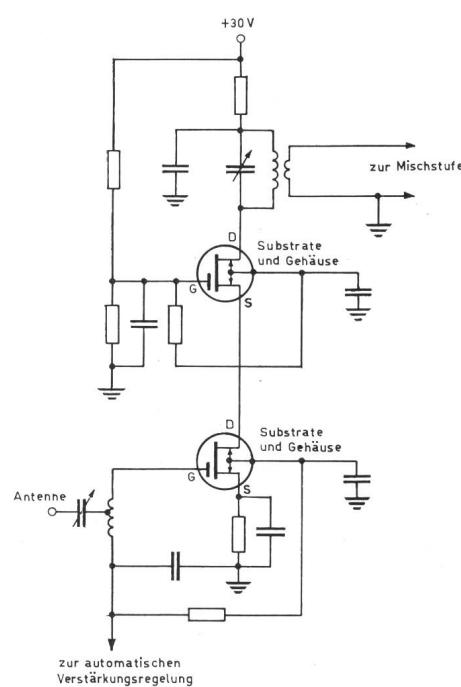

Fig. 15

**Cascode-Anfangsstufen-Hochfrequenzverstärker mit zwei insulated gate-FET**

(Datenblatt RCA)

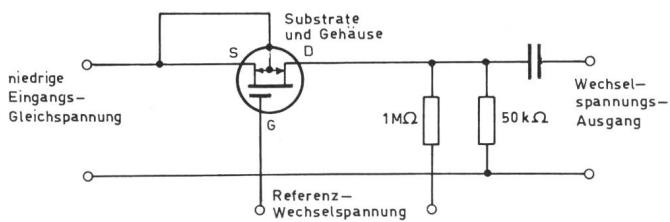

Fig. 16

Reihen-chopper-Kreis mit einem insulated gate-FET

(Datenblatt RCA)

storen ist die Konstruktion meistens schwieriger durchführbar. Besonders für integrated circuits vom monolithischen Typ können FET in einfacher Weise mittels Masken- und Aufdampfverfahren erzeugt werden.

## 5. Anwendungen

Da ein FET ein Dreielektroden-Bauelement ist, kann er auf drei verschiedene Arten in einen Vierpol eingebaut werden, je nachdem eine der Elektroden S, G oder D als gemeinsame Elektrode des Ein- und Ausganges dient (Fig. 12).

Wie bereits erwähnt, können die FET fast unmittelbar Trioden und Pentoden in elektronischen Schaltungen ersetzen. Als erstes Beispiel sei ein Anfangsstufenverstärker für den

Fig. 17

Parallel-chopper-Kreis mit einem insulated gate-FET

(Datenblatt RCA)

akustischen Frequenzbereich erwähnt (Fig. 13). Einen abgestimmten Hochfrequenz-Anfangsstufenverstärker zeigt Fig. 14. Auch in Fig. 15 ist ein Hochfrequenz-Anfangsstufenverstärker gezeigt, aber diesmal in Cascode-Schaltung. Zwei chopper-Kreise zeigen Fig. 16 und Fig. 17 (die Fig. 13...17 wurden einem RCA Datenblatt entnommen). Schliesslich zeigt Fig. 18 einen bistabilen Kreis, der keinen Strom verbraucht, ausser wenn geschaltet wird.

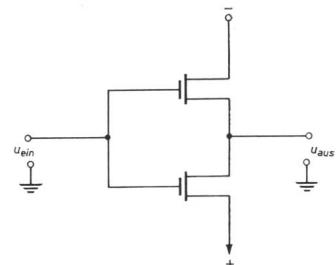

Fig. 18

Bistabiler Kreis mit zwei insulated gate-FET, der nur dann Strom verbraucht, wenn geschaltet wird [3]

In integrated circuits vom monolithischen Typ werden heute fast ausschliesslich FET verwendet, weil sie sich beim Fabrikationsprozess in einfacher Weise in die Schaltungen einfügen lassen.

## Literatur

- [1] W. Shockley: A Unipolar Field-Effect Transistor. Proc. IRE 40(1952)11, S. 1365...1376.

- [2] G. C. Dacey and J. M. Ross: The Field Effect Transistor. Bell Syst. techn. J. 34(1955)6, S. 1149...1189.

- [3] J. T. Wallmark: The Field-Effect Transistor — an old Device with new Promise. IEEE Spectrum 1(1964)3, S. 182...191.

- [4] P. K. Weimer: The TFT — A new Thin-Film Transistor. Proc. IRE 50(1962)6, S. 1462...1469.

- [5] G. C. Onodera, W. J. Corrigan and R. M. Warner: Silicon Field-Effect Transistor with Internal Epitaxial Channel. Proc. IRE 50(1962)8, S. 1824.

- [6] H. Borkan and P. K. Weimer: An Analysis of the Characteristics of Insulated-Gate Thin-Film Transistors. RCA Rev. 24(1963)2, S. 153...165.

- [7] S. R. Hofstein and F. P. Heiman: The Silicon Insulated-Gate Field-Effect Transistor. Proc. IEEE 51(1963)9, S. 1190...1202.

- [8] W. Guggenbühl, M. J. O. Strutt und W. Wunderlin: Halbleiterbauelemente. Bd. I: Halbleiter und Halbleiterdioden. Birkhäuser Basel 1962.

- [9] R. S. C. Cobbold and F. N. Trofimienoff: Theory and Application of the Field-Effect Transistor. Part I: Theory and d.c. Characteristics. Proc. IEE 111(1964)12, S. 1981...1992.

- [10] F. N. Trofimienoff, R. D. Silverthorn and R. S. C. Cobbold: Theory and Application of the Field-Effect Transistor. Part 2: High-Frequency Properties. Proc. IEE 112(1965)4, S. 681...688.

- [11] R. R. Bockemuehl: Analysis of Field-Effect Transistors with Arbitrary Charge Distribution. Trans. IEEE Electron Devices ED-10(1963)1, S. 31...34.

- [12] D. R. Olsen: Equivalent Circuit for a Field-Effect Transistor. Proc. IEEE 51(1963)1, S. 254.

- [13] A. Van der Ziel: Thermal Noise in Field-Effect Transistors. Proc. IRE 50(1962)8, S. 1808...1812.

- [14] A. Van der Ziel: Gate Noise in Field-Effect Transistors at Moderately High Frequencies. Proc. IEEE 51(1963)3, S. 461...467.

- [15] A. Van der Ziel: Carrier Density Fluctuation Noise in Field Effect Transistors. Proc. IEEE 51(1963)11, S. 1670.

- [16] C. T. Sah: Theory of Low-Frequency Generation Noise in Junction-Gate Field Effect Transistors. Proc. IEEE 52(1964)7, S. 795...814.

## Adresse des Autors:

Dr. sc. techn., Dr.-Ing. h. c., Prof. M. J. O. Strutt, Vorstand des Institutes für höhere Elektrotechnik der ETH, Gloriastrasse 35, 8006 Zürich.

## Thermoelektrische Kühlung

Von H. Müller und J. Rupprecht, Erlangen

537.322.15

Es wird über den Entwicklungsstand geeigneter Halbleitermaterialien für die technische Nutzung des Peltiereffektes, den Aufbau und die Anwendung von Aggregaten berichtet. Die derzeit günstigsten Halbleiter sind Mischkristalle der Telluride und Selenide des Wismut und Antimon. Die Aufbereitung erfolgt entweder nach pulvermetallurgischen oder dem Normal-Freezing-Verfahren. Die Anwendung plattenförmiger Aggregate wird am Beispiel eines Thermofaches für den wahlweisen Kühl- oder Wärmebetrieb sowie für die Bauelementekühlung bei tiefen Temperaturen mittels Peltierkaskaden beschrieben.

## 1. Einleitung

Die Theorie der thermoelektrischen Kühlung, basierend auf dem Peltiereffekt, sowie die Bemessung von Peltieraggrega-

Les auteurs relatent où en sont le développement des semi-conducteurs convenant pour l'utilisation technique de l'effet Peltier, ainsi que la fabrication et l'emploi des piles thermo-électriques. Les semi-conducteurs les plus appropriés sont actuellement des cristaux mixtes de tellurures et séléniums de bismuth et d'antimoine. On les obtient soit par le procédé pulvéro-métallurgique, soit par «normal-freezing». Comme exemple d'application des piles plates, l'article décrit leur emploi pour réaliser une loge thermique pouvant servir, à volonté, à chauffer ou à refroidir, ainsi qu'à réfrigérer des éléments de construction au moyen de cascades Peltier, jusqu'à de basses températures.

gaten wurde in den letzten Jahren ausführlich in der Fachliteratur behandelt [1; 2; 3]<sup>1)</sup>. Im vorliegenden Beitrag wer-

<sup>1)</sup> Siehe Literatur am Schluss des Aufsatzes.