Zeitschrift: Bulletin des Schweizerischen Elektrotechnischen Vereins

Herausgeber: Schweizerischer Elektrotechnischer Verein ; Verband Schweizerischer

Elektrizitätswerke

**Band:** 56 (1965)

Heft: 4

Artikel: Planar-Technologie und Festkörper-Schaltkreise

**Autor:** Steinmaier, W.

**DOI:** https://doi.org/10.5169/seals-916341

## Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. Mehr erfahren

## **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. En savoir plus

# Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. Find out more

**Download PDF: 21.11.2025**

ETH-Bibliothek Zürich, E-Periodica, https://www.e-periodica.ch

# Planar-Technologie und Festkörper-Schaltkreise 1)

Von W. Steinmaier, Nijmegen

621.382.062

Neben einer kurzen Beschreibung von wichtigen technologischen Verfahren wird versucht, die wesentlichen Merkmale von Festkörper-Schaltkreisen darzustellen. Sich hieraus ergebende Gesichtspunkte für den Entwurf von Schaltkreisen werden aufgezeigt und diskutiert.

Après une description sommaire des phases les plus importantes de la réalisation des circuits intégrés semiconducteurs, suivent quelques considérations des propriétés typiques de ces circuits. Quelques conséquences importantes à prendre en compte pour le développement électrique des circuits sont discutées.

#### 1. Einführung

Die Technik der Halbleiterschaltkreise ist noch jung und befindet sich in voller Entwicklung. Es sei hier versucht, über den heutigen Stand der Technik zu berichten.

Bei der Fertigung von Halbleiterelementen ist es möglich, von verschiedenen Grundmaterialien und Fertigungstechniken auszugehen. In der letzten Zeit haben sich Silizium als Basismaterial und die Diffusion als Arbeitstechnik in der Industrie immer mehr durchgesetzt. Fig. 1 und 2 zeigen zwei Beispiele diffundierter Si-Bauelemente.

33'707-726

$Fig.~1\\ \textbf{Si-Leistungsdiode}~\textbf{für}~\textbf{250}~\textbf{A,}~\textbf{1200}~\textbf{V}\_$

In Fig. 1 ist eine Leistungsdiode 72BAY für 250 A, bei einem Scheitelstrom von 4000 A und 1200 V Gleichspannung, dargestellt. Fig. 2 zeigt einen integrierten, monolithisch ausgeführten Verstärker für Hörgeräte. Das Element gibt mehr als 75 dB Leistungsverstärkung und verbraucht 1,1 mA bei 1,3 V Batteriespannung.

Fig. 2

Integrierter Verstärker für Hörgeräte

Die beiden wichtigsten Schritte in der Entwicklung diffundierter Si-Bauelemente stellen die Erfindung der jetzt schon gut bekannten «Planartechnik» und der «Epitaxie» dar.

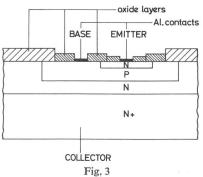

Die *Planartechnik* gestattet durch Oxidmaskierung eine selektive Diffusion von elektrisch aktiven Elementen in das Silizium. Die Diffusion tritt an jenen Stellen auf, wo SiO<sub>2</sub> nach Abdecken mit einer Maske durch photolithographische

Schematischer Aufbau eines epitaxialen Planartransistors

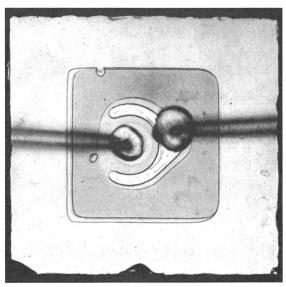

Verfahren entfernt wurde. Ein weiteres Merkmal dieser Technik ist, dass alle so entstandenen Übergänge durch SiO<sub>2</sub> bedeckt sind und in einer Ebene liegen (Fig. 3 und 4).

Unter «Epitaxie» versteht man die Abscheidung von dünnen, monokristallinen Si-Schichten auf Si-Einkristallsubstrate. Durch gezielte Dotierung der Abscheidung gelingt es, bei entsprechender Wahl des Substratwiderstandes, bestimmte Dotierungsprofile herzustellen.

Die Planartechnik gestattet grosse Beweglichkeit in der Entwicklung von Bauelementen verschiedener Eigenschaften. Diese ergibt sich aus der Verwendung von Masken, entspre-

Fig. 4

Planartransistor

<sup>&</sup>lt;sup>1</sup>) Vortrag, gehalten an Elektronik-Tagung im Rahmen der Schweiz. Fernseh-, Elektronik-, Radio/Phono-Ausstellung am 28. August 1964 in Zürich.

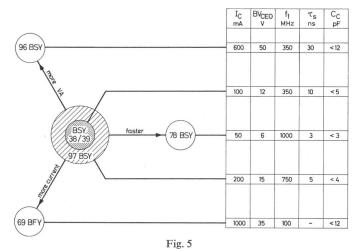

Wichtige elektrische Parameter einiger Schalttransistoren  $I_C$  Kollektorstrom;  $BV_{CEO}$  Kollektor-Emitter-Durchbruchsspannung;  $f_1$  Grenzfrequenz ( $\beta=1$ );  $\tau_s$  Speicherzeit;  $C_C$  Kollektorkapazität

chend gewählter Geometrie mit demselben oder annähernd demselben Diffusionsprogramm, und der Benützung von epitaxialem oder nichtepitaxialem Material. Dies erklärt die enorme und oft verwirrende Vielfalt von «planaren» und «planarepitaxialen» Typen-Nummern, welchen sich der Verbraucher gegenüber sieht.

Fig. 5 gibt eine Übersicht der wichtigsten elektrischen Parameter repräsentativer Schalttransistoren, wie sie durch Anpassung der Geometrie bei annähernd denselben Diffusionen erreicht wurden.

Wesentlich für eine flexible Transistorentwicklung ist die Möglichkeit, schnell entsprechende Masken zu entwerfen und herzustellen. Auf einer Si-Scheibe von etwa 2,5 cm Durchmesser können etwa 2000 Transistoren gleichzeitig angefertigt werden. Es ist daher wichtig, dass die Maskenabbildungen mit grösster Präzision ausgeführt werden.

Ein praktisches Beispiel zeigt Fig. 6. Hier ist eine Al-Kontakt-Maske eines 800-MHz-Transistors abgebildet. Der Abstand zwischen zwei benachbarten Al-Streifen beträgt nur drei μm.

Fig. 6

Maske für die Herstellung der Al-Kontakte eines Transistors

# 2. Integrierte Schaltungen

Bei Verwendung entsprechender Masken ist es von der Herstellung der Einzelelemente zur Realisierung von Mehrfachtransistoren und -Dioden nur ein kleiner Schritt. Nur aus Gründen der besseren Bedienbarkeit wird bei Einzeltransistoren eine minimale Kristallabmessung gefordert, was zur Folge hat, dass nur ein relativ geringer Teil des Kristalls für den eigentlichen Transistor benützt wird. Weit günstiger ist die Raumausnützung bei Mehrfachelementen.

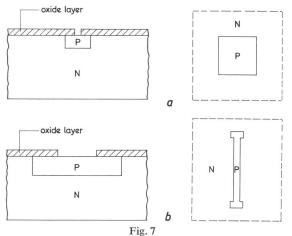

Der nächste Schritt führt zu vollständigen Schaltungen. Wesentlich ist hiebei, dass die für den Transistor verwendeten Diffusionsprozesse auch zur Herstellung von Widerständen und Kapazitäten verwendet werden können (Fig. 7).

Konstruktion einer Diode (Kondensator) (a) und eines Widerstandes (b)

### 3. Widerstände

Für Widerstände gilt die einfache Formel

$$R=\varrho_s\frac{l}{b}$$

wobei  $\varrho_s$  den Schichtenwiderstand bedeutet. l, die Länge und b, die Breite des Widerstandes, werden durch das Maskenbild festgelegt.

Abweichungen von den Nennwerten werden in erster Linie durch Streuungen von  $\varrho_s$  und durch variierende Streifenbreiten verursacht. Daraus ergeben sich Toleranzen von etwa  $\pm$  15 % Bei Widerstandsverhältnissen kann man mit weit engeren Toleranzen ( $\approx$  5 % ) rechnen, da die Streuung, die durch die Herstellung bedingt ist, an benachbarten Stellen einer Scheibe erheblich geringer sein kann als die aus vielen Chargen errechnete mittlere Abweichung. Das Arbeiten mit Widerstandsverhältnissen anstatt mit Widerstandswerten ist daher nach Möglichkeit vorzuziehen.

### 4. Kondensatoren

Für Kondensatoren kann von den kapazitiven Effekten der PN-Übergänge Gebrauch gemacht werden. Die Kapazität wird durch die Oberfläche des PN-Überganges, die Störstellenverteilung im Silizium und die Spannung am PN-Übergang bestimmt.

Die Grössenordnung der Kapazitätswerte liegt bei etwa 100 pF/mm². Kondensatoren bedingen grosse Oberflächen,

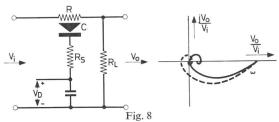

Verwendung eines diffundierten Widerstandes als RC-Filter — mit  $R_s$  —— ohne  $R_s$

$V_i$  Eingangsspannung;  $V_0$  Ausgangsspannung;  $V_D$  Sperrspannung; R Filterwiderstand;  $R_S$  Serienwiderstand;  $R_L$  Lastwiderstand;  $\omega$  Kreisfrequenz

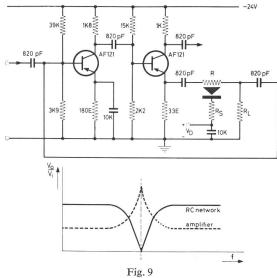

Verstärkerschaltung mit Filter aus Fig. 8

so dass grosse Kapazitätswerte möglichst vermieden werden sollten. Die kapazitive Kopplung eines diffundierten Widerstandes mit dem Grundmaterial kann zur Konstruktion eines *RC*-Filters verwendet werden (Fig. 8). Der Frequenzgang kann durch externe Komponenten beeinflusst werden. In Fig. 9 ist ein solcher Filter in einen Verstärker eingebaut.

#### 5. Induktivitäten

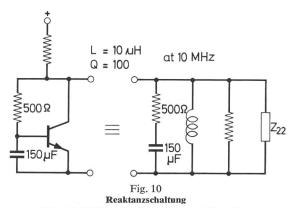

Induktivitäten können in der Planartechnik nicht verwirklicht werden. Man muss sich mit Simulierungsschaltungen behelfen, welche aus realisierbaren Bauelementen aufgebaut sind. Fig. 10 zeigt ein einfaches Beispiel einer Reaktanzschaltung.

L Induktivität; Q Gütefaktor; Z Impedanz

## 6. Isolation und Verbindungen

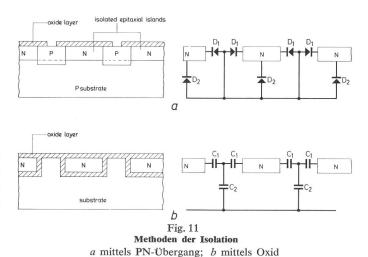

Die letzte und wichtigste Frage ist das Problem der elektrischen Isolierung der verschiedenen Bauelemente.

Vereinigt man mehrere, nach dem beschriebenen Verfahren hergestellte Widerstände, Dioden und Transistoren auf eine gemeinsame Unterlage, so ergeben sich zwangsweise gewisse leitende Verbindungen. Beispielsweise wären die Kollektoren zweier Transistoren über die gemeinsame N-leitende Unterlage verbunden. Um das zu vermeiden, bringt man die Komponenten nicht direkt auf eine N-leitende Schicht, sondern auf eine N-leitende Epitaxialschicht, welche ihrerseits auf eine P-leitende Unterlage aufgewachsen ist. Diese Epitaxialschicht wird dann mittels einer P-Diffusion, die durch entsprechende Fenster der Oxid-Schicht erfolgt und bis hinab ins P-leitende

Substrat reicht, in einzelne N-leitende Inseln aufgeteilt. Die Inseln sind demnach durch PN-Übergänge voneinander getrennt (Fig. 11a). Jeder PN-Übergang ist in einem Ersatzschaltbild durch eine Diode darstellbar.  $D_1$  sind die durch Diffusion entstandenen Dioden und  $D_2$  die durch die Epitaxie erzeugten. Mit N sind die N-leitenden Inseln bezeichnet. Komponenten, die elektrisch voneinander isoliert sein sollen, werden auf getrennten N-Inseln untergebracht. Die Unvollkommenheiten dieser Isolation durch Sperrströme und Sperrschichtkapazitäten der Dioden lassen sich für viele Anwendungen genügend klein halten.

Eine weitere Möglichkeit der Isolierung ist ebenfalls in Fig. 11b und in Fig. 12 gezeigt. Hier sind N-leitende, monokristalline Inseln von SiO<sub>2</sub> umgeben und in polykristallines Silizium eingebettet.

Diese Methode ermöglicht eine Herabsetzung der parasitären Kapazitäten, wie sie bei obiger Methode auftreten, was einen wichtigen Schritt in Richtung der vollständigen Isolierung integrierter Schaltungen darstellt.

Im Gegensatz zu dem als Einzelbauelement gefertigten Planartransistor muss bei einem Transistor in Festkörperschaltungen auch der Kollektoranschluss auf der Oberseite des Kristalls angebracht werden. Als Nachteil ergibt sich ein grösserer Kollektor-Serienwiderstand, der durch das ausgedehnte Bahngebiet zwischen Kollektor-Basis-Übergang und Kollektoranschluss zu Stande kommt.

Es gibt Möglichkeiten, den Kollektor-Serienwiderstand herabzusetzen. Man fügt zur Erzielung einer möglichst nie-

Fig. 12

Monokristalline Inseln sind durch Oxid und polykristallines Silizium

voneinander getrennt

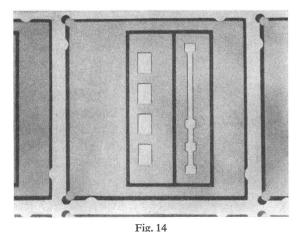

Fig. 13

Isolationsdiffusion

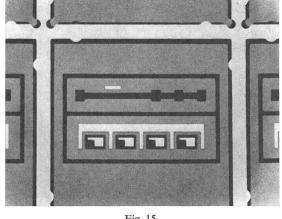

Fig. 15

Emitterdiffusion

drigen Kollektorspannung zwischen P-leitender Unterlage und N-leitender Epitaxialschicht manchmal eine zweite N-Schicht mit niedrigerem Widerstand ein. Diese Zone wird entweder nach dem Epitaxialverfahren oder mittels Diffusion durch ein entsprechend geätztes Fenster in der Oxidschicht erzeugt. Erst anschliessend lässt man die epitaxiale N-Schicht aufwachsen.

Schliesslich müssen die in den Fenstern der Oxidschicht liegenden Aluminiumanschlüsse der einzelnen Komponenten nach dem vorgeschriebenen Verdrahtungsschema miteinander verbunden werden. Hiezu dampft man metallische Leiterbahnen (Aluminium) auf die Oberfläche der Oxidschicht.

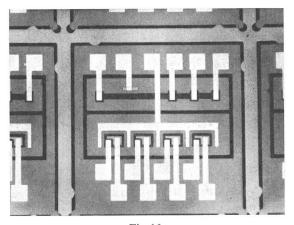

In den Fig. 13...16 sind die einzelnen Schritte des Verfahrens dargestellt.

### 7. Einige Gesichtspunkte bei dem Entwurf von Schaltkreisen

Es gibt im Wesentlichen drei wichtige Faktoren, welche beim Entwurf von Festkörperschaltkreisen unbedingt beachtet werden müssen:

- a) Das elektrische Verhalten;

- b) Der Preis;

- c) Die Zuverlässigkeit der Schaltung.

Entsprechend dem Anwendungsgebiet wird einer dieser Faktoren bei der Wahl einer bestimmten Schaltung ausschlaggebend sein. Der optimale Schaltkreis wird deshalb immer mit dem optimalen Kompromiss zwischen diesen drei Faktoren übereinstimmen. Als Erschwernis gilt, dass heute

viele Schaltungsingenieure noch nicht genügend Erfahrung besitzen, einen solchen optimalen Kompromiss zu finden. Sie denken bei der Realisierung von Schaltungen in Termen diskreter aktiver und passiver Komponenten. Es wird hiebei als selbstverständlich angenommen, dass eine aktive Komponente teurer zu stehen kommt als ein passives Element, und dass Widerstände die billigsten aller Komponenten sind. Der «worst case»-Entwurf einer Schaltung basiert immer auf der unkorrelierten Streuung diskreter Komponentenparameter. Für die Integrierung bestehender Schaltkreise unter Berücksichtigung des erwähnten Kompromisses ist eine Veränderung dieses Zustandes sicherlich notwendig. Die geometrische Anordnung der Komponenten im Kristall beeinflusst das elektrische Verhalten, wenn man die Widerstands- und kapazitive Kopplung zwischen ihnen berücksichtigt. Wie gezeigt wurde, ist es heute mit technologischen Mitteln schon möglich, die parasitären Kapazitäten zwischen den Isolationsinseln praktisch völlig zu unterdrücken, so dass integrierte Schaltungen nunmehr auch für hohe Frequenzen verwendet werden können.

Der Preis integrierter Schaltungen wird in erster Linie nicht durch die Anzahl der Elemente in der Schaltung bestimmt, sondern durch die erforderliche Kristalloberfläche und die Zahl der Anschlüsse vom Kristall zur Aussenwelt. Dazu sei noch folgendes erwähnt: Jede Siliziumscheibe enthält unvermeidliche Fehler. Je grösser der Kristall gewählt wird, umso grösser ist die Wahrscheinlichkeit, dass er einen dieser Fehler enthält und somit unbrauchbar wird. Ausser-

Diffusion der Widerstände und Basen der Transistoren

Fig. 16 Schaltung nach Anbringen der Leiterspuren

Fig. 17

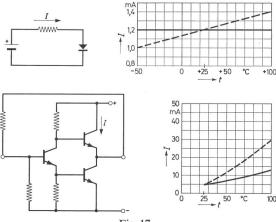

Stromstabilisierung durch einen integrierten Widerstand

I Ruhestrom; t Temperatur

konventionelle Komponente

integrierte Festkörperschaltkreise

dem nimmt die Zahl der Kristalle pro Scheibe stark zu, wenn deren Abmessungen verkleinert werden. Als allgemeine Regeln zur Verkleinerung der Kristalloberfläche seien erwähnt:

- a) Die Verwendung von so wenig isolierten Inseln wie möglich,

- b) Vermeidung von grossen Widerständen (in Bezug auf die Kristalloberfläche kostet ein 15-k $\Omega$ -Widerstand mehr als 3 zusätzliche Transistoren),

- c) Vermeidung von grossen Kapazitäten.

Fig. 17 zeigt die Temperaturabhängigkeit des Stromes durch eine Halbleiterdiode in Serie mit einem konventionellen und integrierten Widerstand.

Wie bereits erwähnt, erhält man keinen optimalen Festkörperschaltkreis, wenn man eine «konventionelle» Schaltung einfach integriert. Dazu ist eine enge Zusammenarbeit zwischen Technologen und Schaltungstechnikern notwendig. Ist es heute noch wegen der schnellen Entwicklung technologischer Prozesse schwierig, ohne täglichen Kontakt auf dem laufenden zu bleiben, so ist doch zu hoffen, dass sich in Zukunft ein Denken in Termen integrierter Komponenten durchsetzen wird. Daneben ist es natürlich wichtig, dass sich eine gewisse Normung integrierter Produkte vollzieht, wie es ja für industrielle Erzeugnisse notwendig ist.

In manchen Fällen kann von den spezifischen Eigenschaften der Schaltkreise vorteilhaft Gebrauch gemacht werden.

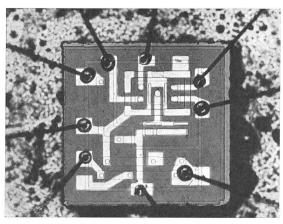

Fig. 18 Masterchip I

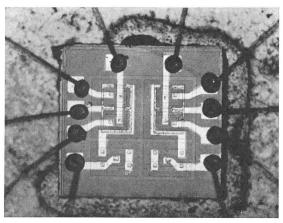

Fig. 19 Masterchip II

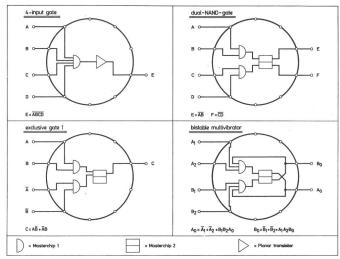

Für den digitalen Sektor wurde von Philips die sog. Masterchipskonzeption gewählt. Es wurden zwei sog. «Masterchip» entwickelt. Jedes dieser Chips enthält eine Anzahl von Elementen (Transistoren, Dioden und Widerstände), welche in entsprechende Weise voneinander isoliert sind. Ausgewählte Al-Leiterspuren ermöglichen die Verwendung der Chips für verschiedene Schaltungstechniken. Vollständige Schaltungen (Gatter, doppelte Gatter, Flip-Flop, Schieberegister, Halbaddierer usw.) können durch entsprechende Kombination von Chips und Planartransistoren realisiert werden.

Fig. 18 zeigt Masterchip I, ausgeführt auf einem Kristall von  $1 \times 1$  mm und Fig. 19 Masterchip II.

Fig. 20 Kombinationsschaltungen

Fig. 20 gibt schliesslich eine Reihe von Kombinations-Möglichkeiten der beiden Systeme und eventuell Planartransistoren in einem Gehäuse. Diese Lösung hat zwei wesentliche Vorteile: Erstens ermöglicht sie eine relativ rasche Realisierung von Schaltungen entsprechend den verschiedenen Wünschen. Zweitens gestattet sie dem Verbraucher, mit dem spezifischen Verhalten integrierter Komponenten vertraut zu werden, so dass eine derartige halbintegrierte Anordnung als Ausgangspunkt für eine vollintegrierte Schaltung dienen kann.

## Adresse des Autors:

Dr. W. Steinmaier, Philips N. V., Nijmegen (Niederlande).