**Zeitschrift:** Bulletin des Schweizerischen Elektrotechnischen Vereins

**Herausgeber:** Schweizerischer Elektrotechnischer Verein ; Verband Schweizerischer Elektrizitätswerke

**Band:** 55 (1964)

**Heft:** 5

**Artikel:** Logische Elemente mit Widerstandskopplung

**Autor:** Schaffner, H.

**DOI:** <https://doi.org/10.5169/seals-916687>

#### **Nutzungsbedingungen**

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. [Mehr erfahren](#)

#### **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. [En savoir plus](#)

#### **Terms of use**

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. [Find out more](#)

**Download PDF:** 14.01.2026

**ETH-Bibliothek Zürich, E-Periodica, <https://www.e-periodica.ch>**

# BULLETIN

DES SCHWEIZERISCHEN ELEKTROTECHNISCHEN VEREINS

Gemeinsames Publikationsorgan des Schweizerischen Elektrotechnischen Vereins (SEV)

und des Verbandes Schweizerischer Elektrizitätswerke (VSE)

## Logische Elemente mit Widerstandskopplung

Von H. Schaffner, Solothurn

621.374.32:517.11

### 1. Einführung

In logischen Elementen werden Transistoren miteinander oft durch Widerstände gekoppelt. Widerstandskopplung ist preislich meist vorteilhafter als Diodenkopplung; gegen die Widerstandskopplung spricht jedoch, dass die maximale Anzahl der Eingänge eines Elementes viel kleiner sein kann als dies bei Diodenkopplung der Fall ist.

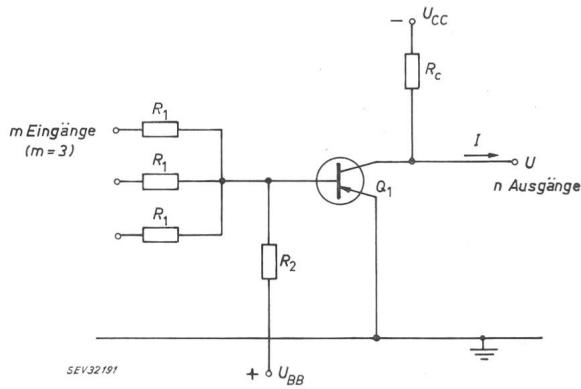

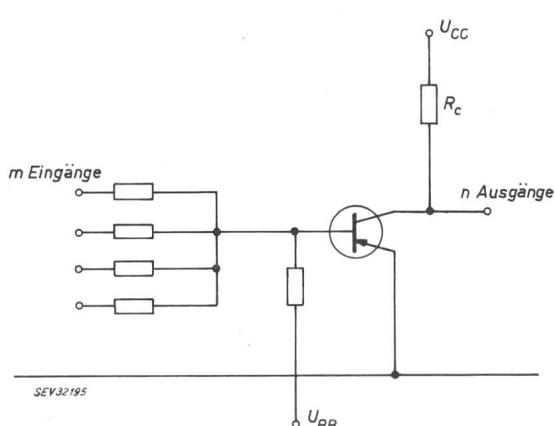

Fig. 1 zeigt ein Grundelement mit einem pnp-Transistor, dessen Basiselektrode durch je einen Widerstand  $R_1$  mit  $m$  Eingangsklemmen verbunden ist. Die Kollektorelektrode des Transistors ist durch einen Widerstand  $R_c$  mit der negativen Sammelschiene, die Basiselektrode ist durch einen Widerstand  $R_2$  mit einem Punkt verbunden, der gegenüber der Emittorelektrode ein positives Potential  $U_{BB}$  aufweist.

Diese Eingangsklemmen werden nun mit den Ausgangsklemmen anderer Elemente verbunden. Dabei sind alle Elemente so konstruiert, dass bei korrekten Eingangssignalen nur zwei diskrete und voneinander verschiedene Signale an den Ausgangsklemmen erscheinen können — das  $L$ -Signal und das  $O$ -Signal. Bei den gebräuchlichen logischen Systemen haben diese beiden Ausgangssignale die allgemeine Form:

Signal  $O$

$$|U_{O\min}| < |U| < |U_{O\max}|$$

Signal  $L$

$$\left| \frac{U_{CC\min} - U}{R_{O\max}} - I_{CBO} \right| < |I| < \left| \frac{U_{CC\max} - U}{R_{O\min}} \right|$$

wobei  $U_O$  die Sättigungsspannung  $U_S$  des Transistors sein

Fig. 1

Grundelement

$R_1$  Eingangswiderstand;  $R_2$  Basiswiderstand;  $Q_1$  Transistor;  $U$  Ausgangsspannung;  $U_{BB}$  Hilfsspannung;  $U_{CC}$  Hauptspannung;  $I$  Ausgangsstrom

<sup>1)</sup> Die Bezeichnungen «min» und «max» beziehen sich auf die Absolutwerte.

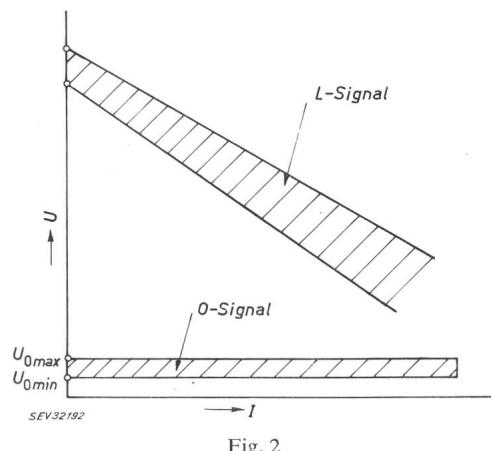

kann.  $U_{CC}$  ist die Kollektorspeisespannung und  $I_{CBO}$  der Reststrom des Transistors. In Fig. 1 ist  $R_o = R_c$ . Die beiden Signale  $O$  und  $L$  werden in Fig. 2 in der Strom-Spannungsebene gezeigt.

Es soll nun angenommen werden, dass mit jeder, mit einer Eingangsklemme des Elementes verbundenen Ausgangsklemme eines anderen Elementes höchstens  $(n - 1)$  zusätzliche Eingangsklemmen verbunden sind, d. h., dass ein solches Element  $n$  andere Elemente steuert.

Fig. 2

O- und L-Signale

$U_{O\max}$  Min. Wert der Ausgangsspannung beim  $O$ -Signal;  $U_{O\min}$  Max. Wert der Ausgangsspannung beim  $O$ -Signal

Mit diesen Annahmen kann die Berechnung des Elementes in allgemeiner Form durchgeführt werden. Als erster Schritt sollen die optimalen Werte für die Kopplungswiderstände  $R_1$  und  $R_2$  berechnet werden. Als zweiter Schritt soll, für konkrete Schaltelemente, die kleinste Stromverstärkung  $h_{FE}$  bestimmt werden, die für die Transistoren dieser Elemente benötigt wird.

In den Berechnungen wird angenommen, dass alle Widerstände die gleichen Toleranzen besitzen. Den Widerständen wird deshalb die Form  $R(1 \pm \Delta)$  gegeben. Um ein Resultat zu erhalten, das allgemein gültig ist, wird auch angenommen, dass verschiedene Elemente von verschiedenen Netzgeräten gespiesen werden. Da diese Netzgeräte verschiedene Ausgangsspannungen haben können, wird der Kollektorspeisespannung die Form  $U_{CC}(1 \pm \epsilon)$  gegeben, während die Zusatzspannung zwischen  $U_{BB\min}$  und  $U_{BB\max}$  liegen soll.

### 2. Der Grundkreis

In Fig. 1 ist der Transistor  $Q_1$  mit  $m$  Eingangsklemmen verbunden. Jede Eingangsklemme ist mit höchstens  $n - 1$

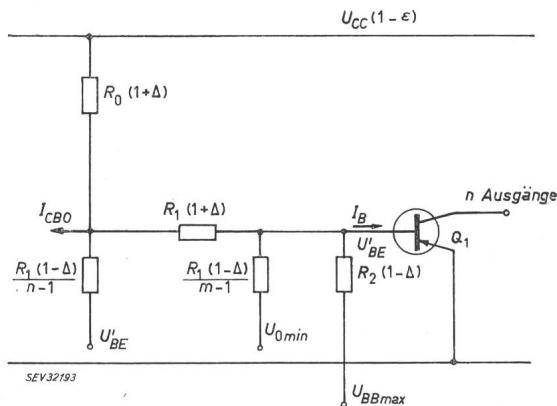

Fig. 3

Worst-case, leitender Zustand

$R_0$  Kollektorwiderstand;  $I_{CBO}$  Reststrom des Transistors;  $I_B$  Basisstrom;  $U'_{BE}$  Eingangsspannung des Transistors

Weitere Bezeichnungen siehe Fig. 1 und 2

Eingangsklemmen anderer Elemente verbunden. Die Zahlen  $m$  und  $n$  sind nicht notwendigerweise identisch. Beispielsweise kann ein ODER-NICHT-Element 4 Eingänge haben. Es kann aber selber höchstens imstande sein 3 andere ODER-NICHT-Elemente zu steuern. Der Transistor  $Q_1$  kann auch der erste Transistor eines ODER-Elementes mit komplementärem Ausgang sein.

Alle Basiselektroden sind durch je einen Widerstand  $R_2$  mit dem positiven Potential  $U_{BB}$  verbunden. Dieser Widerstand ist notwendig, um die Transistoren in den sperrenden Zustand zu versetzen. Im folgenden wird angenommen, dass zur Sperrung des Transistors die Eingangsspannung  $U_{BE}$  den Wert  $U''_{BE}$  haben muss. Im leitenden (gesättigten) Zustand soll die Eingangsspannung den Wert  $U'_BE$  haben. Für pnp-Germaniumtransistoren beträgt  $U'_BE$  beispielsweise ca.  $-0,5$  V,  $U''_{BE}$  ca.  $0,2$  V.

Es wird in den nachfolgenden Betrachtungen angenommen, dass der Leser bis zu einem gewissen Grade mit den Methoden der «worst-case»-Rechnungsart vertraut ist. Dabei wird die Schaltung für den Fall durchgerechnet, dass «alles schief geht», d. h., dass alle Widerstände und Spannungen im Bereich der Toleranzen ihren ungünstigsten Wert haben und dass auch die mit einem Element verbundenen andern Elemente den denkbar ungünstigsten Zustand einnehmen.

### 3. Die «worst-case»-Rechnung

#### 3.1 Transistor leitend

Fig. 3 zeigt den Grundkreis für den Fall, dass nur an eine der Eingangsklemmen das Signal  $L$  angelegt ist, während an den  $m-1$  andern Eingangsklemmen das Signal  $O$  erscheint.

In der Schaltung sind alle Toleranzen so gewählt, dass der Basisstrom  $I_B$  des Transistors  $Q_1$  möglichst klein wird. Wie man sich leicht überzeugen kann, hat dieser Basisstrom den Wert:

$$I_B = \frac{U_{CC}(1-\epsilon) - R_0 I_{CBO}(1+\Delta) - U'_BE}{(R_1 + n' R_0)(1+\Delta)} - (m-1) \frac{U'_BE - U_{omin}}{R_1(1-\Delta)} + \frac{U_{BBmax} - U'_BE}{R_2(1-\Delta)} \quad (1)$$

wobei  $n' = n + 2 \frac{\Delta(n-1)}{1-\Delta}$  ist.

Dieser Basisstrom muss nun den Transistor in die Sättigung treiben. Ist  $I_{Cmax}$  der grösste mögliche Kollektorstrom, dann muss:

$$I_B \geq \frac{I_{Cmax}}{h_{FE}}$$

oder

$$h_{FE} \geq \frac{I_{Cmax}}{I_B}$$

#### 3.2 Transistor gesperrt

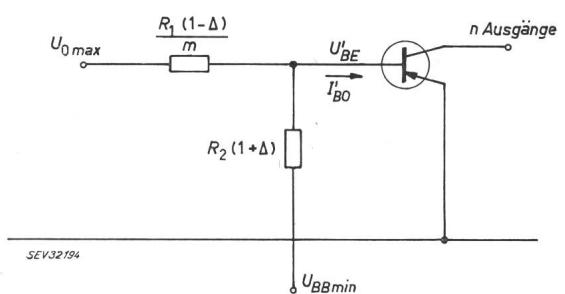

In der Schaltung der Fig. 4 wird angenommen, dass an alle Eingangsklemmen das Signal  $O$  angelegt wird. Die Werte der Widerstände und Spannungen sind so gewählt, dass die Eingangsspannung des Transistors  $U_{BE}$  einen möglichst ungünstigen Wert annimmt. Die Bedingung für  $U_{BE} = U''_{BE}$  ist:

$$\frac{m(U_{omax} - U''_{BE})}{R_1(1-\Delta)} + \frac{U_{BBmin} - U''_{BE}}{R_2(1+\Delta)} + I'_{BO} = 0 \quad (3)$$

Dabei ist  $U''_{BE}$  die Eingangsspannung, die notwendig ist, um den Transistor zu sperren und  $I'_{BO}$  der Basisstrom des gesperrten Transistors.

#### 4. Die Berechnung von $R_1$ und $h_{FE}$

Aus Gl. (3) folgt für  $R_2$ :

$$\frac{1}{R_2} = - \frac{m(1+\Delta)(U_{omax} - U''_{BE})}{R_1(1-\Delta)(U_{BBmin} - U''_{BE})} - \frac{I'_{BO}(1+\Delta)}{U_{BBmin} - U''_{BE}} \quad (4)$$

Dieser Wert kann nun in Gl. (1) eingesetzt werden:

$$I_B = \frac{U_{CC}(1-\epsilon) - R_0 I_{CBO}(1+\Delta) - U'_BE}{(n' R_0 + R_1)(1+\Delta)} - \frac{1}{R_1} \left[ (m-1) \frac{U'_BE - U_{omin}}{1-\Delta} + \frac{m(1+\Delta)(U_{omax} - U''_{BE})(U_{BBmax} - U'_BE)}{(1-\Delta)^2(U_{BBmin} - U''_{BE})} \right] - I'_{BO} \frac{1+\Delta}{1-\Delta} \cdot \frac{U_{BBmax} - U'_BE}{U_{BBmin} - U''_{BE}} \quad (5)$$

Diese Gleichung hat die allgemeine Form:

$$I_B = \frac{U_{CC}}{n' R_0} \left( \frac{a n' R_0}{n' R_0 + R_1} - b \frac{n' R_0}{R_1} - c \right) \quad (6)$$

wobei

$$a = \frac{U_{CC}(1-\epsilon) - U'_BE - R_0 I_{CBO}(1+\Delta)}{U_{CC}(1+\Delta)} \quad (7)$$

$$b = \frac{(U'_BE - U_{omin})(m-1)}{U_{CC}(1-\Delta)} + m \frac{(1+\Delta)(U_{omax} - U''_{BE})(U_{BBmax} - U'_BE)}{(1-\Delta)^2(U_{BBmin} - U''_{BE})U_{CC}}$$

$$c = n' I'_{BO} \frac{1+\Delta}{1-\Delta} \cdot \frac{U_{BBmax} - U'_BE}{U_{BBmin} - U''_{BE}} \cdot \frac{R_0}{U_{CC}}$$

Fig. 4

Worst-case, sperrender Zustand

$U''_{BE}$  Eingangsspannung;  $I'_{BO}$  Reststrom

Weitere Bezeichnungen siehe Fig. 1

Der Basisstrom aus Gl. (6) hat einen Maximalwert:

$$I_B = \frac{U_{CC}}{n' R_o} [(\sqrt{a} + \sqrt{b})^2 - c] \quad (8)$$

wenn

$$R_1 = \frac{n' R_o}{\sqrt{\frac{a}{b}} - 1} \quad (9)$$

Die Stromverstärkung des Transistors muss dann mindestens den Wert

$$\frac{I}{h_{FE}} = \frac{U_{CC}}{n' R_o I_{Cmax}} [(\sqrt{a} - \sqrt{b})^2 - c] \quad (10)$$

haben, wobei  $I_{Cmax}$  der höchstmögliche Kollektorstrom ist. Um diese optimale Bedingung zu erreichen, muss die Gl. (9) erfüllt sein und  $R_2$  muss den in Gl. (4) angegebenen Wert haben.

### 5. Das einfache ODER-NICHT-(NOR-)Element (Fig. 5)

Für ein ODER-NICHT-Element mit  $m$  Eingängen und  $n$  Ausgängen gilt für den Maximalwert des Kollektorstromes (wobei  $R_o = R_c$ ,  $U_o = U_S$ ):

$$I_{Cmax} \approx \frac{U_{CC}(1 + \varepsilon)}{R_c(1 - \Delta)}$$

Somit gilt für den minimal notwendigen Wert von  $h_{FE}$ :

$$\frac{1}{h_{FE}} \approx \frac{1 - \Delta}{n'(1 + \varepsilon)} [(\sqrt{a} - \sqrt{b})^2 - c] \quad (11)$$

In praktischen ODER-NICHT-Elementen kann angenommen werden, dass:

$$\begin{aligned} |U_{CC}(1 - \varepsilon)| &\gg |U_{BE}| + R_c I_{CBO}(1 + \Delta) \\ |U_{BBmax}| &\gg |U_{BE}| \\ |U_{BBmin}| &\gg |U_{BE}''| \end{aligned}$$

Die Werte für  $a$ ,  $b$  und  $c$  vereinfachen sich damit zu:

$$a = \frac{1 - \varepsilon}{1 + \Delta}$$

$$\begin{aligned} b &= (m - 1) \frac{U_{BE} - U_{Smin}}{U_{CC}(1 - \Delta)} + \\ &\quad + m \frac{1 + \Delta}{(1 - \Delta)^2} \cdot \frac{U_{BBmax}(U_{Smax} - U_{BE}'')}{U_{BBmin} U_{CC}} \end{aligned}$$

$$c = n' I_{BO} \frac{1 + \Delta}{1 - \Delta} \cdot \frac{U_{BBmax}}{U_{BBmin}} \cdot \frac{R_c}{U_{CC}}$$

Fig. 5

NOR-Element

$R_c$  Kollektorwiderstand

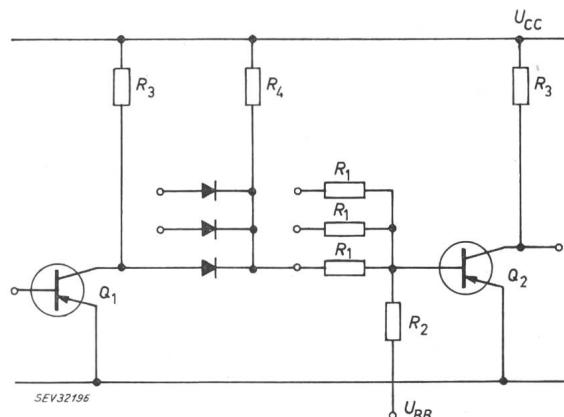

Fig. 6

NOR-Element mit AND-Gatter

$R_3, R_4$  Widerstand

Weitere Bezeichnungen siehe Fig. 1

Für jedes widerstandsgekoppelte ODER-NICHT-Element kann aus diesen Werten und aus den Gl. (9) und (10) der optimale Wert von  $R_1$  und die minimale Stromverstärkung des Transistors berechnet werden.

Beispiel:  $m = n = 4$  (vier Eingänge, vier Ausgänge)

$\varepsilon = 0,1$ ,  $\Delta = 0,1$  (10% Toleranz),  $U_{CC} = -24$  V,  $U_{BE} = -0,6$  V,  $U_{BE}'' = 0,2$  V,  $U_{Smax} = -0,15$  V,  $I_{BO} = 0,05$  mA,  $U_{BBmax} = U_{BBmin} = 12$  V,  $R_c = 6$  kΩ.

Aus den obigen Gleichungen folgt:

$$n' = 4,67$$

$$a = 0,82$$

$$b = 0,165$$

$$c = 0,071$$

Der optimale Wert für  $R_1$  aus Gl. (9) ist  $R_1 = 22,5$  kΩ. Der Transistor muss (Gl. 11) mindestens eine Stromverstärkung von  $h_{FE} = 31$  haben.

### 6. ODER-NICHT-(NOR-)Element mit vorgeschaltetem UND-Gatter

Fig. 6 zeigt ein ODER-NICHT-Element, das mit der Ausgangsklemme eines UND-Gatters verbunden ist, wobei das Gatter aus einigen Dioden und einem Widerstand  $R_4$  besteht. Um übersichtliche Verhältnisse zu schaffen, soll angenommen werden, dass der Ausgang eines Gatters nur mit einem Eingangswiderstand  $R_1$  verbunden werden darf und dass der durch einen Eingangswiderstand fließende Strom in erster Annäherung unabhängig davon sein soll, ob er direkt oder durch ein Gatter mit dem Transistor  $Q_1$  verbunden ist. Gleichung 1 zeigt, dass diese Bedingung erfüllt ist, wenn  $R_4 = n' R_3$ . Der Kollektor des Transistors  $Q_1$  kann dabei mit  $n$  Gattern oder Eingangswiderständen belastet werden.

$U_0$  besteht nun aus der Sättigungsspannung des Transistors  $Q_1$  in Serie mit dem Spannungsabfall an einer leitenden Diode.  $U_{omin}$  kann daher einen relativ hohen Wert annehmen.

Im leitenden Zustand tritt der «worst case» dann ein, wenn von den  $m$  Eingängen des Transistors  $Q_2$  einer durch ein Gatter mit dem nichtleitenden Transistor  $Q_1$  verbunden ist, während die andern  $m - 1$  Eingänge direkt mit gesättigten Transistoren verbunden sind. Im nichtleitenden Fall tritt der «worst case» ein, wenn alle  $m$  Eingänge je durch ein Gatter mit einem gesättigten Transistor verbunden sind. Deshalb entspricht  $U_{omin}$  dem Minimalwert der Sättigungsspannung,  $U_{max}$  der Summe

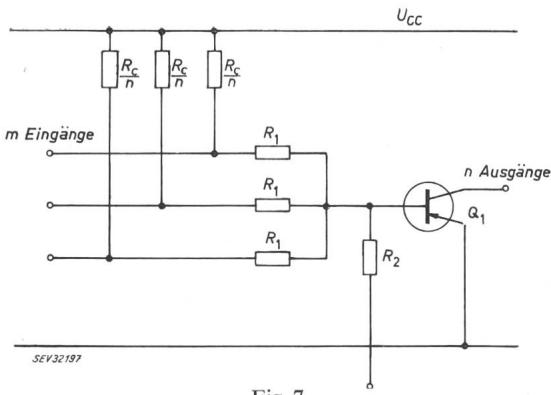

Fig. 7

Modifizierte NOR-Einheit

$R_c/n$  Kollektorwiderstand

aus maximaler Sättigungsspannung und dem Spannungsabfall der Gatterdiode.

Da der nichtleitende Zustand mit Gatter höhere Anforderungen stellt als ohne Gatter, sollen die Parameter der Gl. (9) und (10) der Stufe mit Gatter entsprechen. Für  $U_{omax}$  ist also  $U_{Smax} + UD$  zu wählen, wobei  $UD$  die Diodenspannung ist.

Der maximale Strom, der im Kollektor des Transistors fliessen kann, ist [da der Kollektorstrom nicht nur durch  $R_4$ , sondern auch durch  $n$  Gatterwiderstände ( $R_4 = n' R_3$ ) fliessen kann]:

$$I_{C\max} \approx \frac{U_{CC}(1+\varepsilon)(n+n')}{R_3(1-\varDelta)n'} \quad (12)$$

$$\frac{1}{h_{FE}} = \frac{1-\varDelta}{(n+n')(1+\varepsilon)} [(\sqrt{a} - \sqrt{b})^2 - c]$$

Die Stromverstärkung mit Gatter muss also mindestens zweimal so hoch sein als ohne Gatter.

### Beispiel:

$$\begin{aligned}

m &= n = 3 & U_{CC} &= -24 \text{ V} \\

&\varepsilon = 0,1 & U_{BB\max} &= U_{BB\min} = 12 \text{ V} \\

&\Delta = 0,1 & R_c &= 6 \text{ k}\Omega \\

U'_{BE} &= -0,6 \text{ V} & U_{o\max} &= -0,7 \text{ V} \\

U''_{BE} &= 0,2 \text{ V} & U_{o\min} &= -0,15 \text{ V} \\

I'_{BO} &= 0

\end{aligned}$$

Diesmal ist

$$a = 0,82; \quad b = 0,15; \quad c = 0$$

und damit

$h_{FE} \gg 29,1$  bei  $R_1 = 15,5 \text{ k}\Omega$

Diese Stromverstärkung ist für praktische Anwendungen, die hohe Zuverlässigkeit erfordern, etwas hoch. Eine Lösung kann in einer Änderung des Kopplungskreises gefunden werden (Fig. 7). Wird nämlich der Kollektorwiderstand der nächsten Stufe zugeschlagen, dann sinkt — wie man sich leicht überzeugen kann — der maximale Kollektorstrom auf:

$$I_{C\max} \approx \frac{U_{CC}(1+\varepsilon)}{R_c(1-\Delta)}$$

also auf den gleichen Wert wie für ODER-NICHT-Einheiten ohne UND-Gatter. Damit sinkt auch die kleinste zulässige Stromverstärkung auf die Hälfte, also auf ca. 14, ein Wert, der durchaus realisierbar ist.

## 7. Zusammenfassung

Eine allgemeine Gleichung für widerstandsgekoppelte logische Elemente wurde abgeleitet und zur Berechnung der kleinsten zulässigen Stromverstärkung für ein ODER-NICHT-(NOR-)Element, das mit einem UND-Gatter kombiniert wurde, benutzt. Dabei zeigte es sich, dass widerstandsgekoppelte ODER-NICHT-Elemente ohne UND-Gatter mit 4 Eingängen und Ausgängen und mit UND-Gatter mit 3 Eingängen und Ausgängen ohne besonderen Aufwand realisierbar sind.

## Literatur

- [1] Bachmann, A. E.: Logische Schaltungen mit Transistoren und Dioden. Bull. SEV 53(1962)18, S. 840...846.

- [2] Pierre, D. A.: Switching Circuit Optimization. Solid State Design 3(1962)10, S. 43...46.

- [3] Veith, P.: Grundlagen und Anwendungen der Widerstands-Transistor-Schaltlogik. Elektronik 12(1963)1, S. 3...8.

### **Adresse des Autors:**

Dr. *H. Schaffner*, Ingenieurbüro für angewandte Elektronik, Luzernstrasse 118, Solothurn.

## **Neuere Erkenntnisse bei der Anwendung acetylierter Papiere in der Elektrotechnik**

Von *W. Dieterle*, Basel

621.315.614.6

Als Fortsetzung früherer Arbeiten [1; 2; 3] 1), worin vor allem die grundlegenden Eigenschaften von acetyliertem Papier (Isocel) beschrieben wurden, wird über den heutigen Stand der Verwendung dieses hochwertigen Isoliermaterials berichtet. Das Anwendungsgebiet der Schichtstoffe wird — neben den klassischen Kombinationen mit Harzen vom Bakelitypus — durch neuere Kombinationen mit Harzen vom Typus Epoxyd, Polyester, Hydrocarbon usw. in interessanter Weise bereichert.

Es folgen Resultate vergleichender Alterungsversuche. Die Acetylierung erhöht die Wärmebeständigkeit von Papier in einem technisch interessanten Masse. Dank der damit erreichten starken Reduktion der Feuchtigkeitsaufnahme ist die Massbeständigkeit erhöht, die Trocknung erleichtert und wird eine höhere Ionisationseinsatz-Spannung erreicht.

Die chemische Stabilität von acetyliertem Papier steigt mit zunehmendem Reinheitsgrad und mit zunehmendem Acetylierungsgrad der Faser oder des Faserverbandes. Der Einfluss verschiedener in der Elektrotechnik verwendeter Metalle auf die Alterung wurde untersucht. Kupfer und Blei haben den grössten Einfluss auf die Alterung von Cellulose. Erstmals werden auch Zahlen des Verlustfaktors, welche an sogenannten Carbonblack-Papieren, jedoch auf Basis von acetyliertem Papier gemessen

Faisant suite à des articles publiés ces dernières années [1, 2, 3] 1), où nous exposions plus particulièrement les propriétés fondamentales du papier acétylé (Isocel), nous décrivons dans le présent exposé l'état actuel de l'emploi de ce matériau isolant de haute qualité. Dans le secteur des produits stratifiés, où le papier acétylé permet d'obtenir des résultats remarquables, de nouvelles combinaisons avec des résines époxydes, polyesters, hydrocarbures, etc. offrent d'intéressantes possibilités, outre les combinaisons habituelles ou classiques avec résines du type bakélite.

Les résultats de mesures comparatives détaillées indiquent les conditions relatives au vieillissement. Par l'acétylation du papier une résistance à la chaleur est atteinte qui est techniquement intéressante. Grâce à la réduction de l'absorption d'humidité la stabilité aux dimensions des papiers acétylés est meilleure, le séchage est plus rapide et on obtient une tension d'ionisation plus élevée. La stabilité chimique du papier acétylé augmente avec le degré de pureté et avec le degré d'acétylation des fibres ou amas de fibres. On a examiné l'influence de divers métaux utilisés fréquemment en électrotechnique sur le vieillissement du papier. Le cuivre et le plomb ont une influence extrêmement mauvaise sur le vieillissement des papiers. Pour la première fois, il nous a été possible d'indiquer des chiffres pour le facteur de pertes, mesuré avec des papiers au noir de fumée, mais à base de papier

---

<sup>1)</sup> Siehe Literatur am Schluss des Aufsatzes.