**Zeitschrift:** Schweizer Ingenieur und Architekt

**Herausgeber:** Verlags-AG der akademischen technischen Vereine

**Band:** 107 (1989)

**Heft:** 33-34

**Artikel:** Die Serienfertigung des 4-Megabit-Speicherchips

**Autor:** Kuhnle, Klaus

**DOI:** <https://doi.org/10.5169/seals-77150>

### Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. [Mehr erfahren](#)

### Conditions d'utilisation

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. [En savoir plus](#)

### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. [Find out more](#)

**Download PDF:** 23.02.2026

**ETH-Bibliothek Zürich, E-Periodica, <https://www.e-periodica.ch>**

# Die Serienfertigung des 4-Megabit-Speicherchips

**Die Beherrschung der Fertigungstechnologie für die Herstellung von Chips mit einer Speicherdichte von mehr als vier Millionen Bits unter gleichzeitiger Verwendung von Wafern (Siliziumscheiben) in einer Grösse, wie sie weltweit noch nie zum Einsatz kam, ist eine herausragende High-Tech-Leistung. Die hochentwickelten Verfahren und Produktionsanlagen wurden der internationalen Fachpresse am 3. Juli 1989 in Stuttgart vorgestellt. Der nachfolgende Beitrag fasst die Vorträge zusammen, welche diese Pressekonferenz begleiteten.**

## Trend der Halbleiterfertigung

Die Halbleiterproduktentwicklung und -fertigung im Entwicklungslaboratorium Böblingen und im Werk Sindelfingen

VON KLAUS KUHNLE,

SINDELFINGEN

gen der IBM Deutschland gehen auf die seit dem Jahre 1968 hergestellten Speicherchips in zunächst bipolarer Technologie zurück, die zu Beginn der 70er Jahre durch die einfachere Feldeffekt-Transistor-Technologie abgelöst wurde.

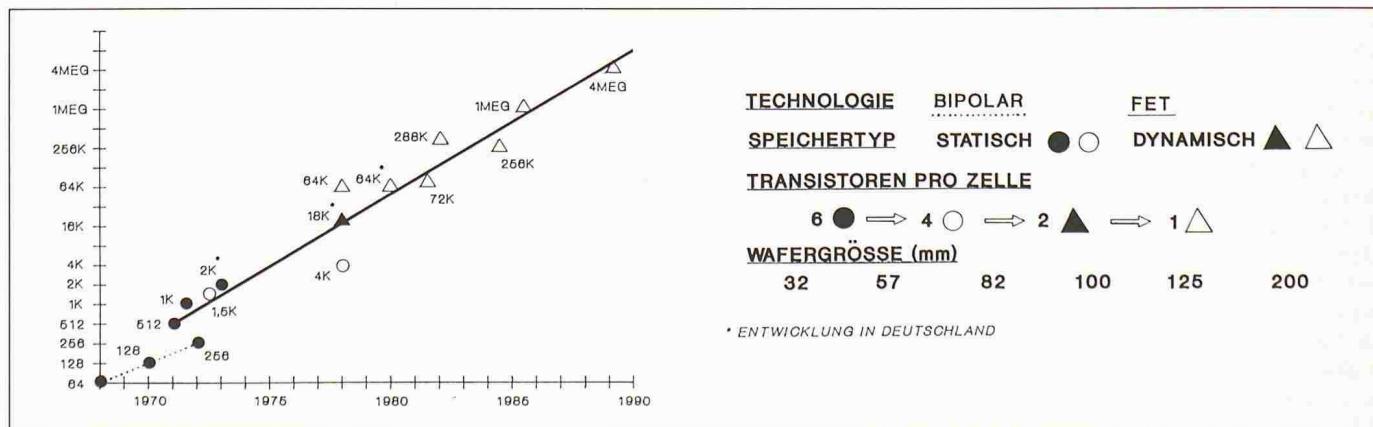

Die anfänglich erreichte Speicherdichte von 64 Bit (das entspricht acht Buchstaben) wurde im Laufe der vergangenen 20 Jahre auf den heutigen Stand von mehr als vier Millionen Bits pro Chip (das entspricht dem Inhalt von fast 300 Schreibmaschinenseiten) um mehr als das 65 000fache verbessert, eine Leistungssteigerung, die in keiner vergleichbaren Hochtechnologie je erreicht wurde (Bild 1). Die seit Ende 1985 auf der Basis der NMOS-Technologie (n-Kanal-Metal-Oxide-Semiconductor) laufende 1-Megabit-Chip-Produktion wurde während der letzten drei Jahre durch ständige systematische Prozessverbesserungen – auch bereits im

Vorgriff auf künftige, noch anspruchsvollere Produkte – weiterentwickelt. Sie stellt die Ausrüstung aller in Europa gefertigten IBM-Rechner, von der PS/2-Serie bis zu den Grosssystemen 3090, mit Speicherchips sicher.

## Neue Produktionsanlagen

### Investitionen

Die Gesamtinvestitionen für die 4-Megabit-Linie belaufen sich im Werk Sindelfingen auf rund eine halbe Milliarde Mark. Davon entfallen auf die neuen Fertigungsanlagen etwa 400 Millionen, auf die Gebäudeeinrichtungen ca. 100 Millionen. In die Reinräume allein wurden etwa 40 Millionen investiert. Ca. 50 Prozent der gesamten Investitionen kommen aus deutschen oder europäischen Ländern, etwa 42 Prozent aus den USA und ca. 8 Prozent aus Japan.

### Umweltschutz

Um die Grundlage des Produzierens zu gewährleisten, sind immer mehr auch Investitionen im Umweltschutz angebracht. Die Umweltschutzmassnahmen des Werkes Sindelfingen konzentrieren sich auf drei Schwerpunkte:

- Einsatz von umweltbelastenden Stoffen verringern

- Wiederaufbereitung oder Recycling

- Entsorgung

Ein neu erbautes Chemikalien-Lager zählt zu den sichersten Europas. Dafür wurden rund 20 Millionen Mark investiert. So wurde beispielsweise ein Auffangbecken für Löschwasser realisiert, damit – im Falle eines Falles – keine umweltbelastenden Chemikalien in das Grundwasser gelangen können. Der Verbrauch von FCKW-haltigen Substanzen wurde innerhalb der letzten 5 Jahre um 80 Prozent reduziert. In der neuen 4-Megabit-Linie wurden diese kritischen Substanzen vollkommen ersetzt.

In allen IBM-Werken in Deutschland wurden 1988 für den Umweltschutz 28 Millionen Mark investiert und zusätzlich 43 Millionen Mark für Umweltschutz-Betriebskosten ausgegeben. In der gleichen Zeit konnten aber auch 57 Millionen Mark durch Rohstoffrückgewinnung, also durch Recycling eingespart werden.

### Vermeidung von Defekten

Bei der Herstellung von 4-Megabit-Chips entscheiden Verunreinigungen in noch höherem Masse als beim 1-Megabit-Chip über Erfolg oder Misserfolg. Der Grund dafür ist einfach: Die Fläche einer einzelnen Speicherzelle beträgt nur noch ein Viertel. Die einzelnen Strukturen sind um ca. 30 Prozent kleiner geworden, d.h. ein menschliches Haar ist 100mal dicker als ein einzelner Leiterzug.

Dies führt zu extrem hohen Anforderungen an die Reinheit von Gebäuden und Anlagen. Deshalb wird in Reinräumen gearbeitet, die z. B. im Vergleich zur sehr sauberen Hochgebirgsluft ca. 100mal reiner ist. Die Grösse von Schmutzteilchen darf, wenn man es mal bildlich betrachtet, nicht grösser sein, als eine Erbse auf der Fläche eines

Bild 1. Entwicklung der Speicherdichte und Kenndaten der Chip-Entwicklung von 1968 bis 1990

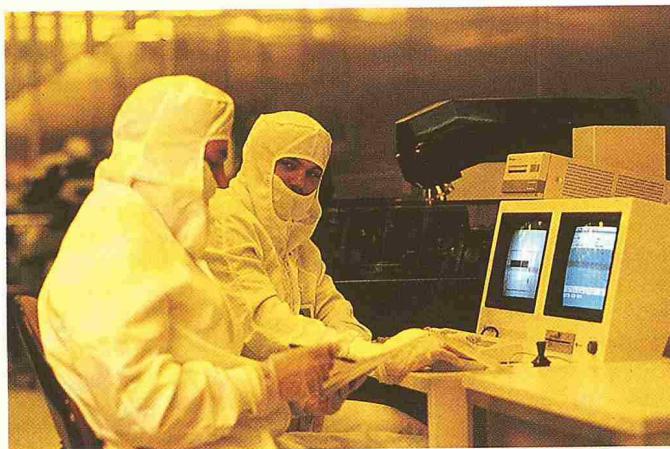

Bild 2. Gerät zur Dimensionsmessung von photolithographisch hergestellten Strukturen auf Siliziumscheiben (Wafern). Ein feinfokussierter Laserstrahl tastet die zu messende Struktur in horizontaler Richtung ab. In Serien von Messungen mit variabler Fokussierung wird das jeweils reflektierte Licht zur Bestimmung der Strukturprofile aufgenommen. Die Auflösungsgrenze beträgt (filmabhängig) 0,5 Mikrometer, bei einer Genauigkeit (nach Kalibrierung) von 10 Nanometer

Bild 3. Anlage zum nasschemischen Prozessieren der Fertigungslose von Siliziumscheiben, die mittels eines Roboters in eine Trommel beschickt werden. Durch von aussen angeordnete Düsen wird eine Reihe von Prozesschemikalien nach einem vorgeählten Programm auf die Scheiben gesprührt. Nach Beendigung des Nassätzens werden die Scheiben mit Wasser gespült und trocken geschleudert

Bild 4. Anlage zur Beschichtung von Siliziumscheiben mit lichtempfindlichem Photolack, aus Vorratsflaschen mit Partikelfiltern dosiert. Durch anschliessendes Abschleudern bei mehreren tausend Umdrehungen pro Minute wird eine von Lackviskosität und Drehzahl abhängige Lackdicke erreicht. Das folgende Backen der Scheiben auf Heizplatten entfernt überschüssiges Lösungsmittel aus dem Lack und stabilisiert dadurch den sich anschliessenden Photolithographieprozess

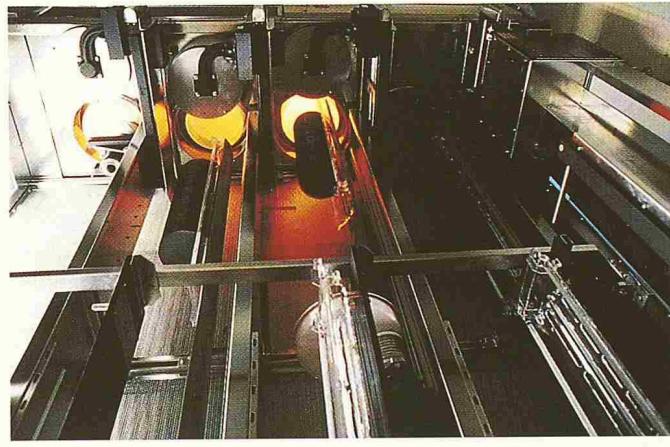

Bild 5. Im Heissprozess werden in vollautomatischen Öfen die Siliziumscheiben auf Quarzglasbooten bei Temperaturen zwischen 8000 und 11400 C oxidiert. Um Siliziumoxidlagen genau definierter Schichtdicke zu erhalten, wird die Ofentemperatur computergesteuert. Während des gesamten Oxidationsprozesses, der üblicherweise zwischen 3 und 5 und bis zu 15 Stunden dauert, variiert die Ofentemperatur um  $+/- 0,50$  C. Die vollautomatische Beschickung des Ofens hat zu einer wesentlichen Verringerung der Verunreinigungen der Wafer durch Partikel geführt, was eine hohe Produktqualität garantiert

Fussballfeldes. Die Dicke der Isolierschichten bewegt sich in einem Bereich von wenigen Atomlagen.

Das heisst, dass jede auch noch so kleine Verunreinigung zum totalen Ausfall des Chips führen kann. Ebenso wichtig wie die Einrichtung von Reinräumen ist es, die Partikel erst gar nicht entstehen zu lassen.

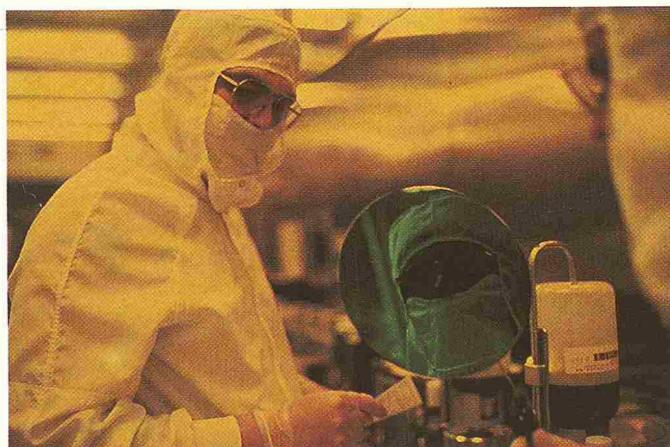

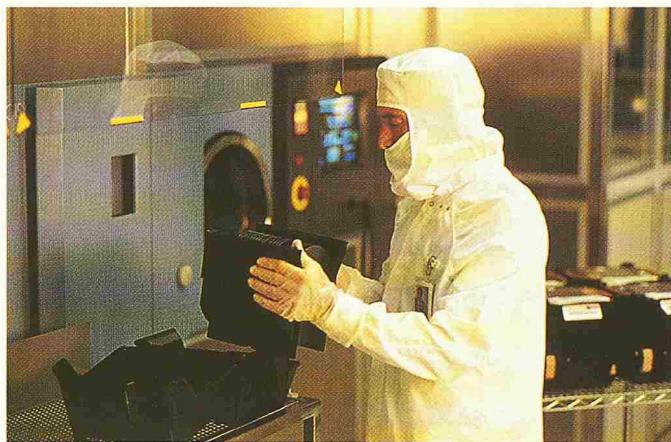

Potentielle Partikelerzeuger sind neben den Anlagen und Geräten auch eingesetzte Materialien und Chemikalien. Mit den Chemikalien-Lieferanten wurde hier z. B. eine Verbesserung um den Faktor 100 erreicht. Und nicht zuletzt muss auch vermieden werden, dass der Mensch zum Erzeuger von Partikeln wird. Deshalb tragen die Mitarbeiter

Reinraumkleidung, die der eines Chirurgen sehr ähnlich ist. Allerdings sind die Anforderungen an einen Operationssaal um den Faktor 100 geringer (Bilder 2 bis 10).

### Mitarbeiter der Zukunft

Die Spitzentechnologie der 4-Megabit-Fertigung und das hohe Innovationstempo in der Halbleitertechnologie fordern von allen Beteiligten eine ständige Weiterentwicklung von Kenntnissen und Fähigkeiten. Das erfordert Schulungsprogramme, mit denen Mitarbeiter auf neue, anspruchsvollere Qualifikationen vorbereitet werden.

Neben der Lernfähigkeit der einzelnen Mitarbeiter ist jetzt auch die Anpas-

sung der organisatorischen Strukturen eine notwendige Voraussetzung. Das Kernstück einer im vergangenen Jahr begonnenen Umgestaltung im Halbleiterbereich hatte zum Ziel, autonome Produktionseinheiten zu schaffen.

In diesen dezentralen Einheiten übernimmt ein Team aus Ingenieuren und Produktionsmitarbeitern eigenverantwortlich einen Prozessabschnitt. Sie sind dann für die Stabilität, Qualität und Optimierung der Prozesse verantwortlich: Dadurch werden organisatorisch Schnittstellen reduziert, der Produktionsprozess kann reibungsloser ablaufen, und die Durchlaufzeiten verkürzen sich. Dies ist auch notwendig, denn beim 4-Megabit-Chip ist die An-

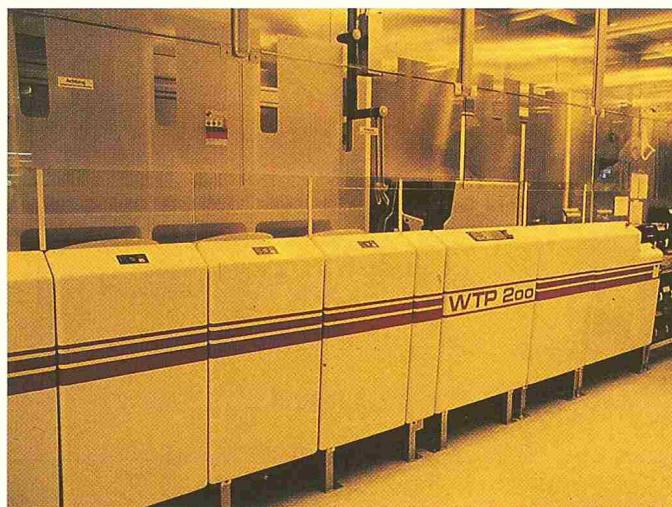

Bild 6. Die Reinigungsstation WTP (Wet Tank Processor) dient dem nasschemischen Prozessieren von Siliziumscheiben. Ein Roboter transportiert die Fertigungslose durch eine Reihe von Prozesstanks mit ätzenden oder Lack entwickelnden Chemikalien. Danach werden die Wafer mit Wasser gespült und in Schleudertrommeln getrocknet

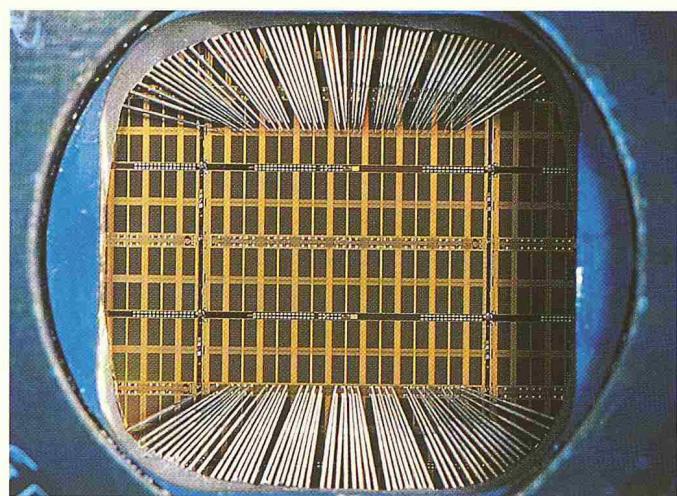

Bild 7. Chiptest. Beim dargestellten Funktionstest eines 4-Megabit-Speicherchips kontaktieren feinste Nadeln die Signalpunkte des Chips, um in kürzester Zeit alle 4 194 304 Speicherzellen zu überprüfen. Der Tester ist eine IBM-Entwicklung mit sehr schnellen Logik-Chips. Das System kalibriert sich automatisch, wobei sowohl DC-Werte (Spannung und Ströme) als auch AC-Werte (Pulsflanken, Pulsdauer und zeitliche Relation der Pulse untereinander) hochgenau eingestellt werden. Beim Wafertest können bis zu vier Chips gleichzeitig getestet, die Daten ausgewertet und zum Hostrechner übertragen werden

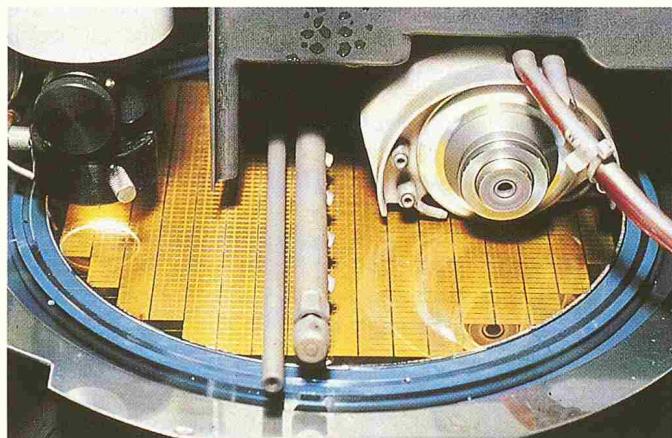

Bild 8. Für das Wafersägen dreht ein 0,06 mm dünnes, mit Diamantstaub beschichtetes Sägeblatt mit 25 000 bis 32 000 Umdrehungen pro Minute. Die Kühlung während des Sägevorgangs erfolgt mit bidestilliertem Wasser

Bild 9. Der gesägte Wafer wird auf eine Adhäsionsfolie aufgebracht, die ihn für die Dauer des Dicing- und Picking-Prozesses in einer exakten Position innerhalb des Hilfsramens aus magnetischem, nichtrostendem Stahl hält. Ein Barcode-Label auf dem Rahmen stellt den Bezug zwischen den Test- bzw. Pickingdaten des Logistiksystems in den verschiedenen Fertigungsschritten her

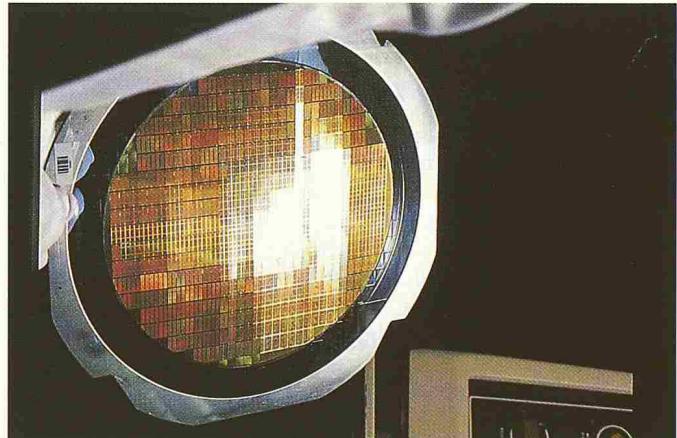

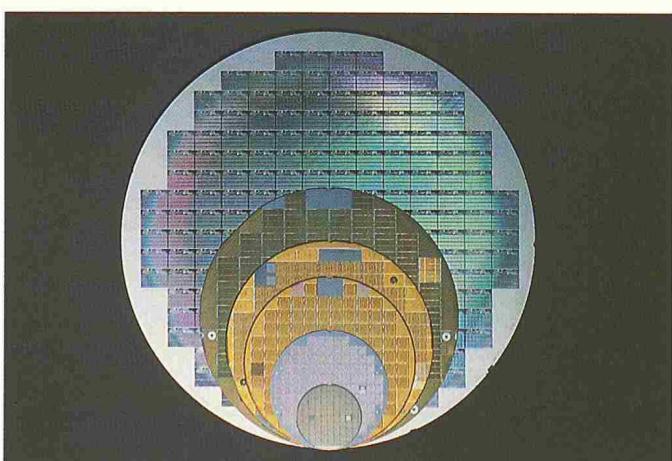

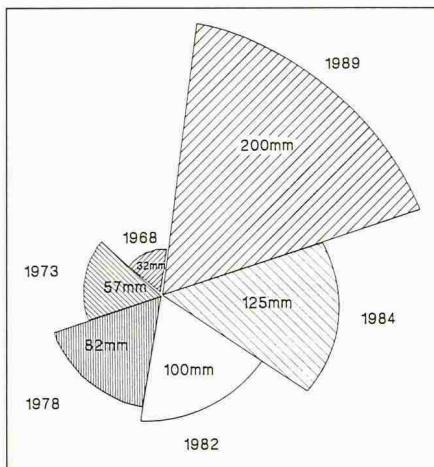

Bild 10. Wafer im Größenvergleich

| Jahr | Durchmesser | Speicherkapazität      |

|------|-------------|------------------------|

| 1968 | 32 mm       | 64 Bit                 |

| 1973 | 57 mm       | 2 000 Bit (2 KBit)     |

| 1978 | 82 mm       | 64 000 Bit (64 KBit)   |

| 1982 | 100 mm      | 288 000 Bit (288 KBit) |

| 1986 | 125 mm      | 1 000 000 Bit (1 MBit) |

| 1989 | 200 mm      | 4 000 000 Bit (4 MBit) |

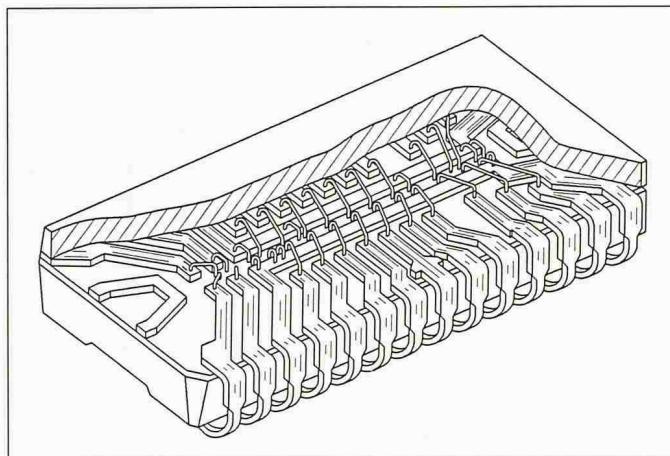

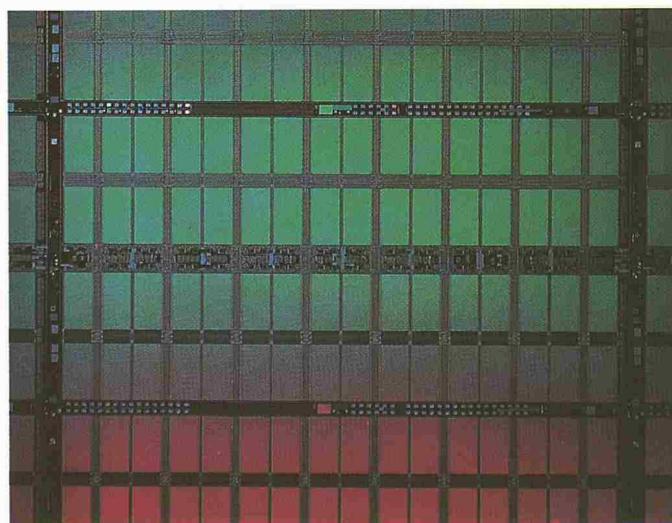

Bild 11. 4-Megabit-Substrat

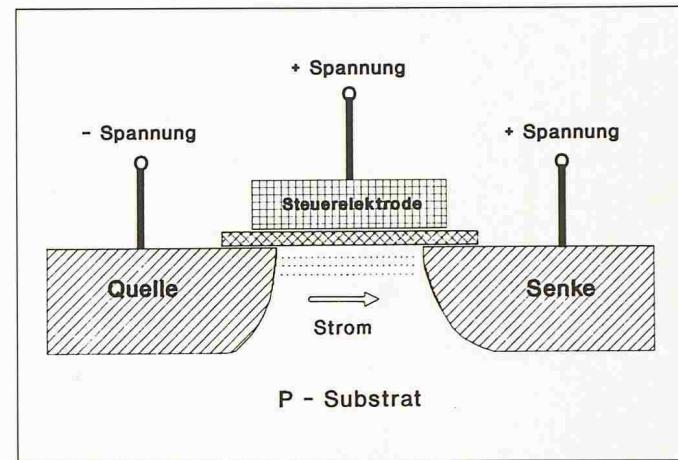

Bild 12. Feldeffekttransistor (FET)-Technologie

zahl der Prozessschritte um weitere 25 Prozent auf ca. 500 angestiegen.

Zusätzlich sind die Anzahl und Dauer der Prozessketten, die nicht unterbrochen werden können, gestiegen. Sie sind im Vergleich zum 1-Megabit-Chip um den Faktor 3 länger. Daher wird auch diese neue Linie im kontinuierlichen Betrieb gefahren.

## Produktbeschreibung

### Technische Daten

Betrugen die Chipabmessungen beim 1-Megabit-Chip 10,5 mm x 7,7 mm, so vergrösserten sie sich auf 13,1 mm x 6,6 mm beim 4-Megabit-Chip. Eine Speicherzelle auf dem 4-Megabit-Chip beansprucht einen Platz von 12 Quadratkilometer, die auf dem 1-Megabit-Chip 45 Quadratkilometer. Das bedeutet, dass ein Bit auf dem 4-Megabit-Chip nur noch etwa ein Viertel der Fläche benötigt, die es auf dem 1-Megabit-Chip beanspruchte. Daraus errechnet sich eine Steigerung der Dichte auf

mehr als 50 000 Speicherzellen je Quadratmillimeter beim 4-Megabit-Chip, verglichen mit 13 000 Speicherzellen je Quadratmillimeter beim 1-Megabit-Chip.

Der fertige Chip wird für die spätere Montage auf ein Substrat aufgebracht und mit einem Gehäuse hermetisch abgeschlossen. Aufgelötete Goldrädrchen verbinden den Chip mit den zwei Reihen von je 14 J-förmigen Anschlüssen (Pins), die Oberflächenmontage auf den Leiterplatten ermöglichen (Bild 11).

### FET-Technologie

Der neue 4-Megabit-Chip wird in FET-Technologie gefertigt, die bei IBM seit Beginn der 70er Jahre verwendet wird (Bild 12). Beim Feldeffekttransistor (FET) ist nur ein Ladungsträgertyp vorhanden. Man könnte ihn deshalb auch als unipolaren Transistor im Gegensatz zum bipolaren Transistor bezeichnen, an dem positive und negative Ladungsträger (Defektelektronen und Elektronen) beteiligt sind.

Die Wirkungsweise des FET beruht auf der Änderung der elektrischen Leitfähigkeit des Halbleiters durch ein äusseres elektrisches Feld, das durch eine Steuerelektrode erzeugt wird. Zwischen zwei gut leitenden Gebieten gleichen Ladungstyps (Quelle und Senke) liegt ein hochohmiges Gebiet, das Quelle und Senke voneinander isoliert. Legt man ein elektrisches Feld zwischen Quelle und Senke, so fliessst noch kein Strom. Man kann dieses Gebiet zwischen Quelle und Senke jedoch beeinflussen, indem man eine Spannung an die Steuerelektrode anlegt, die durch eine dünne dielektrische Schicht vom Halbleiter isoliert ist. Ab einer bestimmten Höhe dieser Spannung, der «Schwellspannung» des FET, beginnt ein Strom zwischen Quelle und Senke zu fliessen. Aufgrund dieser beiden Eigenschaften, «Strom» oder «kein Strom», lässt sich der FET als Schalter benutzen.

Gegenüber dem bipolaren Transistor hat der FET eine einfachere Struktur und erfordert deshalb weniger Herstellungsschritte. FET-Transistoren wer-

Bild 13. CMOS - Speicherzelle (Complementary Metal Oxid Semiconductor)

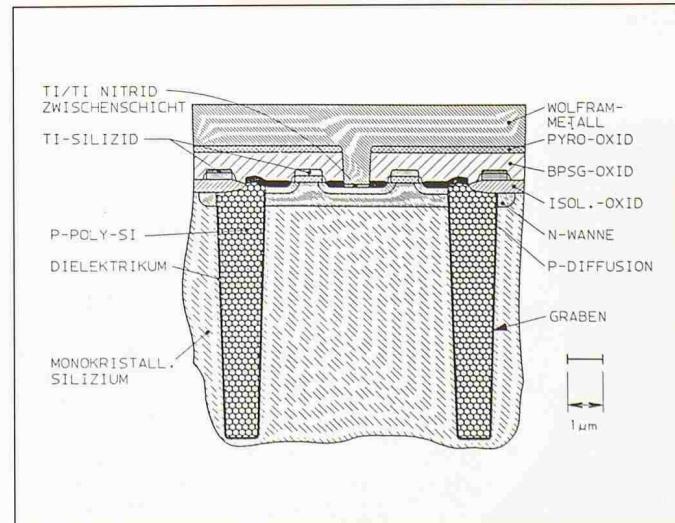

Bild 14. Querschnitt einer CMOS-Speicherzelle

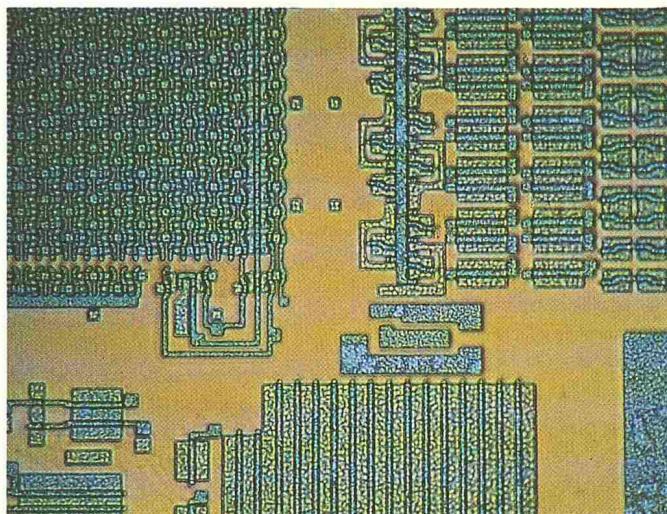

Bild 15. 4-Megabit-Chip; Makroaufnahme

Bild 16. Ausschnitt eines 4-Megabit-Chip im Massstab 1000:1

den hauptsächlich für Speicherschaltungen benutzt.

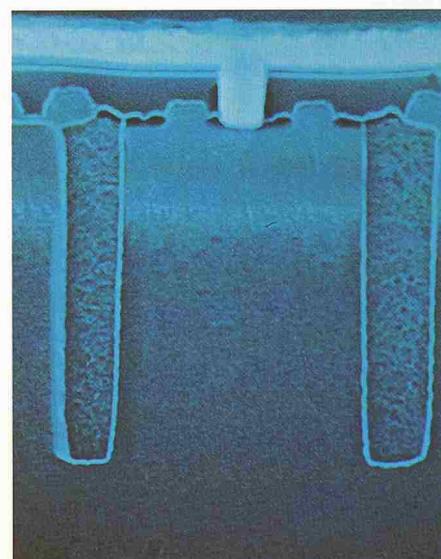

#### Prozesstechnologie für den 4-Megabit-Chip

Beim 4-Megabit-Chip verwendet IBM erstmalig die CMOS-Technologie (Complementary Metal Oxide Semiconductor, also die Benutzung von sowohl als auch p-Kanal-FETs auf demselben Chip), platzsparende, in die dritte Dimension gehende «Graben»-Strukturen als Speicher kondensatoren sowie eine wesentlich dichtere und zuverlässiger Verdrahtungstechnik auf dem Chip (Bilder 13 und 14). Die gleichzeitig eingeführte Vergrößerung der als Substrate benutzten Silizium-Scheiben (Wafer) von 125 mm auf 200 mm Durchmesser eröffnet ein erhebliches Produktivitätsgewinnpotential. Ein besonderer Vorteil der CMOS-Technologie ist eine gegenüber der früheren NMOS-Technologie wesentlich geringere Wärmeabgabe im Betrieb.

Die bei einem dynamischen Speicherchip elementaren Funktionen «Speichern» und «Abrufen» einer Information wurde bei allen früheren Technologien durch flächige, zweidimensionale «Platten»-Kondensatoren mit einer Schichtstruktur von siliziumisolierendem Dielektrikum-Metall (oder neuerdings Polysilizium) realisiert. Dies führte zu einem erheblichen Flächenverbrauch, der beim 1-Megabit-Chip noch durch geschickte Schaltkreisoptimierung aufgefangen werden konnte, beim dichteren 4-Megabit-Chip aber erst durch das Ausweichen in die dritte Dimension, d.h. durch das Ausbilden einer «Graben»-Platten-Kondensatorstruktur, gelöst werden konnte. Die erfolgreiche Herstellung dieser Struktur von etwa 7 Mikrometer Tiefe bei nur

0,7 Mikrometer Breite setzt präzise Profilkontrolle beim Ätzen, das defektfreie Aufwachsen einer nur etwa 10 Nanometer (1 Nanometer = 1 Milliardstel Meter) dicken, isolierenden dielektrischen Schicht und das Füllen des Grabens mit einer weiteren, leitenden Schicht voraus.

Die zweite wesentliche Änderung in der Prozesstechnik betrifft die «Verdrahtung» der bereits hergestellten Transistoren durch metallische Leiterbahnen auf dem Chip selbst. Für die nun insgesamt fast 20 Meter langen Leiterzüge auf einer Fläche von weniger als 100 Quadratmillimeter waren beträchtliche Verbesserungen in der Defektfreiheit und Zuverlässigkeit notwendig. Verwirklicht wurde dies durch die Nutzung neuer, den Kontaktübergangswiderstand reduzierender Metallschichtstrukturen in Form von Titan/Titan-Nitrid-Lagen, durch selbstplanarisierende Metallabscheidungsprozesse aus der Gasphase (hier Wolfram-Silicid/Wolfram) sowie durch defektfreie-

re Isolationsschichten zwischen den Verdrahtungsebenen – ebenfalls erzeugt durch Gasphasenabscheidung von Silizium-Oxiden bzw. Silizium-Nitriden.

Die grundsätzliche Aufgabe, vor der sich die Technologie zur Fertigung von Halbleiterspeichern von Anfang an gestellt sah, bestand und besteht darin:

- Motive (Pattern) des Chips in immer feinere Strukturen aufzulösen, wobei gleichzeitig auch die Defekte nach Grösse und Anzahl immer weiter reduziert werden müssen (Bilder 15 und 16). Seit 1970 hat sich die Grösse des kleinsten Motivs von 4,5 Mikrometer auf 0,7 Mikrometer verringert.

- Einen immer komplexer werdenden Fertigungsprozess zu beherrschen.

Die Prozesskomplexität hat sich – zieht man nur die Anzahl kritischer Prozesse in Betracht – von 1970 bis heute fast vervierfacht (Tabelle 1). Die Summe aller Prozesse beträgt beim 4-Megabit-Chip ungefähr 500.

| Kleinste Motiv             | (Mikrometer) |     |     |     |     |

|----------------------------|--------------|-----|-----|-----|-----|

|                            | 3,5          | 2,5 | 1,5 | 1,0 | 0,7 |

| <b>Prozess-Komplexität</b> |              |     |     |     |     |

| Photo-Prozesse             | 6            | 10  | 11  | 11  | 13  |

| Heiss-Prozesse             | 6            | 5   | 6   | 8   | 10  |

| Ionen-Implantationen       | -            | 2   | 4   | 8   | 8   |

| CVD-Prozesse               | -            | 3   | 3   | 5   | 17  |

| Metall-Lagen               | 1            | 2   | 2   | 2   | 2   |

| <b>Kritische Prozesse</b>  |              |     |     |     |     |

|                            | 13           | 22  | 26  | 34  | 45  |

Tabelle 1. Vermehrung der kritischen Prozesse bei der Chip-Herstellung von 1968 bis 1990

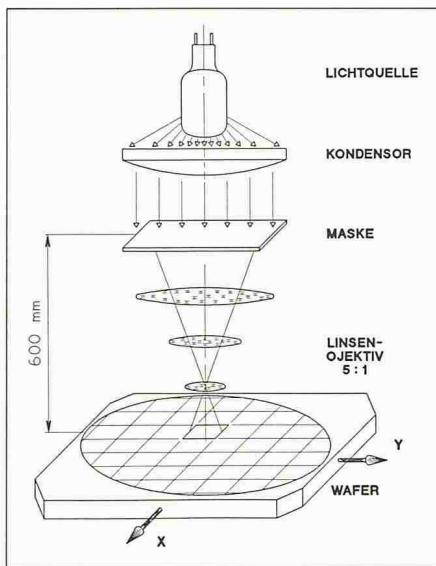

Bild 17. Step- und Repeat-Belichtungsprinzip

Neben der Zunahme von Anzahl und Komplexität der Prozesse wurden auch einige dieser Prozesse gegenüber früheren Verfahren grundlegend geändert. Vergleicht man beispielsweise die Produktion der 4-Megabit-Chips mit der des 1986 erstmals gefertigten 1-Megabit-Chips, so lassen sich in den drei Hauptprozessbereichen

- Photolithographie

- Filmabschneidungs- und Ätzprozesse

- Dotierungs- und Heissprozesse

folgende Verbesserungen feststellen:

### Photolithographie

Die Verkleinerung der Dimensionen erforderte beträchtliche technologische Verbesserungen in der Photolithographie. Dazu gehört einmal beim Photolack selbst die Umstellung von lösungsmittelentwickeltem Negativ-Photolack auf nasschemisch entwickelten Positivlack, weil nur dieser kleine Motive maszkendimensionsgerecht wiedergeben kann.

Zur Auflösung dieser kleinen Motive benutzt man jetzt sogenannte «Step-and-Repeat»-Kameras, die eine fünf-

mal vergrößerte Vorlage verwenden und dieses Muster auf die Wafer projizieren (Bild 17). Bei jedem Belichtungsvorgang werden zwei Chips auf den Wafer belichtet. Danach fährt ein steuerbarer x-y-Koordinatentisch mit dem Wafer zur nächsten Chip-Position, und die nächste Belichtung erfolgt. Um die erforderliche Positioniergenauigkeit zu erreichen, verwendet man ein Laserinterferometer zur Steuerung des Koordinatentisches, der eine Schrittgenauigkeit kleiner als 50 Nanometer hat.

Für die Produktion des 4-Megabit-Chips wurde diese Technik des Projektionsbelichtens konsequent weiterentwickelt und verfeinert. Durch verbesserte optische Linsensysteme mit erhöhter Auflösung und die Kombination mit genaueren Justiertechniken sowie durch die Einführung empfindlicher Photolacke gelang die Reduzierung der Strukturbreiten auf 0,7 Mikrometer und die Erhöhung der Justiergenauigkeit auf 0,25 Mikrometer. Entsprechend mussten auch die Prozesstoleranzen verkleinert werden.

Als Masken für das 5:1-Projektionsbelichten werden, wie auch beim 1-Megabit-Chip, Chrommasken auf Quarzsubstraten mit sehr hohem Kontrast und damit guter Motivqualität verwendet.

Die Herstellung der Masken selbst erfolgt vollautomatisch mit Elektronenstrahl-Belichtungssystemen, die direkt mit den Entwurfsdaten aus den Laboratorien gesteuert werden. Für den 4-Megabit-Chip werden diese Daten aus dem Laboratorium Burlington ins Werk Sindelfingen übertragen, dort gespeichert und in Steuerdaten für das Elektronenstrahl-Belichtungssystem umgesetzt. Gegenüber den früheren Mustergeneratoren, die zur Herstellung einer fehlerfreien Maske mehrere Tage benötigten, lässt sich mit Elektronenstrahl-Belichtungssystemen diese Zeit wesentlich verkürzen. Anspruchsvolle Masken werden heute mit einem Elektronenstrahl von 0,2 Mikrometer Durchmesser in wenigen Stunden fehlerfrei und mit hoher Bildqualität geschrieben.

### Filmabscheidungs- und Ätzprozesse

Beim 4-Megabit-Prozess wird die gesamte Palette der bekannten Techniken verwendet. Ein besonders eindrucksvolles Beispiel ist dabei die komplexe Folge von zehn Filmabscheidungs- und Ätzprozessen, die notwendig sind, um den dreidimensionalen «Graben»-Platten-Kondensator herzustellen (Tabelle 2). Die verwendeten Filmtypen reichen dabei von dielektrischen Silizium-Oxid/Nitrid-Schichten mit extrem geringen Dicken von nur 10 Nanometer an den Seitenwänden dieses Grabens bis hin zu der leitenden polykristallinen Silizium-Schicht von etwa 0,5 Mikrometer Dicke, die den Graben als «zweite Platte des Kondensators» auffüllt. Der Schlüssel zum Erfolg liegt in der Beherrschung der defektfreien Herstellung dieses nur wenige Atomlagen dicken Dielektrikums in den nur 0,7 Mikrometer breiten, aber 7 Mikrometer tiefen Gräben.

Die zweite wesentliche Neuerung der Filmtechnologie im 4-Megabit-Prozess konzentriert sich auf den Bereich der elektrischen Verdrahtung der Transistoren untereinander auf dem Chip mit Hilfe von metallischen Filmen, die durch Photolithographie und Trockenätztechniken strukturiert werden.

Der grundsätzlichen Schwierigkeit, dass bei immer kleiner werdenden Dimensionen die beiden Problemkreise «geringere Strombelastbarkeit immer dünnerer Metalleiter» und «größere mechanische Empfindlichkeit der Leiterzüge beim »Überqueren« der Berg- und Talstruktur der fertigen Transistoren» zu wesentlich geringerer Ausbeute und einer kürzeren Lebensdauer führen, geht man durch die Verwendung neuer Filme und sogenannter selbstplanarisierender Abscheide- und Ätztechniken aus dem Weg. Dazu benutzt man beim 4-Megabit-Chip für die erste Verdrahtungsebene eine aus der Gasphase abgeschiedene Wolfram-Metallschicht, die dabei gleichzeitig die Topologie der zu den Transistoren führenden Kontaktlöcher auffüllt und einebnet. Durch den Wechsel zu Wolfram war gleichzeitig – sowohl aus Filmhaftfähigkeitsgründen als auch zum Erzielen guter Kontaktübergangswiderstände – eine Vielfachschichtstruktur von Titan/Titan-Nitrid/Wolfram/Wolfram-Silicid-Lagen zwischen Transistor und Metalleiter notwendig.

### Dotierungs- und Heissprozesse

Die Heissprozesse, die dritte Sektion, werden zum Einstellen der Dotierungsprofile sowie zum Bilden von Oxidschichten durch die Oxidation von Silizium verwendet.

|                   | Filmtyp      | Schichtdicken | Technik                                                                |

|-------------------|--------------|---------------|------------------------------------------------------------------------|

| <b>Abscheiden</b> |              |               |                                                                        |

| Isolierend        | Si-Oxid      | 10µm-1,0µm    | Thermische Oxidation<br>Chemische Gasphasenabscheidung                 |

|                   | Si-Nitrid    | 10µm-0,5µm    | Chemische Gasphasenabscheidung<br>Plasmagestützte Gasphasenabscheidung |

| <b>Leitend</b>    |              |               |                                                                        |

|                   | Polysilizium | 0,5µm         | Chemische Gasphasenabscheidung                                         |

|                   | Ti/Ti Nitrid | 0,1µm         | Kathodenzerstäubung                                                    |

|                   | WSix/W       | 0,7µm         | Chemische Gasphasenabscheidung                                         |

|                   | Al (Cu,Si)   | 1,0µm         | Kathodenzerstäubung                                                    |

| <b>Ätzen</b>      |              |               |                                                                        |

|                   | Alle Filme   |               | Reaktives Ionenätzen                                                   |

Tabelle 2. Filmabscheidungs- und Ätztechniken beim 4-Megabit-Prozess

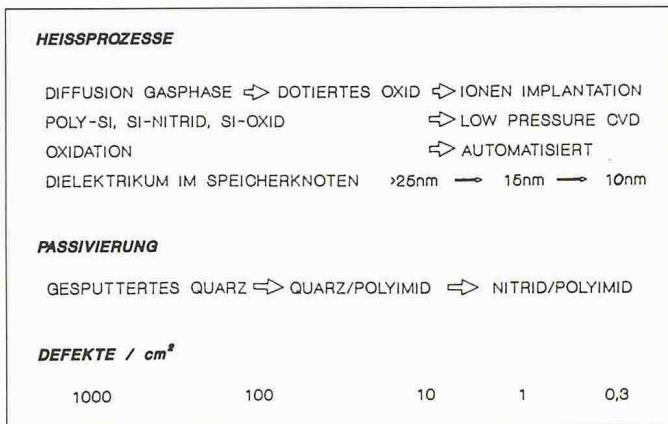

Bild 18. Technologieentwicklung der Dotierungs- und Heissprozesse

Bild 19. Dotierungs-Technologie: Ionen-Implantation

Die Verkleinerung der Speicherzellen beim 4-Megabit-Chip wirkt sich auch auf Flächen und Dicken der aufzubringenden Schichten im Fertigungsprozess aus. Lag die Dicke der dünntesten Schichten beim 64-KBit-Chip noch bei 25 Nanometern, so ist sie beim 4-Megabit-Chip bis auf 10 Nanometer zurückgegangen. Dies erfordert Veränderungen und Verbesserungen der im Fertigungsprozess verwendeten Verfahren, um vor allem die Gleichmässigkeit der aufzuwachsenden Schichten zu gewährleisten. (Bild 18)

Die konventionellen Diffusionsprozesse aus der Gasphase wurden Ende der 70er Jahre vollständig auf das moderne Verfahren der Ionen-Implantation umgestellt, mit der sich eine wesentlich exaktere Dotierung erreichen lässt (Bilder 19 und 20). Bei der Ionen-Implantation «schießt» man beispielsweise Bor-Ionen als gerichteten Ionenstrahl direkt in das Kristallgitter des Siliziums. Dieser Vorgang läuft im Vakuum bei hohen elektrischen Spannungen ab.

Mit der Ionen-Implantation erhält man durch den anisotrop ablaufenden Vorgang weniger horizontale Streuung als beim früheren Diffusionsprozess und damit gleichmässigere und flexiblere gestaltende Dotierungsprofile. Dadurch lässt sich dichter packen, die Störkapazitäten werden kleiner, und die Signale der einzelnen Transistoren werden grösser. Die beim 4-Megabit-Prozess teilweise notwendigen Beschleunigungsspannungen von weit über 1 Million Volt stellen grosse Anforderungen an die dazu verwendeten –

fast schon an Hochenergiephysikgeräte erinnernden – Maschinen, die mittlerweile in der Fertigungsline Flächen von mehr als 100 Quadratmeter je Anlage beanspruchen.

### Produktivitätssteigerung durch grössere Wafer

Die Herstellkosten des fertigen Wafers bei gegebener Technologie sind nahezu unabhängig von seinem Durchmesser und von der Anzahl der auf ihm befindlichen Chips. Die Bedeutung der Wafergrösse für die Wirtschaftlichkeit der Fertigung liegt deshalb auf der Hand. Der Durchmesser der Wafer hat sich während der Halbleitergeschichte des Werkes Sindelfingen von anfangs 32 mm auf heute 200 mm vergrössert (Bilder 21 und 22).

Dies entspricht einer 40fachen Vergrösserung der Waferoberfläche. IBM ist weltweit der erste Halbleiterproduzent, der diese Wafergrösse realisiert hat.

Gerätetechnisch bedeutet der Übergang auf den grösseren Wafer eine von Grund auf neu ausgerüstete Fertigungsline, da alle bisher verwendeten Anlagen für Wafer mit einem Durchmesser bis maximal 150 mm ausgelegt waren. Mit der Umstellung liessen sich gleichzeitig in vielen Fällen entscheidende Verbesserungen miteinbeziehen, die zu kleineren Prozesstoleranzen und geringeren Defektdichten der Anlagen führten.

Bei mehr als 50 Prozent der Geräteinvestitionen in der neuen Fertigungsli-

nie konnte auf die hervorragende Kompetenz und Kooperation deutscher und europäischer Hersteller zurückgegriffen werden

### Defektreduzierung für wirtschaftliche Ausbeuten

Letztlich entscheidet beim 4-Megabit-Chip das Beherrschen von Defekten über Erfolg oder Misserfolg der Produktion.

«Gute Ausbeute» verlangen eine totale Kontrolle der Defekte in allen kritischen Schritten der Fertigung. Beim 4-Megabit-Chip stören heute nahezu

Bild 20. Anlage der Ionen-Implantation

Bild 21. Entwicklung der Wafer-Größen (Siliziumscheiben) seit 1968

alle Schmutzpartikel, die man bei früheren Chips noch tolerieren konnte. Die kleinste horizontale Abmessung liegt beim 4-Megabit-Chip bei 0,7 Mikrometer. Die Grösse der auftretenden Partikel darf deshalb 0,3 Mikrometer nicht überschreiten.

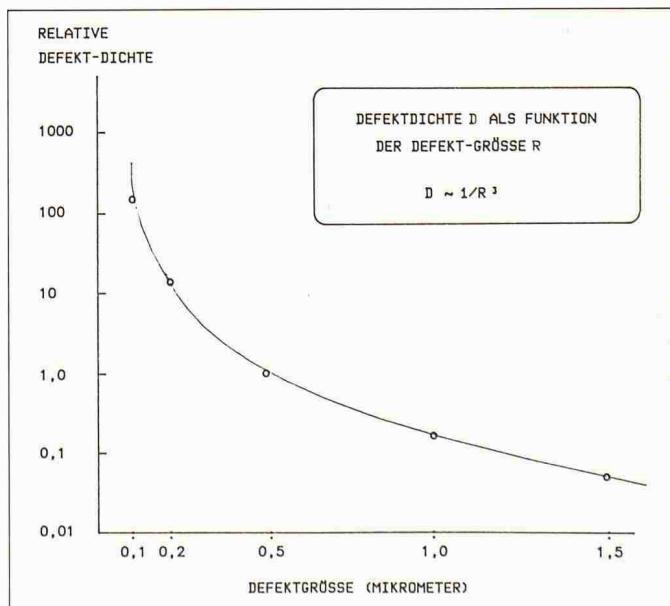

Noch kritischer ist die Empfindlichkeit in der Vertikalen. Hier können beim 4-Megabit-Chip schon Partikel, die 0,1 Mikrometer oder kleiner sind, Kurzschlüsse im Speicher kondensator, dessen Dielektrikum nur noch wenige Atomlagen dick ist, hervorrufen. Diese Kleinstpartikel sind aber rund 100mal häufiger anzutreffen als 0,5 Mikrometerpartikel (Bild 23).

Um Defekte zu vermeiden, muss man die «Erzeuger» solcher Partikel kennen. Es sind dies unter anderem:

- die Prozesseinrichtungen, beispielsweise zum Belichten, Implantieren oder Bedampfen des Wafers,

- die verwendeten Prozessmedien wie

Gase, Chemikalien oder Reinstwasser,

- die Staubpartikel in der Umgebungs luft der Prozessräume, d.h. der Rein räume, der Werkbänke oder der Transportbehälter

- der Mensch selbst beim Transportieren, Messen oder Inspizieren der Wafer.

### Reinräume

Für Halbleiterprozesslinien wird aus den genannten Gründen ein abgestuftes Konzept von Reinraumzonen benutzt und der höchste Reinheitsgrad dort vorgesehen, wo die Wafer «offen» transportiert und bearbeitet werden müssen. Es herrscht hier eine Reinraumklasse 1, d.h. in 28 Liter Volumen Luft darf nur weniger als ein Partikel, das grösser als 0,5 Mikrometer ist, vorkommen. Das entspricht gegenüber der Aussenluft einer um den Faktor 10 Millionen oder gegenüber einem heute üblichen hochsterilen Operationssaal um den Faktor 100 reineren Luft.

### Automatisches Handhaben und Prozessieren

Eine weitere Hauptquelle für das Entstehen von störenden Partikeln in Prozesslinien sind die dort tätigen Mitarbeiter. Ein Teil der Partikelabgabe durch den Menschen – vor allem von der Haut, den Haaren, beim Atmen und Sprechen – wird durch das Tragen von Reinraumanzügen sowie von Kopfhauben, Mundschutz und Handschuhen ähnlich wie in Operationssälen unterdrückt. Den grösseren Teil der entstehenden Defekte kann man jedoch erfolgreich vermeiden, wenn man den Kontakt zwischen Mensch und Wafer durch automatisches Handhaben und Prozessieren ganz ausschliesst.

### Produkt-Charakterisierung

Der frühe Erfolg mit dem 4-Megabit-Chip im Werk Sindelfingen beruht nicht zuletzt auf der grossen Produktionserfahrung, die das Werk in mehr als zwanzig Jahren sammeln konnte. Dabei wurde gelernt, Produkt- und Prozessparameter gezielt zu steuern, in einem kontinuierlichen Lernprozess zu verbessern und vor allem Defekte konsequent zu vermeiden

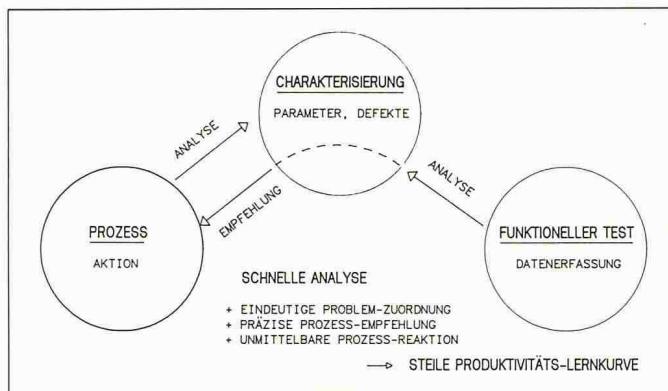

Voraussetzung für diese ständige Optimierung ist das lückenlose Sammeln und Auswerten von Testdaten, die «Charakterisierung» eines Produktes. Damit ist der Status einer Halbleiterfertigung exakt zu bestimmen (Bild 24).

### Erfassen von Funktionsdaten auf dem Chip

Zum Erfassen von Funktionsdaten benutzt man sowohl die sogenannten «Kerfs» als auch die Chips selbst. Kerfs sind die Abstandsfächen zwischen den einzelnen Chips, die beim Zerschneiden des Wafers in Einzelchips zerstört werden. Diese Kerfs enthalten Teststrukturen, mit denen rund 300 verschiedene Tests beim 4-Megabit-Chip vorgenommen werden. Etwa die gleiche Anzahl von Tests erfahren auch die Zellen auf den Chips.

Es ist wichtig, dass die Wafer nach jeder Bearbeitungsstufe überprüft werden. Hierbei sind die Testbedingungen am Anfang der Fertigung besonders scharf, um nicht defekte Wafer durch die Produktion zu ziehen und sie am Ende doch «verschrotten» zu müssen. Damit lassen sich auch fehlerhafte Bearbeitungsprozesse rechtzeitig erkennen, ehe zu viele Wafer davon betroffen werden.

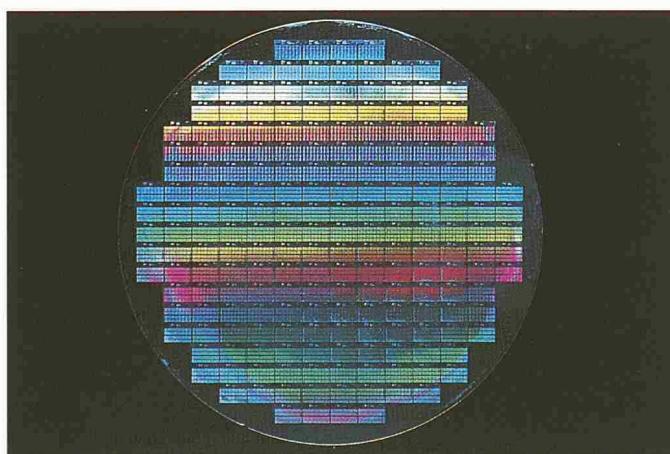

Bild 22. IBM-Wafer mit 4-Megabit-Chips

Bild 23. Defektdichte D als Funktion der Defektgrösse R(D 1/R^3)

Bild 24. Produktcharakterisierung durch Sammeln und Auswerten der Testdaten während der Produktion

Bild 25. Produktivitäts-Lernkurve in der Halbleiterfertigung

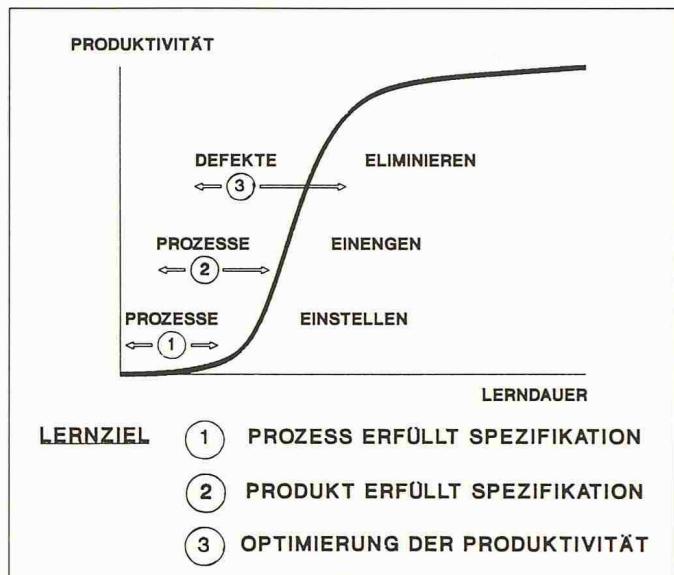

### Produktivitätslernkurve

Bei der «Charakterisierung» eines Wafers geht es darum, sowohl alle bei den kritischen Prozessen anfallenden Parameter als auch die bei den einzelnen Zwischentests nach jeder Bearbeitungsstufe festgestellten Defekte zu erfassen. Bei einigen dieser Zwischentests erfolgt außerdem eine Überprüfung der Chip-Funktionen. Die anschliessende Analyse dieser Daten führt schnell zur Identifizierung etwaiger Probleme und zu präzisen Vorgaben zur Verbesserung der Prozesse. Dieses unmittelbare Rückkoppeln ist entscheidend für eine steile Produktivitätslernkurve.

Geht es in der Anfangsphase einer Produktion darum, die einzelnen Prozesse

so einzustellen, dass die vorgegebenen Spezifikationen erfüllt werden können, so kommt es in der zweiten Stufe darauf an, die Toleranzen der einzelnen Parameter einzuschränken, um schliesslich in einer dritten Stufe Defekte zu eliminieren (Bild 25).

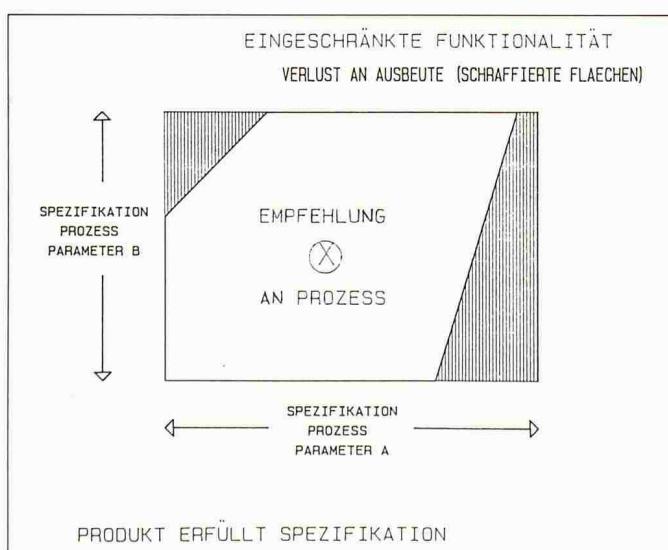

In der zweiten Stufe ermittelt man das sogenannte Prozessfenster. Es ist quasi eine Kombination von in der Produktion beherrschten physikalischen Parametern, die eine hohe Ausbeute gewährleisten. Die «Vorhänge» (schraffierte Flächen in Bild 26) sind Zonen eingeschränkter Funktionalität. Das Festlegen eines optimierten Prozessfensters ist das wesentliche Ergebnis der

Stufe zwei in der Produktivitätslernkurve.

Der gesamte Lernprozess verläuft um so kürzer, je mehr sich das neue Produkt evolutionär aus einem schon ausgereiften Produktionsprogramm entwickeln kann.

Für die Dauer des Lernprozesses ist die Effektivität der Datenanalyse der Vorgaben an den Prozess und die Reaktion des Prozesses entscheidend. Hier zeigt sich, dass die Ausbeute an guten Chips fast ausschliesslich von der Perfektion der Parameter und Defekt-Kontrolle in der Fertigung abhängt. Der Charakterisierung kommt damit eine Schlüsselstellung in der Halbleiterfertigung des Werkes Sindelfingen zu.

Bild 26. Prozessfenster für Spezifikationserfüllung eines Produktes in der Relation zwischen den Spezifikationen zweier Prozessparameter

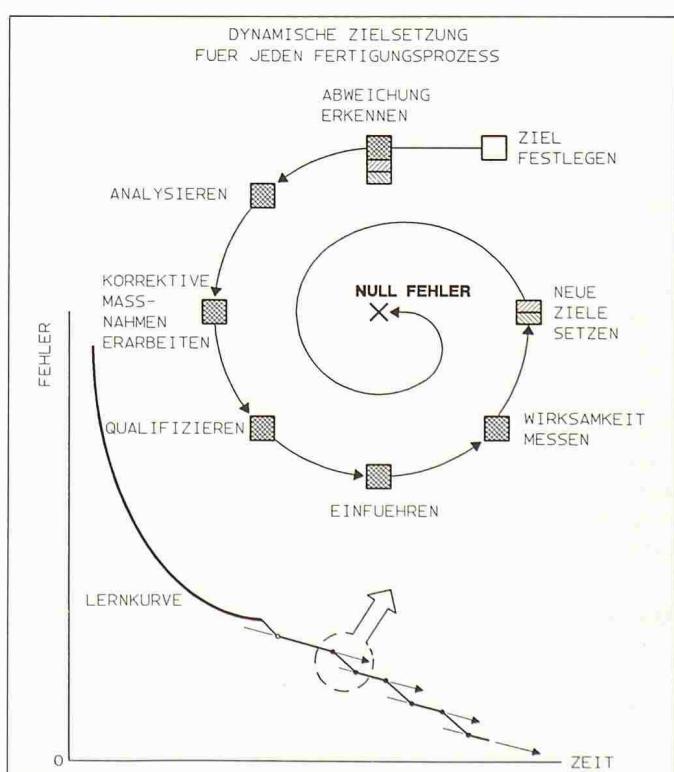

Bild 27. «Qualitätsspirale» in der Null-Fehler-Strategie

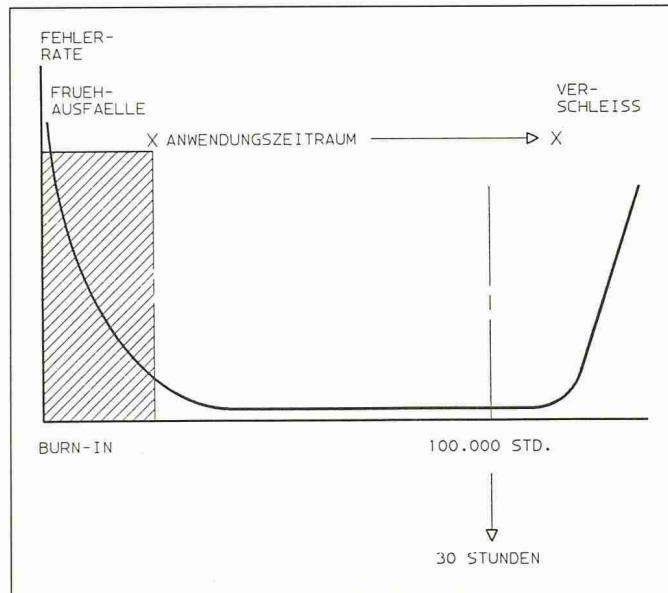

Bild 28. Simulation des Zuverlässigkeitserhaltens durch «Burn-in» (erhöhte Temperatur- und Spannungsbelastung während 30 Stunden in Simulation des Anwendungszeitraums von 100 000 Stunden)

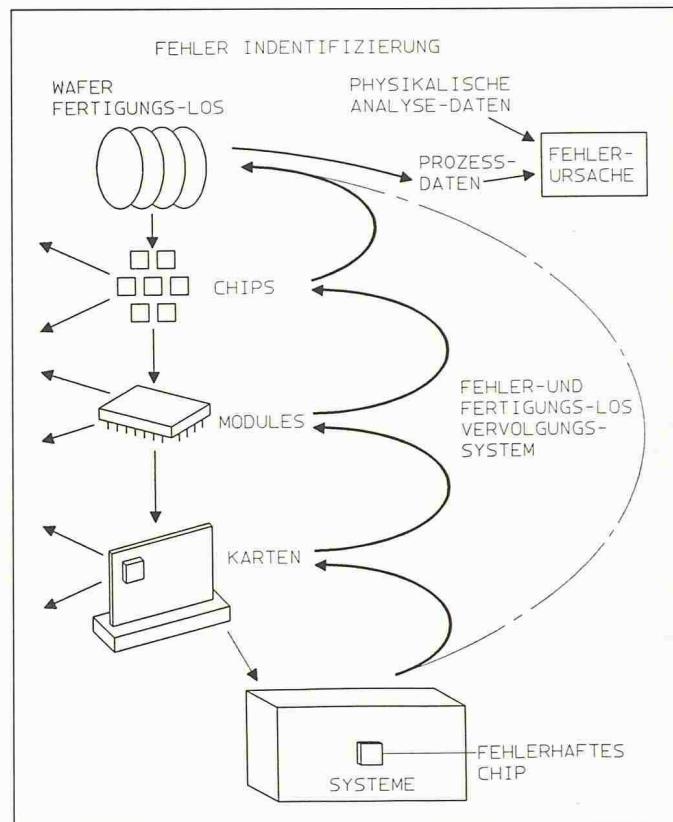

Bild 29. Qualitätssicherung durch Rückkopplung der statistischen Auswertung von Testdaten des Fehler- und Fertigungslos-Verfolgungssystems zum Herstellungsverfahren

### Der dynamische Zielsetzungsprozess

Dem Ziel «Null Fehler» kann man nur über einen dynamischen Zielsetzungsprozess nähern. Dabei werden erreichten Ergebnissen neue, weiterreichende, aber zu bewältigende Ziele gegenübergestellt, die das Produkt immer näher an den Zustand «Null Fehler» bringen.

Der Status «Null Fehler» lässt sich in einem Prozess nicht auf Anhieb erreichen. Man folgt einer «Qualitätsspirale» (Bild 27), in deren Mittelpunkt sich das angestrebte Ziel «Null Fehler» befindet. Ihre Windungen sind dadurch gekennzeichnet, dass aus allen gegebenen Abweichungen vom Soll zunächst das schwerwiegendste Problem angegangen und gelöst wird, ehe in der nächsten Windung das dann dominierende Problem zur Lösung ansteht. Bei jedem Durchlauf einer Windung ist es erforderlich, alle verfügbaren Daten und Erkenntnisse zu berücksichtigen, wenn es um die Problemanalyse, das Festlegen korrekter Massnahmen und um die Beurteilung der Ergebnisse geht.

### Der elektrische Endtest der Chips

Der elektrische Endtest ist ein Mass für die Qualität der Fertigung.

Die im produzierten Wafer werden auf volle Funktionsfähigkeit getestet, dann in Einzelchips zersägt und die guten Chips computergesteuert aussortiert. Anschliessend gelangen die Chips zur Weiterverarbeitung zu Modulen, d.h. sie werden auf Substrate aufgelötet und mit einem Gehäuse hermetisch abgeschlossen.

Der Test der fertigen Wafer und später auch die Prüfungen der mit Chips bestückten Modulen und Karten erfolgt mit computergesteuerten, bei IBM entwickelten Testsystemen.

Der Speicher-Endtest, bei dem jede Speicherzelle einzeln überprüft wird, beinhaltet u.a. folgende Hauptfunktionen:

Messen der Leck- und Versorgungsströme sowie der Speicherfunktionen. Damit wird der vorgegebene Anwendungsbereich garantiert. Dieser Test läuft auf Wafer- und Modulebene ab.

Variation von Spannung, Temperatur, Impulsformen und Datenmustern sowie spezielle Grenzwerttests. Damit wird die Funktionsfähigkeit aller Speicherzellen überprüft. Diese Prüfungen erfolgen sowohl beim Wafer- als auch beim Modultest.

Dynamisches, sogenanntes «Burn-in» (Einbrennen) mit erhöhter Temperatur und erhöhter Spannung (nur auf Modul-Ebene). Während dieses Stresstests, der

wesentlich zu einer hohen Zuverlässigkeit der Produkte beim Kunden beträgt, wird das Modul funktionell betrieben. Dem «Burn-in» unterliegen alle auf Speichermodulen montierten Chips (Bild 28).

### Qualitätssicherung

Die Speicherung von Prozess- und Testdaten in zentralen Datenbanken ermöglicht eine statistische Auswertung der Testdaten und die Rückkopplung zum Herstellungsverfahren des 4-Megabit-Chips. Selbst beim Kunden auftretende Fehler lassen sich mit einem aufwendigen Logistiksystem in den meisten Fällen eindeutig bestimmten Prozessschritten und den Prozessbedingungen dieses Chips zuordnen, so dass korrigierende Massnahmen angestossen werden können (Bild 29). Damit lassen sich Ausbeute und Zuverlässigkeit in der Chip-Produktion weiter optimieren.

Adresse des Verfassers: Klaus Kuhnle, Leiter Werk Sindelfingen, IBM Deutschland GmbH, Postfach 80 08 80, D-7000 Stuttgart 80.