**Zeitschrift:** Helvetica Physica Acta

**Band:** 41 (1968)

**Heft:** 6-7

**Artikel:** Ein Analogverfahren zur Berechnung der Eigenschaften von

Feldeffekttransistoren

Autor: Drangeid, K.E. / Sommerhalder, R.

**DOI:** https://doi.org/10.5169/seals-113926

# Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. Mehr erfahren

## **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. En savoir plus

#### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. Find out more

**Download PDF:** 05.12.2025

ETH-Bibliothek Zürich, E-Periodica, https://www.e-periodica.ch

magnetic order and if in addition W=0, one reobtains Slater's split-band model of antiferromagnetism as described by DES CLOIZEAUX [4]. On the other hand, if  $\gamma_{\uparrow}=\gamma_{\downarrow}=\gamma$ , there is no magnetic order and the periodic charge distribution of the band electrons and ionic charge distribution will adjust selfconsistently to one another, leading to at least a partial compensation of the lattice and Coulomb contributions to the gap. For  $\gamma=\pi/2$ , there will be optimum overlap of the electronic and ionic charge densities. It is obvious that for intermediate values of  $\gamma_{\sigma}$  one can achieve states which correspond to mixtures of periodic electronic and spin densities.

In general one needs a gap at least comparable to the band width in order to ensure an insulating ground state. One can obtain large gaps by allowing relatively large crystallographic distortions accompanied by large or small Coulomb- and exchange contributions. However, in order to achieve selfconsistency, both the crystallographic distortion and the Coulomb- and exchange contributions are in general required to be large. This is the point we want to make: in treating crystallographic distortions of the type discussed above, one must not overlook the possible importance of electron-electron interactions. However, detailed numerical calculations on specific systems would be required, in order to decide whether the model has any practical applicability. Of course, ion-ion interactions, which we have neglected so far, would then also have to be taken into account.

Finally, we wish to remark that the model described above is a special case of the charge-density-wave model, recently described by OVERHAUSER [5].

### References

- [1] G. J. HYLAND, J. Phys. C (Proc. Phys. Soc.) 1, 189 (1968).

- [2] Solid State Physics, Eds. F. Seitz and D. Turnbull, Academic Press, to be published.

- [3] D. Adler, J. Feinleib, H. Brooks, W. Paul, Phys. Rev. 155, 851 (1967).

- [4] J. DES CLOIZEAUX, J. Phys. Radium 20, 606 (1959); 20, 751 (1959).

- [5] A. W. OVERHAUSER, Phys. Rev. 167, 691 (1968).

# Ein Analogverfahren zur Berechnung der Eigenschaften von Feldeffekttransistoren

von K. E. Drangeid und R. Sommerhalder

IBM Zürich Forschungslabor, 8803 Rüschlikon

(1. V. 68)

Shockley hat bereits 1952 eine Theorie des Feldeffekttransistors publiziert, welche die Berechnung der statischen Kennlinien gestattet. Der Gültigkeitsbereich dieser Theorie ist eingeschränkt durch die geometrische Auflage, dass die Länge der Gate-elektrode gross gegen die Dicke des Transistors sein muss, und durch die physikali-

sche Auflage, dass die Driftgeschwindigkeit der Ladungsträger im leitenden Kanal genügend klein im Vergleich zum Sättigungswert bleibt.

Die Shockleysche Theorie scheint lange nicht weiterentwickelt worden zu sein. In letzter Zeit hat sich allerdings wieder vermehrt technisches Interesse dem Feldeffekttransistor zugewendet, insbesondere miniaturisierten Ausführungsformen. Dabei werden beide Auflagen der Shockleyschen Theorie als störend empfunden; es drängt sich auf, eine Theorie zu entwickeln, die ohne diese auskommt. Nun erfordert leider eine allgemein gehaltene Diskussion der mit der Miniaturisierung sich stellenden Probleme die numerische Bearbeitung nichtlinearer partieller Differentialgleichungen, worauf hier nicht eingegangen werden kann. Wir möchten jedoch zeigen, dass wenigstens die geometrische Auflage der Shockleyschen Theorie mit einfachen Mitteln überwunden werden kann.

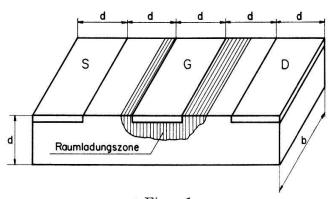

Gegeben sei eine Transistorgeometrie gemäss Figur 1. Das Halbleitermaterial sei ein n-leitendes Plättchen (Dicke d, Breite  $b \gg d$ ), seine Leitfähigkeit gegeben durch die Störstellenkonzentration N und die Elektronenbeweglichkeit  $\mu$ , seine Dielektrizitätskonstante  $\varepsilon$ . Source- und Drainelektroden seien Metallstreifen der Länge d, welche ohmischen Kontakt mit dem Halbleiter herstellen. Die Gateelektrode sei gleichfalls ein Metallstreifen der Länge d und besitze den Abstand d von den anderen Elektroden; der Gate-/Halbleiter-Kontakt wird als Schottky-Barrière angenommen, wobei die mobilen Ladungen aus der Raumladungszone quantitativ verdrängt sein sollen.

Figur 1

Transistorgeometrie.

S, G, D =Source-, Gate- und Drainelektrode, d =Transistordicke, b =Transistorbreite ( $b \ge d$ ). Länge und Abstand aller Elektroden gleich gross wie die Transistordicke.

Zwischen Source und Drain liegt die Spannung  $V_{SD}$  und fliesst der Drainstrom  $i_d$ , zwischen Source und Gate liegt die Spannung  $V_{SG}$  (die Diffusionsspannung am Metall-/Halbleiter-Kontakt sei in  $V_{SG}$  bereits mit eingeschlossen).

Unter den beschriebenen Bedingungen berechnet sich der Verlauf des elektrischen Potentials in der Gatezone als Lösung der Poissonschen Gleichung

$$\Delta V = -\frac{N e}{\varepsilon \, \varepsilon_0} \,, \tag{1}$$

im übrigen Halbleiter (Kanalzone) als Lösung der Laplaceschen Gleichung

$$\Delta V = 0 \tag{2}$$

mit den Randbedingungen

$$\frac{\partial V}{\partial n} = 0 \quad \text{auf dem Rand der Raumladungszone,} \\ \text{soweit dieser nicht Elektrode ist.}$$

(3b)

Lösungen der Gleichungen (1), (2) und (3) lassen sich mit einem Analogmodell wie folgt finden:

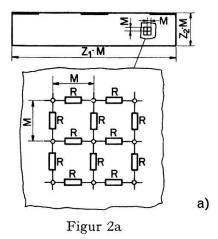

Wir simulieren das Halbleitermaterial in v-facher Vergrösserung durch ein diskretes zweidimensionales Netzwerk Ohmscher Widerstände R mit Maschenweite M, wie in Figur 2a gezeigt ( $Z_1 = \text{Zahl}$  Maschenpunkte in Längs-,  $Z_2 = \text{Zahl}$  Maschenpunkte in Querrichtung). Source-, Gate- und Drainelektrode werden als Kurzschlüsse am Netzwerk angebracht und auf die entsprechend Gleichung (3a) verlangten Potentiale gelegt (Figur 2b). Dann wird ein zunächst willkürlich berandetes Gebiet als Gatezone angenommen. Innerhalb dieser Zone werden die von Gleichung (1) geforderten Raumladungen dadurch simuliert, dass in jedem Maschenpunkt im Strom

$$I_{\varrho} = \frac{N e}{\varepsilon \, \varepsilon_0} \, \frac{M^2}{R \, v^2} \tag{4}$$

eingespiesen wird (Figur 2b). In unserem Widerstandsnetzwerk verzweigen sich nun die in der Raumladungszone eingespiesenen und die durch die Spannung  $V_{SD}$  erzeugten Ströme automatisch so, dass der Potentialverlauf im Netzwerk in der Gatezone eine Lösung von Gleichung (1), im übrigen Halbleiter eine Lösung von Gleichung (2) darstellt. Im allgemeinen wird aber die Randbedingung (3b) nicht erfüllt sein. Man muss deshalb die Form der Raumladungszone iterativ so variieren, bis Gleichung (3b) befriedigt ist. Offensichtlich wird durch die Erfüllung der Randbedingung (3b) auch

Analognetzwerk des Transistors. M= Maschenweite, R= Maschenwiderstand,  $Z_1=$  Zahl Maschen in Längsrichtung,  $Z_2=$  Zahl Maschen in Querrichtung.

Prinzip der Analogschaltung.  $V_{SG}=$  Gatespannung,  $V_{SD}=$  Drainspannung,  $I_D=$  Drainstrom (Analogwert),  $I_\varrho=$  Einspeisestrom zur Simulierung der Raumladung in der Gatezone.

verhindert, dass der durch die Drainspannung  $V_{SD}$  im Netzwerk erzeugte Strom  $I_D$ , der einem Drainstrom

$$i_D = N e \mu R b I_D \tag{5}$$

im Transistor entspricht, sich mit dem die Raumladungen simulierenden eingespiesenen Strom  $I_a$  vermengen kann.

Die erzielbare Genauigkeit nimmt mit sinkender Maschenweite M zu. In der Praxis ist der Anzahl der Maschenpunkte aber natürlich bald einmal eine Grenze gesetzt. Wir verwendeten  $Z_1 = 50$  Maschenpunkte in Längs- und  $Z_2 = 10$  Maschenpunkte in Querrichtung<sup>1</sup>).

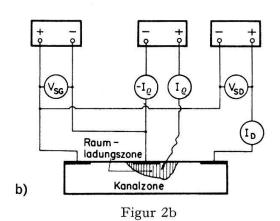

Nachfolgend werden einige Resultate dargestellt, die sich auf folgende Daten beziehen:  $N=5\cdot 10^{15}/\mathrm{cm^3}$ ,  $\mu=650~\mathrm{cm^2}/V$  sec,  $\varepsilon=12$ ,  $d=1\mu$ .

Beispiel eines Potentialbildes. Gatespannung  $V_{SG}=-2$  Volt, Drainspannung  $V_{SD}=+4,6$  Volt.

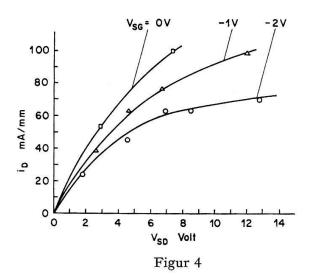

Figur 3 zeigt das Potentialbild für die Spannungen  $V_{SG} = -2$  Volt,  $V_{SD} = 4,6$  Volt. Figur 4 veranschaulicht das Kennlinienfeld des Transistors.

Transistorkennlinien: Drainstrom  $i_D$  als Funktion von Drainspannung  $V_{SD}$  bzw. Gatespannung  $V_{SG}$ .

<sup>1)</sup> Das Netzwerk enthielt ausser den in Figur 2a gezeichneten Widerständen R zusätzliche Diagonalwiderstände, die der Übersichtlichkeit halber hier ignoriert wurden.

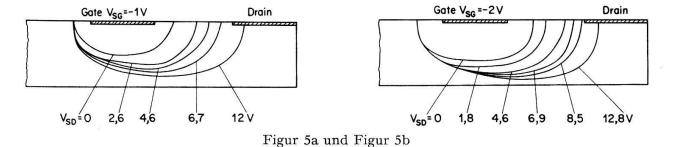

Figur 5a und 5b illustrieren Deformation und Expansion der Raumladungszone mit wachsender Drainspannung  $V_{SD}$  für zwei festgehaltene Gatespannungen  $V_{SG}=-1$  Volt bzw.  $V_{SG}=-2$  Volt. Es ist offensichtlich, dass ein Teil der Steuerwirkung des Gates dadurch verloren geht, dass die Raumladungszone in Richtung Drain auswächst statt quer zum Halbleiterplättchen, wie dies bei langer Gateelektrode nach der Shockleyschen Theorie der Fall wäre.

Form der Raumladungszone für verschiedene Drainspannungen  $V_{SD}$  bei festgehaltener Gatespannung  $V_{SG}$ .  $V_{SG}=-1$  Volt (Figur 5a),  $V_{SG}=-2$  Volt (Figur 5b).

Wenn mit  $I_{o \text{ tot}}$  der totale Einspeisestrom bezeichnet wird, ist

$$C_{GD} = \varepsilon \, \varepsilon_0 \left( \frac{\partial I_{\varrho \, \text{tot}}}{\partial V_{SD}} \right)_{V_{SG}} \tag{6}$$

die für Verstärkerschaltungen wichtige Millerkapazität (Gate-/Drain-Kapazität). Im vorliegenden Beispiel beträgt sie  $C_{GD} \approx 0.15 \text{ pF/mm}$ .

Würde man anstelle der Gatespannung die Drainspannung festhalten, dafür aber die erstere verändern, so liesse sich auf sonst gleiche Weise noch die Summe von Gate-/Source- und Gate-/Drain-Kapazität bestimmen, woraus dann mit Hilfe der Gleichung (6) die Eingangskapazität  $C_{SG}$  des Transistors gefunden werden könnte. In unserem Beispiel ist  $C_{SG} \approx 0.15 \text{ pF/mm}$ .

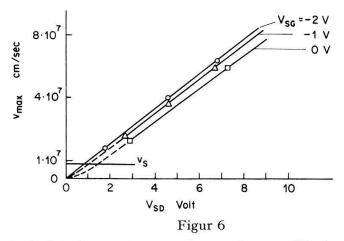

Trägt man (Figur 6) die maximale Driftgeschwindigkeit der Elektronen im Kanal unter dem Gate als Funktion der Gate- bzw. Drainspannung auf, so sieht man sofort,

Maximale Driftgeschwindigkeit  $v_{\text{max.}}$  für verschiedene Gate- und Drainspannungen  $V_{SG}$  bzw.  $V_{SD}$ .  $v_s = S$ ättigungswert der Driftgeschwindigkeit für Silicium.

dass für viele der gezeigten Analog-Bilder eine maximale Driftgeschwindigkeit  $v_{\rm max}$  herauskam, die grösser als die in gängigen Halbleitermaterialien mögliche, z.B.  $v_s \approx 10^7$  cm/sec in Si, ist.

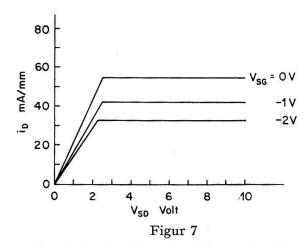

Verwirft man solche Lösungen als unrealistisch und nimmt statt dessen an, dass der Drainstrom seinen Sättigungswert erreicht, sobald  $v_{\rm max.}=v_s$  wird, so bekommt man anstelle des Kennlinienfeldes Figur 4 dasjenige der Figur 7. Letzteres hat sich bei verfeinerten Untersuchungen bis jetzt als recht brauchbare Näherung erwiesen. In unserem Beispiel beträgt die grösste Steilheit  $(V_{SG}=0)$   $g_m\approx 12$  mA/V·mm, die Drainspannung  $V_{SD}\approx 3$  Volt, die Gleichstromleistung  $P_{dc}\approx 150$  mW/mm.

Transistor-Kennlinien bei Berücksichtigung der Materialsättigung (Begrenzung der Driftgeschwindigkeit).

Würde man zwei Transistoren zu einem Verstärker hintereinander schalten, so könnte bis zu einer Grenzfrequenz

$$v_0 = \frac{1}{2\pi} \frac{g_m}{C_{SG} + C_{GD}} \tag{7}$$

Verstärkung erwartet werden.

In unserem Beispiel ist  $\nu_0 \approx 7.5$  Gigahertz. Allen hier angeführten Zahlwerten kommt nur die Bedeutung eines Beispiels zu. Sie sollen keinesfalls als typisch für Feldeffekttransistoren aufgefasst werden.