**Zeitschrift:** Comtec: Informations- und Telekommunikationstechnologie =

information and telecommunication technology

**Herausgeber:** Swisscom **Band:** 76 (1998)

Heft: 9

Artikel: System-on-Chip

Autor: Klipstein, Delano L.

**DOI:** https://doi.org/10.5169/seals-877322

# Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. Mehr erfahren

## **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. En savoir plus

#### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. Find out more

**Download PDF:** 26.11.2025

ETH-Bibliothek Zürich, E-Periodica, https://www.e-periodica.ch

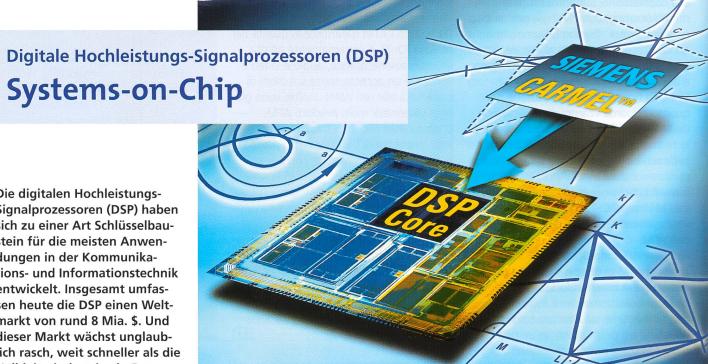

Die digitalen Hochleistungs-Signalprozessoren (DSP) haben sich zu einer Art Schlüsselbaustein für die meisten Anwendungen in der Kommunikations- und Informationstechnik entwickelt. Insgesamt umfassen heute die DSP einen Weltmarkt von rund 8 Mia. \$. Und dieser Markt wächst unglaublich rasch, weit schneller als die Halbleiterindustrie als Ganzes. In fünf Jahren wird ein DSP-Weltmarkt von rund 34 Mia. \$ erwartet. Mehr als 80% dieses Marktes liegen in der Kommunikationstechnik und in der Unterhaltungselektronik.

iemens steigt in das Geschäft mit «Cores» von programmierbaren Hochleistungs-DSP ein. Siemens will DSP-Kerne für die Integration ganzer Systeme auf einem Chip zur Verfügung

## DELANO L. KLIPSTEIN, MÜNCHEN

stellen, und das macht das Thema so interessant. Man spart nämlich Chips, denn DSP finden sich heute fast überall: in Modems (Weltmarkt: 1,37 Mia. \$), in Festplattenlaufwerken (1 Mia. \$ Weltmarkt), bei den «Cellular Phone» Handies (ebenfalls 1 Mia. \$ Weltmarkt), bei der Videokompression, in Sprachausgabechips usw.

## «Logikinitiative»

Siemens hat sich zu einem der technologisch führenden Halbleiterhersteller in den vergangenen vier Jahren hochgearbeitet, auch dank einer Spitzentechnik bei den DRAM, den Arbeitsspeichern der PCs. Doch diese Spitzenstellung wurde

hart erkauft: Mit DRAM kann man heute keine Gewinne mehr einfahren, nachdem die Preise durch weltweite Überkapazitäten abgestürzt sind. So müssen andere Massenprodukte her, die bessere Gewinne versprechen. Im Jahr 1997 hat der Siemens-Halbleiterbereich eine «Logikinitiative» gestartet, ein internes Programm, das das Produktions-Know-how der Speichertechnologie auf Logikschaltkreise umsetzen soll. Dabei setzt man eher auf neue Lösungen, als in bekannte Segmente eingeführten Unternehmen Konkurrenz zu machen. Kern der Bestrebungen ist es, mehr Leistung auf einen Chip zu bringen, also Mikrocontroller, Mikroprozessoren, Speicherblöcke, Signalprozessoren, A/D-Konverter und andere Bausteine in Form von «Cores» anzubieten und dann in kundenspezifische Lösungen zu integrieren.

Solche Lösungen können durchaus Massenprodukte sein. Und in diesen zählt jeder Chip: Die ersten Mobilfunkgeräte, die in den achtziger Jahren auf den Markt kamen, benötigten noch ein gutes Dutzend Chips und wogen ein paar Kilogramm. Heute wird um jedes einzelne Gramm gefeilscht: weniger Chips, geringerer Stromverbrauch, längere Betriebsdauer, niedrigerer Preis. Jeder gesparte Chip trägt dazu bei, dem Kunden solche Vorteile zu bieten.

#### Neuankündigung Carmel

Carmel heisst ein Berg in Israel (ebenso ein gleichnamiger Ort in Kalifornien, was vielleicht auf die Zielgruppe in den USA hindeutet). Entwickelt wurde die Architektur dieses DSP-Kerns bei Siemens und IC.COM, welche ihrerseits ein Joint-venture von Siemens/Nisko in Israel ist. Mit Israel gibt es auf dem Gebiet der DSP bei Siemens schon langjährige Verbindungen; es sei an die «Oak» und «Pine» DSP erinnert, die Siemens bereits seit Jahren einsetzt.

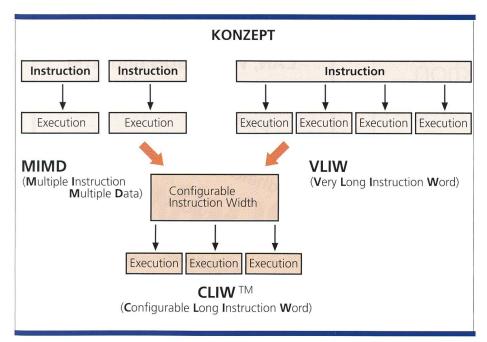

Als erster DSP-Core überhaupt setzt aber Carmel auf ein verbessertes Konzept bei der Nutzung der heute bekannten Verfahren und kombiniert diese in geschickter Weise. In Hochleistungsanwendungen bei DSP hatte man immer einen Kompromiss zu machen: Entweder musste man sich für eine superskalare Parallelverarbeitung entscheiden, das heisst den Befehlsablauf in mehrere einzelne Befehle auflösen, die dann parallel verarbeitet wurden, oder aber mit der Very-Long-Instruction-Word-(VLIW-)Architektur arbeiten – die einen Befehl mit langem Wort aufteilte und auf verschiedene Elemente zur Abarbeitung verteilte. Die Carmel-Architektur nutzt die Vorteile beider Verfahren: Sie macht den Befehl konfigurierbar (Configurable Instruction Width) und verteilt ihn dann zur Abar-

56 comtec 9-1998 beitung (Bild 1). So entstand die Architektur des «Configurable Long Instruction Word» (CLIW). Man muss sich fragen, warum noch niemand zuvor auf diese Idee gekommen ist.

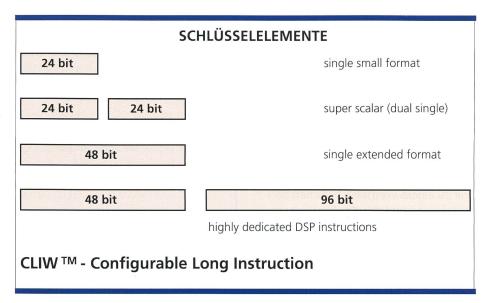

Daraus ergeben sich typische Befehlswortkonstruktionen, welche die jeweilige Anforderung durch eine dafür passende Wortlänge optimieren (Bild 2). Mit 24 bit wird ein kleinstes Datenwort angeboten, um relativ einfache Lösungen für einen DSP zu konfigurieren. Zweimal 24 bit führen zu einem superskalaren Wort, 48 bit Wortbreite zum «Single Extended Format», und als Hochleistungslösung stehen dann 48 bit (Standard-Befehlssatz) und 96 bit (programmierbarer, individueller Befehlssatz) in einer superskalaren Architektur zur Verfügung, mit der erstaunliche Leistungen erzielt werden können.

In einer achtstufigen Pipelinearchitektur lassen sich 120 M-MIPS (Multiple Million Instruction per Second) erzielen, bei 120 MHz Taktfrequenz und nur 2,5 V Betriebsspannung. Das Design des Carmel-Kerns ist so flexibel, dass es auch noch bei 1 V Betriebsspannung prinzipiell funktionsfähig ist. Unter dem neuen Begriff M-MIPS wird beschrieben, dass auf jede Instruktion bis zu 15 Elementaroperationen fallen können; in bestimmten Anwendungen kann dann eine Verarbei-

Bild 2. So ist das Befehlswort des CLIW-Codes zusammengesetzt: Ein 24-bit-Wort mit Standard-Befehlssatz und – bei maximaler Anforderung – ein 96-bit-Befehlswort mit einem programmierbaren, individuellen Befehlssatz werden einer Pipeline-Verarbeitung zugeführt. Für jede Anwendung kann man so die optimale Befehlslänge definieren und ist nicht gezwungen, zeit- und leistungsfressende Kompromisse einzugehen.

tungsleistung von 15x120 MIPS oder 1800 MOPS (Mega Operations per Second) erreicht werden. Einen derartig leistungsfähigen DSP-Kern zur Integration in «Systems on Silicon» gibt es bisher nicht in der Welt.

# **Anwendungsmöglichkeiten** Als erstes Anwendungsfeld wären zu-

nächst einmal die GSM- und CDMA-Mobilfunksysteme – erstere in Europa zu Hause (aber nicht nur), letztere in den USA und auch in Fernost favorisiert – zu nennen. Über kurz oder lang wird man wohl beide Systeme in einem Gerät integrieren müssen, um sich weltweit verschiedene und damit auch kostspielige Systemgeräte zu ersparen. Ein Mobilfunkhandy braucht etwa 500 KBytes Anwendersoftware – und die muss abgearbeitet werden. Dafür eignet sich das sehr lange, individuell gestaltbare 96-bit-Wort hervorragend in der superskalaren Architektur des Carmel-Core. In anderen Anwendungen kann die Anwendersoftware leicht auch mal 1 MByte überschreiten. Der schnelle Netzwerk-Datentransfer (xDSL) ist ein anderer Markt, der geradezu nach schnellen «Systems-on-Chip» schreit. Digital Audio ist ein weiterer, noch zu evaluierender Markt.

#### Auf der Suche nach Partnern

Dieser Weltankündigung von Siemens sollen nun schnell die ersten Chips folgen, Partnern werden grosszügig Lizenzen angeboten, um mit ihnen dann applikationsspezifische Lösungen zu entwickeln. Die ersten Chips werden wohl im 4. Quartal 1998 fertiggestellt sein. Dann wird man sehen, was am Markt

Bild 1. Das Beste aus zwei Konzepten: Die schon klassische MIMD-Architektur (Multiple Instruction Multiple Data) wird von Siemens mit dem Very-Long-Instruction-Word-Konzept zusammengefügt. Als Summe kommt der CLIW-Code heraus, der sich als besonders leistungsfähig erweisen wird.

comtec 9-1998

geschieht. Der von TI gerade angekündigte Gleitkomma-DSP 320C6x mit einer Leistung von 1 GFLOPS hat zwar für den Programmierer eben wegen der Gleitkommatechnik diverse Vorteile – erkauft wird dies aber mit einer grösseren Chipfläche. Und die kostet Geld. Da aber im Endverbrauchermarkt (und dazu gehören mittlerweile die Mobilfunkgeräte) nach Pfennigen und Rappen bei den Fertigungskosten gerechnet wird, wird es hier zu einem Wettstreit zwischen den Ingenieuren und den Kaufleuten kommen. Der Carmel-Kern dürfte billiger sein als eine separate Chiplösung, die auch noch mehr Leistung aus der Batterie ziehen dürfte. Der eine oder andere Mobilfunkgerätehersteller, der bereits diskrete DSP im Design seiner nächsten Gerätegeneration vorgesehen hat, könnte zum Nachdenken gezwungen werden – letztlich haben sich fast immer die Kaufleute durchgesetzt.

Wie hat es Gordon Moore, der legendäre Intel-Mitbegründer, doch so schön gesagt? «Nur der Verrückte überlebt in dieser Branche.» Dem kann man auch heute nichts hinzufügen.

# Zahlen und Fakten zu Carmel

Verarbeitungsgeschwindigkeit: 120 M-MIPS,

8stufige Pipeline,

Single-Cycle-Verarbeitung

16 bit Integer

bisher erreichte Verarbeitungsleistung: 1800 MOPS

Leistungsaufnahme: < 1 mW pro M-MIPS bei 2 V

Versorgungsspannung Power Management Kern und Speicher für 1,5 V

Low Power Process

Wirkungsgrad: für einen GSM-Sprach-Encoder:

7 M-MIPS bei 2 V und < 10 mW

Leistungsaufnahme

Benchmarks: Viterbi-Decoder: 22 Zyklen pro Stufe

Viterbi-Entzerrer: 28 Zyklen pro Stufe Assembler (in einer C-ähnlichen Syntax) Linker, Simulator, Emulator, C-Compiler

DSP-Core als Entwicklungschip im

**Emulations Board**

Prozesslithografie: 0,25 μm; später 0,18 μm und 0,13 μm

Erste Chips: Ende 1998

Entwicklungswerkzeuge:

Telefon + 41-33 228 20 20

Telefax + 41-33 228 36 59