**Zeitschrift:** Comtec: Informations- und Telekommunikationstechnologie =

information and telecommunication technology

**Herausgeber:** Swisscom **Band:** 75 (1997)

**Heft:** 12

Artikel: Der Sprung in den Gigabereich

Autor: Klipstein, Delano L.

**DOI:** https://doi.org/10.5169/seals-876984

#### Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. Mehr erfahren

#### **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. En savoir plus

#### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. Find out more

**Download PDF: 21.11.2025**

ETH-Bibliothek Zürich, E-Periodica, https://www.e-periodica.ch

### International Electron Devices Meeting (IEDM '97)

# Der Sprung in den Gigabereich

Die bedeutendste Elektronikkonferenz der Welt, die International Electron Devices Meeting (IEDM '97), die im Dezember 1997 in Washington D.C. zu Hause war, hat zum 43. Mal unter Beweis gestellt, dass hier die Elektronikzukunft gestaltet wird und nicht auf den von den Marketingfachleuten geschätzten berühmteren Halbleiterkonferenzen.

n der Beteiligung der Unternehmen und Staaten widerspiegeln sich fast die Marktverhältnisse in der Halbleitertriade USA/Fernost/Europa: 46 % der über 200 Referate wurden von Amerika-

#### DELANO L. KLIPSTEIN, MÜNCHEN

nern vorgetragen, 39 % von Asiaten. Die restlichen 15 % kamen aus Europa. Gegenüber dem Vorjahr wuchs die US-Beteiligung spürbar: Selbst wenn man den «Heimvorteil» der Amerikaner berücksichtigt, bleibt doch das wiedererstarkte Selbstbewusstsein von «Uncle Sam» auf diesem Gebiet sichtbar.

## Chipkarten, Lithografie und Multimedia

Siemens hatte sich in diesem Jahr eine der drei prestigebehafteten Plenarsitzungen gesichert. Ulrich Hamann, Chef der Chipkartenhalbleiter, erläuterte den staunenden Amerikanern die Tücken des SmartCard-Geschäfts: Hohe Innovationsgeschwindigkeit, Massenmärkte, riesige Wachstumspotentiale mit all ihren Risiken wie drastischer Preisverfall prägen das Geschäft. Doch der Chip ist nichts, wenn nicht leistungsfähige Systemanbieter dahinterstehen, die dem «Rechner in der Geldbörse» das Einsatzgebiet aufbereiten. So war es ein Lehrstück für Amerika: Die Europäer sind auf diesem Gebiet immer noch unangefochten Weltmarktführer in den Anwendungen. Die Grenzen der heutigen Lithografieverfahren für die Belichtung von Halbleiterchips diskutierte T. Brunner von IBM in Hopewell Junction, einem der am besten ausgerüsteten Forschungsstandorte für die Halbleitertechnik in der Welt. Er kam zu dem Schluss, dass keine der derzeit diskutierten Alternativen zur quasioptischen Lithografie ernsthaft konkurrieren kann. Durch immer neue Tricks lassen sich die Anwendungsgrenzen zu immer feineren Strukturen hinausschieben. Für die Zeit nach der optischen Lithografie, die noch nicht in Sichtweite zu sein scheint, biete sich wohl nur noch die 1:1-Röntgenlithografie an. Über den Finfluss von Multimedia auf die

Über den Einfluss von Multimedia auf die Halbleitertechnik sprach J. Sasaki von NEC aus Tokyo. Drei Schlüsselthemen stellte er dabei heraus: die Frage, wie sich sehr unterschiedliche Einzelfunktionen mit differenzierter Technologieanforderung weiter integrieren lassen, wie man höhere Leistungsfähigkeit mit der Forderung nach geringerem Stromverbrauch verbinden kann und wie man die «Time-to-market» weiter verkürzt, um mit der raschen Entwicklung auf dem Multimediagebiet Schritt zu halten. Lösungen sieht Sasaki in einer drastischen Verringerung der durch lange Verbindungswege erzwungenen Laufzeiten auf den Schaltkreisen und Baugruppen durch «Systems on Chip» sowie in neuen energiesparenden Schaltungen. Ein wesentlicher Punkt ist die rechtzeitige Bereitstellung verbesserter Lithografieverfahren, womit er die Überlegungen seines Kollegen Brunner von IBM stützte. Auf der strategischen Seite sieht Sasaki engere Zusammenarbeit zwischen den Halbleitertechnologen einerseits und den Schaltungsspezialisten in den Designhäusern anderseits, um die jeweils optimale Systemlösung zu finden.

Während die Plenarsitzungen Trends aufzeigen, werden in den Fachgruppen die technologischen Einzelschritte diskutiert. Wegen der Vielzahl dieser Gruppen – auf der IEDM '97 gab es immerhin 36 Arbeitsgruppen mit jeweils einem halben Dutzend Vorträge – haben wir hier eine strenge Auswahl getroffen. Sie orientiert sich eher an Hardwareergebnissen denn an Spezialthemen: Viele der Fachgruppen behandeln Themen, die für die Produktionstechnik oder Simulation am Bildschirm von Wichtigkeit sind, aber den «normalen» Elektronikingenieur weniger betreffen.

## Speichertechnologien schreiten schnell voran

Wie nicht anders zu erwarten, berichteten diesmal gleich zwei japanische Unternehmen über Technologiefragen bei 4-Mbit-Speichern. Da die feinsten Strukturen dieser künftigen Chips rund 0,12 µm betragen, wird ein mechanisches Problem riesengross: Die Anschlusskontakte auf dem Chip müssen in irgendeiner Form nach aussen in ein Gehäuse geführt werden. Hier werden mechanische Toleranzen für die Kontaktierung auf dem Chip gefordert, die weit unter 100 nm – der zehntausendste Teil eines Millimeters – liegen. Was im Labor lösbar ist, stellt in der Massenproduktion bereits ein erhebliches Problem dar, weil die Kontaktierung der Chips in Sekundenschnelle erfolgt. NEC stellte eine mögliche Kontaktierungstechnik für seine 0,13-µm<sup>2</sup>-DRAM-Zelle vor. Durch spezielle Massnahmen konnte man die Toleranz für die Verdrahtung auf 70 nm bringen, was etwa der halben minimalen Strukturabmessung entspricht. Zum Vergleich: 70 nm sind ein Sechstel der kürzesten für das Auge wahrnehmbaren Lichtwellenlänge.

Auch Fujitsu berichtete über eine 4-Gbit-Speicherzelle mit einer Fläche von 0,21 µm² – deutlich grösser als die des Konkurrenten. Fujitsu ging nicht ganz so weit mit den Strukturen herunter und nutzte eine 0,15-µm-Technologie. Bemerkenswert an der Technik ist der Kondensator, den Fujitsu für die Speicherzelle benutzt: Er besteht aus einem 1,2 µm hohen winzigen Pfeiler auf dem Chip – und davon 4 Mia Stück pro Chip. Als Dielektrikum wird das altbekannte, sehr stabile Tantalpentoxid benutzt – an

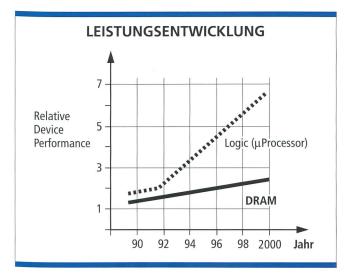

Bild 1. Relative Leistungsentwicklung von Speichern (ausgezogene Linie) und Logikbausteinen (gestrichelte Linie) bis zum Jahr 2000. Die sich öffnende Lücke seit Beginn der neun-Systementwicklern schon heute sehr zu schaffen (Bild: IBM/IEDM '97).

ziger Jahre macht den

### Die **Technologievorreiter**

Die höchste Beteiligung stellte Texas Instruments mit 17 Referaten, gefolgt von NEC mit 14 und den beiden Amerikanern IBM und Bell Labs/Lucent Technologies mit je 13. Mit über zehn Referaten meldeten sich noch Hitachi und Toshiba zu Wort, dann gab es ein grosses Loch. Die nächsten Unternehmen rangierten im Ranking bei sieben Referaten oder weniger.

Und die Europäer? Philips führte die Liste an mit sieben Vorträgen. An zweiter Stelle lag nicht SGS-Thomson Microelectronics oder Siemens, sondern die ETH in Zürich mit fünf Referaten. Von den insgesamt 29 europäischen Vortragenden bestritten Philips und die ETH fast die Hälfte. Hat Europa auf diesem Gebiet so wenig zu sagen? Das wäre voreilig geschlossen. Die Europäer haben sich auf Themen fokussiert, wo sie ihre Stärken ausspielen konnten. Und das ist nicht die ganze Breite des Elektronikspektrums. Schliesslich stellte auch der Weltmarktführer Intel «nur» drei Referenten, und man kann wirklich nicht sagen, dass diese Zurückhaltung sich im Markterfolg spiegelt.

das neuere, noch wenig erprobte BST-Material wagte man sich offensichtlich noch nicht heran. Dafür hat die vorgestellte Technologie einen besonderen Vorteil: Man kann in ihr relativ leicht Logikzellen realisieren und so zu «Embedded Logic in DRAM» kommen. IBM-Wissenschaftler wiesen erneut darauf hin, dass die Leistungsfähigkeit der Logikchips sehr viel schneller wächst als die der Halbleiterspeicher (Bild 1). Dies liegt nicht so sehr in der Speicherkapazität als solcher, sondern im mangelnden Datendurchsatz bei der Kommunikation zwischen Prozessorlogik und Arbeitsspeicher. Diese wachsende Lücke zwischen den beiden Hauptträgern aller Elektroniksysteme erzwingt geradezu neue Überlegungen. Leistungsfähigere Hardwarearchitekturen (SyncLink, RAMBUS) für die Speicher sind ein Lösungsweg, die Integration von Speichern und Logik auf einem Chip ein anderer. Hierfür aber müssen die bestehenden Produktionsprozesse für eine Massenfertigung modifiziert werden.

Nachdem Intel im Sommer 1997 mit einem 64-Mbit-Flash-Speicher die Diskussion um eine Ablösung der mechanischen Festplatte in Laptop-PCs wieder angeheizt hat, war auf dem Gebiet der Flash-Speicher auch mit neuen Informationen auf der IEDM '97 zu rechnen. Und richtig: Toshiba stellte eine Zelltechnologie vor, die es möglich macht, 256-Mbitoder gar 1-Gbit-Flash-Speicher aufzubauen. Die Zelle selbst ist mit 0.31 um<sup>2</sup> Fläche eine der bisher kleinsten NAND-Zellen; sie ist in 0,25/0,15-µm-Technologie gefertigt. Das Einschreiben in die Zelle geht in etwa 40 µs vor sich, das Löschen braucht rund 1 ms. Die Konkurrenz bei Hitachi sprach über eine 0,24-µm<sup>2</sup>-Zelle, welche in 0,2/0,18-µm-Technologie produziert wurde. Auch diese Speicherzelle zielt auf einen 1-Gbit-Flash-speicher. Eine echte Ablösung der Festplatten in PCs durch Flash-Speicher ist gegenwärtig nicht zu erwarten. Zum einen sprechen die höheren Kosten dagegen (eine durch Flash-Speicher ersetzte Festplatte wäre rund 20mal teurer), zum anderen ist die Zahl der Schreibzyklen begrenzt: Kaum ein Hersteller von Flash-Speichern garantiert nämlich mehr als 10 000 Schreibzyklen. Etwas exotisch mutete ein 1-Gbit-SOI-DRAM an, das von Hyundai Electronics

realisiert wurde. Nicht nur die grosse Zahl der an dem Vortrag selbst namentlich Beteiligten (20) fiel auf, sondern für einen Europäer überraschend – dass von diesen 20 fast die Hälfte auf die Familiennamen «Lee» oder «Park» hören (was wohl den «Millers» in den USA und den «Meiers» in Deutschland entspricht). Der Chip hat eine Fläche von 691 mm<sup>2</sup>, die eigentliche Speicherzelle – sie wurde in 0,17-µm-Technologie gefertigt – belegt 0,33 μm<sup>2</sup>. Die erreichte Zellkapazität wurde mit 15 Femtofarad (fF) angegeben. Der Chip wird mit 2,2 V betrieben. Leider ist SOI (Silicon on Insulator) noch sehr teuer.

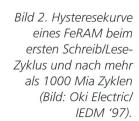

Ferroelektrische Speicherchips (FeRAM, auch FRAM) ziehen seit kurzem das Interesse der Anwender auf sich. Solche Speicher sind nichtflüchtig, das heisst, sie brauchen keinen Auffrischzyklus wie das DRAM, um die abgespeicherte Information zu halten. Als Folge kommt man zu sehr niedrigem Energieverbrauch. Gegenüber den bisher bekannten nicht-

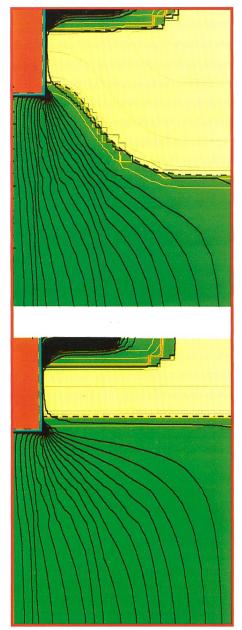

Bild 3. Die FeRAM-Speicherzelle von NEC unter dem Rasterelektronenmikroskop: Im oberen Bild kann man sehr gut die «vergrabenen» PZT-Kondensatoren als helle Schicht erkennen. Das untere Bild ist eine Draufsicht auf die Zellstruktur (Bild: NEC/IEDM '97).

#### Wer mehr wissen will . . .

Bei weit mehr als 200 Referaten ist es für den Konferenzteilnehmer unmöglich, alle wichtigen Themen selbst wahrzunehmen. Da bleibt dann nur der Konferenzband, der mit rund 1000 Seiten ein ausgesprochenes «Schwergewicht» ist. Als Nachschlagewerk bleibt er aber auch über die Konferenz hinaus unentbehrlich, weil er über die Jahre eine wichtige Referenzquelle für Grundlagenarbeiten darstellt. Aus Anlass ihres 40jährigen Bestehens wurde ein Kompendium herausgegeben, welches für jedes Jahr die wichtigsten Themen aufsummierte und in das gesamte politische und wirtschaftliche Umfeld stellte. Der Autor bekennt, dass diese Zusammenstellung bis heute für ihn eine Fundgrube besonderer Art ist. Der Tagungsband der IEDM '97 ist auch für Nichtteilnehmer zugänglich. Man bekommt ihn beim IEEE Service Center, 445 Hoes Lane, Piscataway, NJ 08855-133, USA. Wer es ganz eilig hat, kann sein Exemplar per Fax bestellen: +1-908-463 1571. Auch eine CD-ROM-Version ist erhältlich: Die für das Lesen erforderliche Software (Adobe 2.1 Reader) wird auf der CD-ROM mitgeliefert (sofern man sie nicht ohnehin schon auf seinem PC hat). Die CD-ROM läuft auch mit einem 386er-PC, wir würden dies aber nicht empfehlen. Ein 486er sollte es schon sein, noch besser aber eine Pentium-Maschine, weil es sonst mit den Grafiken eher mühsam läuft. Ein Arbeitsspeicher von 8 MByte ist wünschenswert (minimal sind 4 MByte erforderlich).

flüchtigen Speichern (wie z. B. Flash-Speichern) gewinnt man auch noch erheblich an Arbeitsgeschwindigkeit beim Einschreiben und Auslesen. Eines der Probleme mit diesen Speichern liegt noch in der Zuverlässigkeit und Ermüdungsfreiheit der ferroelektrischen dünnen Filme. Als Basismaterial hat sich für die Zukunft SBT empfohlen, ein Oxid-Compound aus Strontium (Sr), Wismut

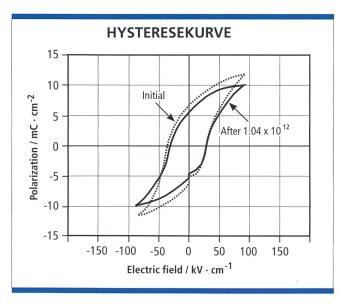

Bild 4. Erster vollintegrierter Windsensor, der von der ETH in Zürich kommt. Der zu messende Luftstrom verändert das Temperaturdifferential auf einer mikromechanisch geätzten Membran des Sensors. Diese Änderung wird elektronisch ausgewertet. Im oberen Teil des Bildes sieht man den Chip, aufgebaut auf einem flexiblen Substrat; im unteren Teil das ganze System. (Bild: ETH Zürich/ IEDM '97).

(Bi) und Tantal (T). Der Speichereffekt bzw. das Löschen wird durch Polarisationsänderungen im Material entlang einer Hysteresekurve realisiert, die beim Schreib/Lösch-Vorgang durchlaufen wird. Für den Einsatz dieser Technik ist es natürlich wichtig, dass sich die Hysteresekurve auch nach vielen Millionen Schreib/Lösch-Zyklen nicht grundsätzlich verändert (Bild 2).

Mehrere Firmen (Matsushita/Symetrix, NEC, Oki Electric, Sharp) berichteten über technologische Fortschritte bei den FeRAM. Fujitsu (Kawasaki, Japan) stellte eine 0,5-µm-FeRAM-Technologie vor, die voll kompatibel mit einem 0,5-µm-Logik-prozess in CMOS-Technik ist: eine hochinteressante Entwicklung, weil sie Fortschritte bei der Integration ganzer Systeme auf einem Chip verspricht. Das Unternehmen arbeitet eng mit Ramtron (USA) zusammen, die auf diesem Gebiet Pionierarbeit geleistet haben. Bisher wird

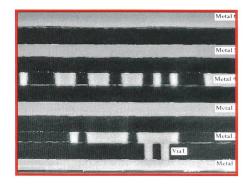

Bild 5. Querschnitt durch einen Chip mit sechs Metallisierungslagen aus Kupfer. Diese Technik wird sowohl von IBM als auch von Motorola als Sprung in eine neue Dimension für Systems on Silicon gesehen. Beide Firmen stellten erste Chips in dieser Technik vor (Bild: IBM/IEDM '97).

ein Standard-FeRAM mit 1 Mbit gefertigt. Im Labor hat man jetzt zu Demonstrationszwecken einen 8-bit-Prozessor in CMOS-Logik mit einem 68-kbit-FRAM auf einem Chip erfolgreich hergestellt. Die Stossrichtung einer solchen Entwicklung scheint klar: Sie zielt auf Hochleistungschipkarten ab.

NEC stellte eine vergleichsweise sehr kompakte FeRAM-Zelle vor, die mit einem Transistor und zwei Kondensatoren aufgebaut ist. Die Zelle ist zwangsläufig erheblich grösser als die Speicherzelle eines modernen DRAM, für ein FeRAM aber doch sehr kompakt. Die ferroelektrischen Kondensatoren werden aus PZT gebildet (Blei-Zirkonium-Titanat) und haben eine Basisfläche von 3×3 µm. Das Rasterelektronenmikroskop lässt gut den Aufbau erkennen (Bild 3). NEC plant, damit später ein 256-Mb-FeRAM aufzubauen.

#### Mikroelektromechanische Systeme (MEMS) in praktischen Anwendungen

Im vergangenen Jahr waren auf der IEDM einige interessante Entwicklungen bei den MEMS zu sehen; in diesem Jahr standen sie nicht ganz so im Rampenlicht. Vielleicht wurde einiges 1997 schon vorweggenommen. Die ETH Zürich war diesmal mit zwei Anwendungen dieser Technologie vertreten: einem Doppelhallsensor mit selbstkompensiertem Offset und einem Einchipanemometer, beide in CMOS-Technologie. Der Signaloffset des Doppel-Hallsensors liegt

mit 2 mT fast 500mal niedriger als der eines Einzelhallsensors, gemessen bei Raumtemperatur. Der vorgestellte mikromechanische Windmesser misst Windgeschwindigkeiten zwischen 0 und 12 Beaufort (0 bis 38 m/s), was einem Dynamikbereich von 65 dB entspricht. Das System, einschliesslich des nachgeschalteten A/D-Wandlers, ist in einem Plastikgehäuse von 1 cm Durchmesser untergebracht. Das ganze Volumen beträgt weniger als 3 cm³ (Bild 4).

#### Neue Technologien am Horizont

In das Gebiet der «Systems on Chip» gehören die von Intel und Motorola unabhängig voneinander – vorgetragenen Arbeiten über eine Chiptechnologie für Logikschaltkreise, die sechs metallische Lagen auf dem Chip für die Verdrahtung anbietet. Das grundsätzlich Neue daran ist, dass anstelle von Aluminiumleitungen auf dem Chip nun Kupfer verwendet wird. Aluminium hat den grossen Vorteil, dass es sich gut mit dem Silizium verträgt, welches das Basismaterial für die Chips ist. Es hatte aber auch zwei Nachteile: Sein Flächenwiderstand ist vergleichsweise hoch, und es neigt zu sogenannter «Elektromigration», das heisst, Aluminiumteilchen werden mit dem elektrischen Strom «mitgerissen» und wandern damit über den Chip. Kupfer hingegen ist zwar wenig siliziumfreundlich, kontaminiert sogar den Chipgrundstoff, hat aber einen viel geringeren Widerstand und vor allem keine Elektromigration. Die beiden Unternehmen trugen ihre ersten Erfahrungen über Chips mit Kupferleiterbahnen vor, die bis zu sechs metallische Lagen aufweisen (Bild 5). Das neue Verfahren ist vollintegrierbar in die gängigen 0,25-µm-CMOS-Prozesse.

Die Philips Forschungslaboratorien in Eindhoven legten ihre Arbeiten an mikroelektronischen Bausteinen und Displays offen, die mit organischen Polymeren arbeiten. Einiges davon haben wir schon an anderer Stelle gefunden (Universitäten Princeton und Minnesota). Die Philips-Forscher berichteten über eine orangefarbene Kunststoff-LED, die bei 4 V arbeitet und eine Leuchtdichte von maximal 100 cd/m<sup>2</sup> realisiert. Noch liegt die Lebensdauer bei einigen tausend Stunden, aber man untersucht schon den Einsatz in möglichen Displays. Auch auf dem Weg zu Kunststoffchips gibt es Fortschritte: In Eindhoven wurden bereits 45 Polymertransistoren auf einem Chip integriert. Was die Technologie so interessant macht: Die Herstellkosten sind sehr viel niedriger, und als Substrat kann man sogar Papier benutzen. Darüber hinaus lässt sich ein «Wafer» in wenig mehr als einer Stunde fertigstellen. Erste Einsätze könnten sich für wirklich billige

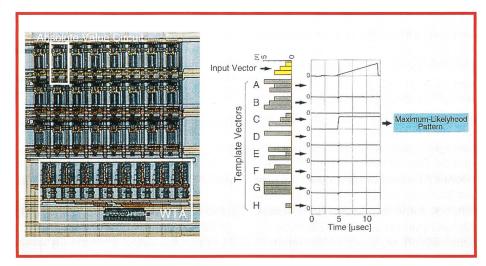

Bild 6. Ein elektronisches Neuron wurde von der Universität Tokio entwickelt und damit ein Testschaltkreis aufgebaut (im Bild links). Rechts im Bild ist zu sehen, wie der Chip aus einer Auswahl von Buchstaben den mit der höchsten Wahrscheinlichkeit – hier also das «C» – erkennt. Der Schaltkreis ist voll kompatibel mit herkömmlicher 0,25-µm-CMOS-Technik. Für den 1 cm² grossen Chip, der aus diesen elektronischen Neuronen aufgebaut wurde, ergibt sich die fast unglaubliche Rechenleistung von 20 Teraoperationen pro Sekunde (Bild: Universität von Tokio/IEDM '97).

COMTEC 12/1997 23

Bild 7. Das Bild zeigt ein Array von optischen Modulator- und Detektordioden (grosse Rechtecke im Bild), die auf einem aktiven Siliziumschaltkreis aufgebondet wurden. Damit lassen sich hohe Übertragungsgeschwindigkeiten auf Standardsiliziumchips realisieren (Bild: Bell Labs, Lucent Technologies/IEDM '97).

«Warenanhänger» ergeben, mit denen man im Laden die Ware gegen Diebstahl schützt.

Die Universität Tokyo beschrieb Überlegungen für ein intelligentes System in Large Scale Integration, das sich am Modell des menschlichen Gehirns orientiert. Das als «neurale Mikroelektronik» beschriebene System speichert Erfahrungen und Erkenntnisse, die es einmal gewonnen hat, in einem nichtflüchtigen Speicher. Die abgelegten Informationen werden bei einer anstehenden Entscheidung darauf hin überprüft, ob es einen ähnlichen Fall schon einmal gegeben hat, und das System legt diese frühere Entscheidung dann dem aktuellen Prozess zugrunde. Das Basiselement, auf dem die neurale Mikroelektronik aufbaut, ist eine Art Transistor. In ihm hat man eine Kombination aus verkoppelten Vielfachkapazitäten einerseits und MOSFETs anderseits realisiert, die durch Änderung der Vorspannung angesteuert werden. In den vergangenen Jahren wurden erste Echtzeitlogikgatter gebaut, die beispielsweise in der Mustererkennung eingesetzt wurden (Bild 6). Um die Leistungsfähigkeit eines solchen neuralen Systems zu zeigen, haben die Japaner einen Echtzeitchip für die Bildkompression entwickelt: Er liess hinsichtlich der Leistungsfähigkeit übliche CISC-Prozessoren um den Faktor 100 bis 1000 hinter sich. Ein weiteres Zukunftsthema ist die optische Verbindungstechnik für Siliziumschaltkreise in Ultra Large Scale Integration (ULSI). Jüngste Entwicklungen von

15

10

5

0.0

0.5

1.0

Pout [W]

Gp [dB]

Neue Ideen für die Hochfrequenztechnik Von Hitachi wurde ein Leistungs-MOSFET aus Silizium für 2 GHz vorgestellt, der bei 3,6 V Versorgungsspannung auf eine maximale Ausgangsleistung von 1 W kommt. Wird er mit 0,8 W Ausgangsleistung betrieben, liegt der Wirkungsgrad (Overall efficiency) bei 34 %. Die erzielbare Verstärkung wird mit 6,5 dB angegeben. Nach Auskunft des Unternehmens soll der MOSFET in künftigen Han-**VERSTÄRKUNG** f = 2 GHzVq = 0.75 VTuning for CDMA Vdd = 4.8 V-Vdd = 3.6 V -2.4 V

Bild 8. Verstärkung (in dB) in Abhängigkeit von Ausgangsleistung (in W) mit der Drainspannung als Parameter: Mit drei Standardbatterien kommt Hitachi auf 1,2 W bei 2 GHz Sendefrequenz (Bild: Hitachi/IEDM '97).

den Bell Laboratories bei der Integration von Optoelektronik auf Silizium könnten zu einer erfolgreichen Ehe führen, die sich auch bei den sehr hohen Taktraten künftiger Chips bewährt (Bild 7). Optische Verbindungen haben keinen der Nachteile, die man metallischen Verbindungen nachsagt: Es gibt weder Leitungswiderstände noch parasitäre Kapazitäten, keine zusätzliche Dämpfung bei Hochfrequenz, kein Nebensprechen, und auch die Elektromigration gibt es nicht, die auf Chips wegen der zunehmenden Leistungslängen Ärger macht. Mehr als 4000 solcher Hochgeschwindigkeitschips, die intern mit optischer Übertragung arbeiten, wurden schon gebaut. Neben IBM zeigte die hochangesehene Stanford-Universität die Möglichkeiten für die Zukunft auf und liess keinen Zweifel offen, dass die optische Verbindungstechnik für Hochleistungsschaltkreise die bevorzugte Verbindungstechnik im nächsten Jahrhundert sein wird.

2.0

1.5

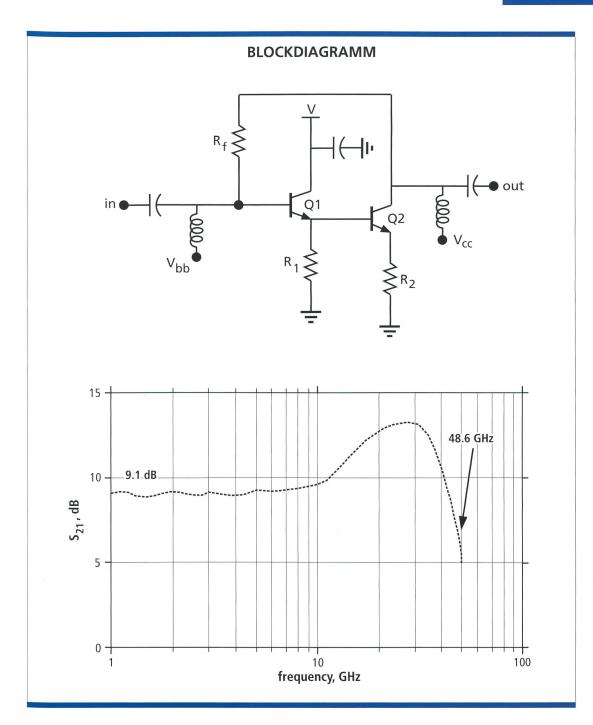

Bild 9. Blockdiagramm eines rückgekoppelten Darlington-Verstärkers mit HBTs (oben) sowie die an ihm gemessene Verstärkung über der Frequenz (unten) (Bild: Universität von Kalifornien/IEDM '97).

dies für CDMA und GSM als Leistungsverstärker eingesetzt werden. Während bisherige Bausteine meist in 0,8-µm-Technologie hergestellt werden, ging Hitachi auf 0,4-µm-Strukturen zurück: Hiermit werden unter anderem die guten HF-Werte begründet (Bild 8). Gleich mehrere Vortragende beschäftigten sich mit der Frage, wie man bei 2 GHz Arbeitsfrequenz vernünftige Induktivitäten mit ausreichend hohen Gütewerten (Q) integrieren kann, die man für die Frequenzabstimmung bei Mobilfunkgeräten braucht. Das koreani-

sche Forschungsinstitut für Elektronik und Telekommunikation zeigte mehrere passive integrierte HF-Spulen, alle im Bereich zwischen 2 und 13 nH, die bei 2 GHz Betriebsfrequenz ein Q zwischen 4 und 14 erzielten. Den Vogel schoss aber das Forschungszentrum von Rockwell ab: Die Wissenschaftler demonstrierten eine integrierbare, abstimmbare Induktivität, die als aktiver Schaltkreis mit Phasenschiebung ausgebildet ist. Die Werte sind denn auch bestechend: Bei 1,5 nH Induktivität und 2 GHz Messfrequenz wurde nach sorgfältiger Abstim-

mung des nachgeschalteten elektronischen Phasenschiebers eine Güte Q von mehr als 1000 erreicht. Die eigentliche Spule hat fünf Windungen und ist nur 10 µm breit. Kaufen kann man das Wunderding nicht: Rockwell wollte mit diesem Vorschlag zeigen, in welche Richtung sich möglicherweise künftige Entwicklungen bewegen.

9 dB Verstärkung bei 48 GHz Bandbreite, das bietet ein rückgekoppelter Verstärker, der einen Heterojunction Bipolar Transistor (HBT) aus AllnAs/GalnAs verwendet. Die Universität von Kalifornien

Bild 10. Das obere Bild zeigt den Stromfluss in einer gängigen spannungsbegrenzten MOSFET-Zelle; die «geklemmte» Spannung begrenzt den Stromfluss und führt zu höherem Flächenwiderstand. In der TrenchFet-Zelle von Siliconix-Temic fällt hingegen der gleichmässige Stromfluss ins Auge und damit der niedrige Flächenwiderstand (Bild: Siliconix-Temic/IEDM '97).

in Santa Barbara stellte das Element vor und erhebt damit den Anspruch, einen Weltrekord für einen solchen Darlington-Verstärker aufgestellt zu haben. Der Chip hat die Abmessungen 0,4×0,37 mm; seine Verstärkung über der Frequenz zeigt das Bild 9. Nach einem Redesign erwartet man eine Bandbreite von mehr

als 60 GHz. Solche Breitbandverstärker werden für die optische Übertragungstechnik benötigt, wenn man wirklich zu hohen Datenübertragungsraten kommen will. Ein kleineres Problem liegt darin, dass man den Eingangs- und Ausgangsscheinwiderstand von 50 noch nicht über den ganzen Frequenzbereich realisieren konnte. Die Entwickler schieben dies Manko aber auf das relativ einfache Design des Verstärkers und sind sich sicher, bei einem Redesign auch dies Problem in den Griff zu bekommen. Von Hitachi in Tokyo wurde eine HBT-Technologie vorgestellt, mit der man eine Transitfrequenz von 130 GHz erzielt hat. Der SiGe-HBT erreicht diese bei einem Kollektorstrom von 6 mA. Bei 1 mA Kollektorstrom wurde noch eine f<sub>T</sub> von >100 GHz gemessen.

## Der Einelektronentransistor – auch in diesem Jahr wieder attraktiv

Viel ist schon über ihn geschrieben worden: den Einelektronentransistor (SET, Single Electron Transistor), der statt einer Viertelmillion Elektronen wie heute nur noch ein oder wenige Elektronen zum Durchschalten benötigt. Fast alle einschlägigen Referate auf der IEDM '97 setzten sich mit Technologiefragen bei der Herstellung dieser Einelektronenbausteine auseinander. Technologisch bedingt sind die Arbeitstemperaturen sehr niedrig (oft nur wenige Kelvin). Interessant daher diejenigen Referate, welche die Arbeit der Bausteine bei Raumtemperatur zum Inhalt hatten, zum Preis, dass man fast unvorstellbar kleine Abmessungen realisieren muss, da hier nur noch mit sogenannten Quantenpunkten (Quantum Dots) gearbeitet wird. Ein Team der Universitäten Princeton und Minnesota hat einen solchen MOSFET in SOI-Technik aufgebaut. Da die Funktion eines SET auf Quanteneffekten beruht, zeigt der Drainstrom einen durch leichte Treppenstufen abgeflachten Anstieg über der Gate-Spannung. Typisch für dieses neue Bauelement sind die winzigen Abmessungen: Die Quantenpunkte haben Durchmesser von einigen Nanometern, ihre Kapazität liegt etwa bei 1 Attofarad. Ein Attofarad ist der millionste Teil eines Picofarad. Die am Ausgang des SET gemessenen Ströme liegen im einstelligen nA-Bereich.

Man kann solche Bausteine auch in anderen Materialien als Silizium realisieren. Dies zeigte das Electrotechnical Laboratory in Tsukuba (Japan), das sich mit Spitzenforschung einen Weltnamen gemacht hat. Gemeinsam mit dem Tokyo Institute of Technology hat man einen SET ebenfalls bei Raumtemperatur in Niob/Nioboxid realisiert, welches auf Siliziumsubstrat aufgebracht wurde. Die ultradünnen Niobfilme weisen nur eine Dicke von 2 bis 3 nm auf.

Eine praktische Anwendung für solche Entwicklungen gibt es bisher allenfalls in der Messtechnik, wenn man sehr geringe Ladungen erfassen will. Für Massenprodukte wie zum Beispiel Speicherchips wird es noch eine Ingenieurgeneration brauchen, bevor man darauf zurückgreifen kann. Doch die Chancen sind viel zu gross, als dass man es vernachlässigen wird. Für tragbare, batteriebetriebene Hochleistungsgeräte (z. B. Multimedia-PCs im Taschenformat) wäre mit einem Schlag das Batterieproblem gelöst: Was praktisch um den Faktor 1000 weniger Strom braucht, kann mit einem Batteriesatz auch 1000mal länger arbeiten . . .

#### Interessante Einzelergebnisse mit herausragenden Daten

Silicon-on-Insulator (SOI) ist zwar noch eine teure Technologie, aber die unbestreitbaren Vorzüge hinsichtlich sehr guten Hochfrequenzverhaltens und geringem Energieverbrauch beschleunigen die Arbeiten an dieser Technologie. Somit wird sie wohl zunächst für HighEnd-Anwendungen im Vordergrund stehen, wo der Kunde bereit ist, für aussergewöhnliche Leistungen auch zu zahlen. Neue Impulse könnten aus der attraktiv niedrigen Versorgungsspannung solcher

Bild 11. Querschnitt durch einen Chip mit sechs Metallisierungslagen aus Kupfer. Diese Technik wird sowohl von IBM als auch von Motorola als Sprung in eine neue Dimension für Systems on Silicon gesehen. Beide Firmen stellten erste Chips in dieser Technik vor (Bild: Motorola/IEDM '97).

Chips abgeleitet werden: SOI-Bausteine lassen sich nämlich auch noch unter 1 V Versorgungsspannung betreiben. Den schnellsten CMOS-Schaltkreis der Welt, der in SOI-Technik hergestellt wurde, demonstrierte die IBM aus ihrem Semiconductor Research and Development Center (SRDC) in Hopewell Junction nördlich von New York. Die dortigen Forscher entwickelten einen CMOS-Inverter mit einer Laufzeit von rund 8 Picosekunden. was einer Frequenz von 125 GHz entspricht, und das bei Raumtemperatur und einer Versorgungsspannung von 1,8 V. Verringert man die Versorgungsspannung auf 1,2 V, dann steigt die Laufzeit auf rund 11 ps an, was immer noch ein herausragender Wert ist. Siliconix-Temic aus Santa Clara, Kalifornien, berichtete über einen Leistungs-TrenchFET (FET: Feldeffekttransistor), der bei 30 V Sperrspannung sicher arbeitet. Er stellt einen neuen Rekord auf: Mit mehr als 1 Mio aktiver Zellen ist es der erste Leistungs-FET, der für sich die Klasse ULSI (Ultra-Large Scale Integration) in Anspruch nehmen kann. Im durchgeschalteten Zustand hat das neue Bauelement einen Widerstand von nur 2 m, wozu das Gehäuse noch 1,1 m hinaddiert. Bei diesem FET lässt sich der Lawinendurchbruch sehr gleichmässig steuern (Bild 10), was entscheidend zu dem niedrigen Widerstand im «On»-Status beiträgt.

Matsushita Electronics aus Osaka stellte einen GaAs-Leistungs-FET vor, dessen Temperaturkoeffizient über den ganzen Anwendungsbereich Null ist – das hat es bisher noch nicht gegeben. Man könnte die Gate-Spannung verschieben, um die Temperaturdrift des Drain-Stroms zu kompensieren – das aber beeinflusst die Hochfrequenzanpassung, so dass sich diese Lösung meist nicht anbietet. Durch eine Verschiebung der Gate-Orientierung auf dem GaAs-Kristallgitter bei der Herstellung gelang die Stabilisierung des Temperaturkoeffizienten (TK) über einen Betriebsbereich von -20 bis +100 °C auf nur 2 %. Zum Vergleich: Konventionelle GaAs-Leistungs-FETs haben einen TK in diesem Temperaturbereich von etwa 30%.

LCDs mit Dünnfilmtransistoren (TFT, Thin Film Transistor) gelten heute als eine Domäne der fernöstlichen Industrie, insbesondere der Japaner. Da musste es überraschen, dass die Universität in Princeton mit einer neuen Entwicklung an die Öffentlichkeit ging: Eine Dünnfilm-

transistortechnologie, die mechanisch flexibel und sogar faltbar ist. Die aus amorphem Silizium hergestellten TFTs sind auf einer 0,25 µm dünnen Stahlfolie aufgebracht: Die Transistoren bleiben funktionsfähig, selbst wenn man die Folie auf einen Radius von nur noch 2,5 mm konvex oder konkav krümmt. Die elektrischen Daten oder gar die Funktionsfähigkeit werden dabei nicht beeinflusst. Gegenwärtig arbeitet man daran, auch noch flexible Pixel mit Hilfe von organischen Leuchtdioden zu erarbeiten. Am Ende der Entwicklung steht die Vorstellung, biegsame Displays in Active-Matrix-Technologie zu realisieren, die man beispielsweise in intelligenten, faltbaren Strassenkarten verwenden kann. In das Gebiet der Systems on Chip gehören die von Intel und Motorola unabhängig voneinander vorgetragenen Arbeiten über eine Chiptechnologie für Logikschaltkreise, die sechs metallische Lagen auf dem Chip für die Verdrahtung anbietet. Das grundsätzlich Neue daran ist, dass anstelle von Aluminiumleitungen auf dem Chip nun Kupfer verwendet wird. Aluminium hat den grossen Vorteil, dass es sich gut mit dem Silizium verträgt, welches das Basismaterial für die Chips ist. Es hat aber auch zwei Nachteile: Sein Flächenwiderstand ist vergleichsweise hoch, und es neigt zu sogenannter Elektromigration, d. h. Aluminiumteilchen werden mit dem elektrischen Strom mitgerissen und wandern damit über den Chip. Kupfer hingegen ist zwar wenig siliziumfreundlich, kontaminiert sogar den Chipgrundstoff, hat aber einen viel geringeren Widerstand und vor allem keine Elektromigration. Die beiden Unternehmen trugen ihre ersten Erfahrungen über Chips mit Kupferleiterbahnen vor, die bis zu sechs metallische Lagen aufweisen (Bild 11). Das neue Verfahren ist voll integrierbar in die gängigen 0,25-µm-CMOS-Prozesse.

## Hat die IEDM '97 gehalten, was man sich von ihr versprochen hat?

Die Konferenz hat Tradition und kann viele spektakuläre Premieren in Hardund Software verzeichnen. Die berühmteste von allen lieferte Dr. Gordon

Moore, der seinerzeitige Intel-Chef: Er

prägte auf der IEDM 1975 das nach ihm

benannte Mooresche Law, welches die

Entwicklung der Leistungsfähigkeit von

Chips über der Zeitachse beschreibt. Und

dieses Gesetz, empirisch gefunden und

technisch ausformuliert, hat bis heute

Gültigkeit. Noch jede IEDM hat an solch grosse Tradition angeknüpft. Für manche hier vorgetragene Idee kam aber die grosse Stunde erst später. Ob wir auch in diesem Jahr wieder einer Sternstunde beigewohnt haben, werden wir vielleicht erst in fünf Jahren wissen.

#### **Summary**

#### The leap into the gigarange

The world's most important electronics conference, the International Electronic Devices Meeting (IEDM '97), which took place in Washington, D.C., in December 1997, has demonstrated for the 43rd time that this is where the electronics future is defined and not at the more widely known semiconductor conference that is so highly valued by marketing experts. The participation by companies and nations approximately reflects the market strengths of the semiconductor triade USA/Far East/Europe: 46% of the over 200 papers were presented by Americans, 39% by Asians and the remaining 15% by Europeans. Relative to the previous year the US participation increased significantly: Even if the 'home advantage' of the Americans is taken into consideration, the reinvigorated self-awareness of 'Uncle Sam' is evident in this field.

### Wer seine

### Investitionen

schützen will, kontaktiert ISO-zertifizierte Generalunternehmen.

SOHARD AG

Software/Hardware Engineering Galgenfeldweg 18, CH-3000 Bern 32 Tel. 031 33 99 888, Fax 031 33 99 800 E-Mail: sohard@sohard.ch