**Zeitschrift:** Comtec : Informations- und Telekommunikationstechnologie = information and telecommunication technology

**Herausgeber:** Swisscom

**Band:** 74 (1996)

**Heft:** 3

**Artikel:** Sparclet : die optimale Lösung

**Autor:** Fanet, Alain

**DOI:** <https://doi.org/10.5169/seals-876750>

### Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. [Mehr erfahren](#)

### Conditions d'utilisation

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. [En savoir plus](#)

### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. [Find out more](#)

**Download PDF:** 06.02.2026

**ETH-Bibliothek Zürich, E-Periodica, <https://www.e-periodica.ch>**

## KOMMUNIKATIONSCONTROLLER FÜR DEN GROSSVOLUMIGEN EMBEDDED-MARKT

# SPARCLET: DIE OPTIMALE LÖSUNG

Die Lizenzvereinbarung mit Sun Microsystems versetzt die französische TEMIC-Tochter Matra MHS (Nantes) in die Lage, im Markt für 32-bit-Mikrocontroller entscheidende Akzente zu setzen. Im Rahmen einer technologischen Partnerschaft mit Sun hat Matra MHS ein Mikrocontroller-Konzept mit den Namen SPARClet entwickelt. Erste Produkte auf der Basis dieser neuen Technologie sind bereits auf dem Markt erhältlich.

**E**s handelt sich um einen Kommunikationscontroller, der vor allem zum Einsatz in Netzwerk-Routern, LAN-Bridges, optischen Relais und ISDN-Adaptoren ausgerichtet ist. Daran

ALAIN FANET

anschliessende Produktentwicklungen werden neben dem Kommunikations- oder Netzwerkbereich auch den Automobilsektor oder Video-Processing-Systeme bedienen. Das Unternehmen zielt dabei besonders auf den hochvolumigen Embedded-Markt. Ein optimales Verhältnis zwischen Prozessor-Performance und dem Preis macht den Core speziell für die beschriebenen kostenempfindlichen Embedded-Lösungen interessant.

Die Zusammenarbeit zwischen Sun und der TEMIC begann 1992. Mit dem SPARClet-Konzept verfügt die TEMIC heute über eine zur SPARC-Architektur kompatible, anderseits aber völlig eigenständige Plattform für eine 32-bit-RISC-Prozessor-Technologie.

## Vorhandenes Marktpotential

Forderungen wie eine Realtime-Sprachübertragung oder eine entsprechende Bild- oder Datenkompression sind im Multimediazeitalter die entscheidenden Kriterien für die Auswahl von Mikroprozessoren, Mikro-

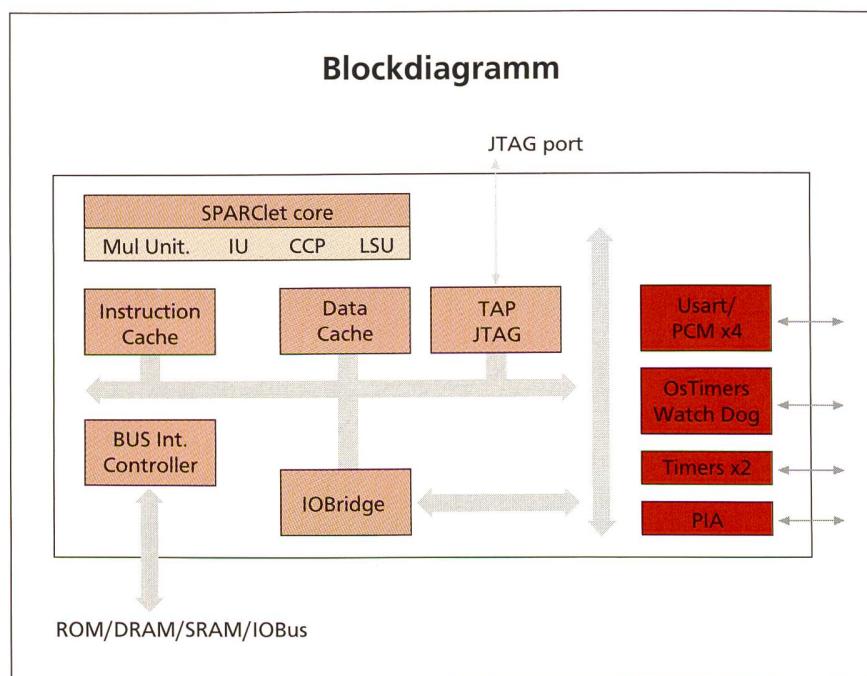

## FEATURES DES 90C701

- ein statischer SPARClet-CPU-Kern (Low-Power-Consumption, Versionen für 30 MHz/3,3 V und 50 MHz/5 V)

- ein 6-KByte-Instruktions-Cache

- 8-KByte-Daten-Cache

- Memory-Controller (DRAM, ROM, SF AM)

- Code/CRC-Coprocessor

- parallele I/Os

- Timer

- USART/PCM

- OTAG mit Boundary-Scan

- zwei Gehäusevarianten: 208-Pin-POFP und 240-Pin-PGA

- 0,6-µ-Strukturen, Dreilagenmetallisierung, CMOS-Technologie

Bild 1. Blockdiagramm 90C701.

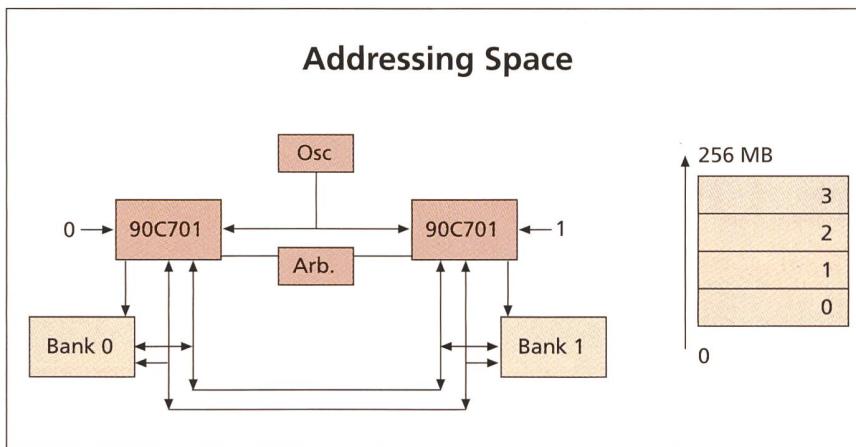

Bild 2. Memory Addressing Space.

stung. Zum anderen reduzieren sich die Systemkosten auch dadurch, dass billigere externe Komponenten, beispielsweise Speicherbausteine, verwendet werden können. Der Grund dafür liegt darin, dass sich der SPARClet weder durch eine parallele Verarbeitung noch im Speicher- oder I/O-Zugriff in seiner Rechenleistung beeinflussen lässt.

## Erste und zweite SPARClet-Generation

«Effective cycle per instruction» – das ist das Prinzip, dem die erste SPARClet-Generation (SPARClet I) folgt. Es werden 1 Mio Befehle pro Sekunde (1 MIPS) und pro Megahertz verarbeitet. Die Bausteine verfügen über eine Dreilagenmetallisierung, 0,6-µ-CMOS-Strukturen und können bei Frequenzen bis zu 70 MHz (70 MIPS) eingesetzt werden. In diesem Fall ist eine Versorgungsspannung von 5 V notwendig. Bei Frequenzen von 50 MHz reichen auch 3 V. Im Laufe von 1996 soll auch ein optimierter 0,5-µ-Prozess für 3-V-Spannung zur Verfügung stehen. Mit der zweiten Generation (SPARClet II) wird die TEMIC 1997 auf den Markt kommen. Dann sollen auf der Basis eines 0,35-µ-Prozesses 3 MIPS pro Megahertz verarbeitet werden. Frequenzen bis zu 100 MHz werden möglich sein.

controllern oder DSPs. Für 1996 schätzen die Auguren deshalb für 16- und 32-bit-Mikrocontroller oder -DSPs eine weltweite Marktgrösse von über 1,4 Mia Dollar ab. Mit 2,7 Mia Dollar wird für das darauffolgende Jahr sogar eine Verdopplung prognostiziert. Die Anwendungen für solch leistungsfähige Architekturen sind vielfältig; um nur einige zu nennen: Fax/Modems, Diskdrives, mobile Kommunikation, digitale Anrufbeantworter, Video-on-Demand, Broadcasting-TV, intelligente PDAs usw.

## SPARClet-Architektur

Digitale Signalprozessoren verfügen, entsprechend ihrem oft ähnlichen Einsatzgebiet, über eine Reihe gleicher, sogenannter General-Purpose-Strukturen. So integriert auch SPARClet eine ganze Reihe von General-Purpose-Architekturen des SPARC. Die erste Erweiterung gegenüber dem zugrunde liegenden Konzept betrifft die stärkere Unterstützung von digitalem Signalprocessing durch zusätzliche Multiplikations- und Additionsbefehle.

Des weiteren basiert der SPARClet-Core zwar auf den RISC-Architekturen des SPARC, ist aber darüber hinaus zusätzlich in der Lage, auch verschiedenartige Operationen parallel abzuarbeiten. Selbst State-of-the-art-Eigenschaften in High-End-Prozessoren, wie Out-of-order-Execution, haben

Eingang in den SPARClet gefunden. So können Speicherzugriffe, die Ausführung skalarer Befehle und sequentieller Multiplikationen in ein und demselben Taktzyklus erfolgen.

## Leistungsvorteile

Durch die Kombination von parallel arbeitenden Ausführungseinheiten und superskalaren Techniken verfügt das SPARClet-Konzept über ein gutes Preis/Performance-Verhältnis für Embedded-Applikationen und enthält gleichzeitig den kompletten SPARC-Befehlssatz. Zum einen verfügt der SPARClet über eine höhere Leistungsfähigkeit bei gleichem Systemaakt oder – im Umkehrschluss – verbraucht weniger Energie bei gleicher Leistung.

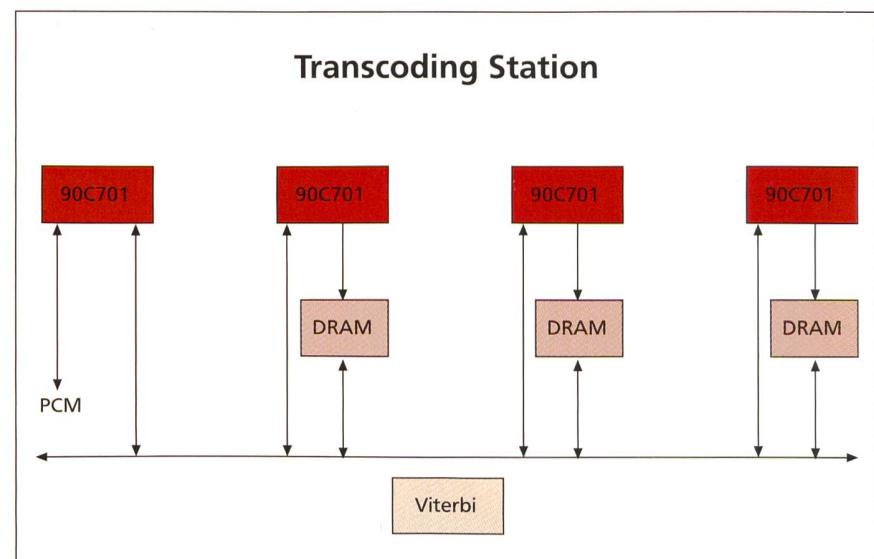

Bild 3. GSM Base Transcoding Station.

## Ein erster Advanced-Communication-Controller

Während des ersten Quartals 1996 wird ein erster SPARClet-Baustein Premiere haben. Dabei wird es sich um den Advanced-Communication-Controller 90C701 handeln. Die integrierte RISC-CPU und eine spezifische Peripherie wurden um Funktionalitäten für ein Mix-Data-Processing und eine Control-Code-Execution erweitert. Der 90C701 kombiniert einen Coprozessor mit bis zu 128 HDLC-Kanälen von 64 kbit/s bis 8 Mbit/s mit einem kompletten DSP. Interessant ist der Controller für Anwendungen in Base-Stations für den GSM-, DECT- oder DCS1800-Standard. Die erste Version des Bausteins wird bei 50 MHz arbeiten.

## TEMIC-ASSP-Strategie

Der Kommunikationscontroller 90C701 ist das erste Mitglied einer ganzen Familie von applikationsspezifischen Standardprodukten (ASSPs),

### SUMMARY

#### Communications controller for the high-volume embedded market

The license agreement with Sun Microsystems enables the French TEMIC subsidiary Matra MHS (in Nantes, France) to make a decisive impact on the 32-bit microcontroller market. Within the framework of a technical partnership agreement with Sun, Matra MHS has developed a microcontroller concept called SPARClet. The first products based on this new technology are already available on the market.

die von vielen Herstellern für ähnliche Anwendungen eingesetzt werden können. Ein weiteres SPARClet-Derivat (90C712) entwickelt die TEMIC derzeit mit einem namhaften Automobilelektronikzulieferer.

Um mit dem SPARClet-Konzept einen weltweit eingesetzten Standard zu etablieren, strebt die TEMIC mittelfristig strategische Partnerschaften an, die die Lizenzvergabe des SPARClet beinhalten.

Dr. Alain Fanet, Verantwortlicher für die Entwicklung der 32-bit-Mikroprozessor-Produkt-Linie bei Matra MHS in Saint Quentin-en-Yvelines.

Quelle:

30. TPC der AEG Daimler-Benz Industrie.

14