**Zeitschrift:** Technische Mitteilungen / Schweizerische Post-, Telefon- und

Telegrafenbetriebe = Bulletin technique / Entreprise des postes, téléphones et télégraphes suisses = Bollettino tecnico / Azienda delle

poste, dei telefoni e dei telegrafi svizzeri

Herausgeber: Schweizerische Post-, Telefon- und Telegrafenbetriebe

**Band:** 66 (1988)

**Heft:** 12

Artikel: Dreidimensionale Integration : Konzepte für multifunktionale IC

Autor: König, Ulf

**DOI:** https://doi.org/10.5169/seals-876272

# Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. Mehr erfahren

# **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. En savoir plus

## Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. Find out more

**Download PDF:** 30.11.2025

ETH-Bibliothek Zürich, E-Periodica, https://www.e-periodica.ch

# Dreidimensionale Integration, Konzepte für multifunktionale IC1

Ulf KÖNIG, Ulm

Zusammenfassung. Die Erhöhung der Packungsdichte integrierter Halbleiterbauelemente ist weiterhin Trend der Halbleitertechnik. Bisher hat man dies durch eine Verringerung der Strukturabmessungen erreicht. Verlockend wäre die Erschliessung der dritten Dimension. Geht man z. B. von einem herkömmlichen Chip von 1 cm² Fläche, besetzt mit einer Vielzahl von Transistoren, aus und versucht, die Bauelemente übereinander anzuordnen, so lässt sich die gleiche Anzahl von Bauelementen in einem Würfel von 1 mm Kantenlänge unterbringen, also auf nur einem Hundertstel der ursprünglichen Chipfläche. Diese Perspektiven waren in der Vergangenheit die Triebfeder der 3-D-Arbeiten, erfordern aber eine kritische Prüfung unter der Einbeziehung technologischer Einschränkungen wie Ausbeute und Wärmeabfuhr.

# Intégration tridimensionnelle, un concept pour circuits intégrés multifonctionnels

Résumé. On observe encore la tendance d'augmenter la densité d'implantation de composants à semi-conducteurs intégrés dans les circuits intégrés. Jusqu'ici, on y parvenait par une diminution des dimensions des structures. A cet égard, il serait tentant de recourir à la troisième dimension. Si l'on tente de superposer sur une puce de 1 cm² de surface les nombreux transistors qui la composent, on parvient à loger le même nombre de composants sur un cube de 1 mm d'arête, c'est-à-dire sur un centième de la surface initiale de la puce. Il y a peu, ces perspectives constituent l'élément moteur des travaux en trois dimensions, bien qu'ils exigent un examen critique tenant compte des limitations technologiques telles que le rendement et l'évacuation de chaleur.

#### Integrazione tridimensionale, progettazione di circuiti integrati multifunzionali

Riassunto. Nella tecnica a semiconduttori si tende sempre più ad aumentare la densità di impaccamento dei componenti integrati. Finora ciò veniva raggiunto con la riduzione delle dimensioni degli elementi. Una soluzione interessante sarebbe quella di sfruttare la terza dimensione. Se si parte per esempio da un chip tradizionale con una superficie di 1 cm², sulla quale si trova un certo numero di transistori e si cerca di disporre i componenti l'uno sull'altro, si può sistemare lo stesso numero di componenti in un cubo con un lato di 1 mm, occupando cioè la centesima parte della superficie originale del chip. Nel passato una tale possibilità ha spinto a effettuare lavori sulla tridimensionalità. Questi lavori devono essere sottoposti tuttavia a un esame critico che tenga conto dei limiti tecnologici relativi, per esempio al rendimento e all'asportazione del calore dissipato.

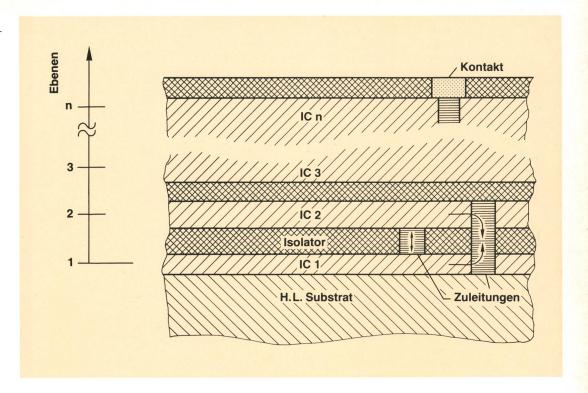

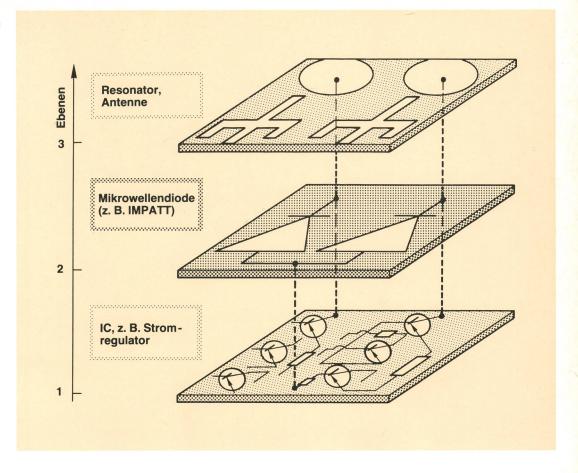

# 1 Prinzip und Bedeutung von 3-D-IC

Man kann sich solche dreidimensionalen Schaltkreise (3-D-IC) als gestapelte Bauelementebenen vorstellen, die jeweils aus mindestens einer Halbleiterschicht (vorzugsweise Si, unter Umständen Halbleiter wie GaAs) bestehen (Fig. 1 und Fig. 2). In jeder Ebene werden die einzelnen Bauelemente mit Verfahren strukturiert, wie sie heute auch bei zweidimensionalen Schaltkreisen eingesetzt werden. Die Bauelementebenen werden durch isolierende Zwischenschichten getrennt. Diskrete Zuleitungen führen von einer Ebene zur anderen. Die elektrische Verbindung zu allen Bauelementebenen erfolgt durch Kontakte auf der obersten Ebene.

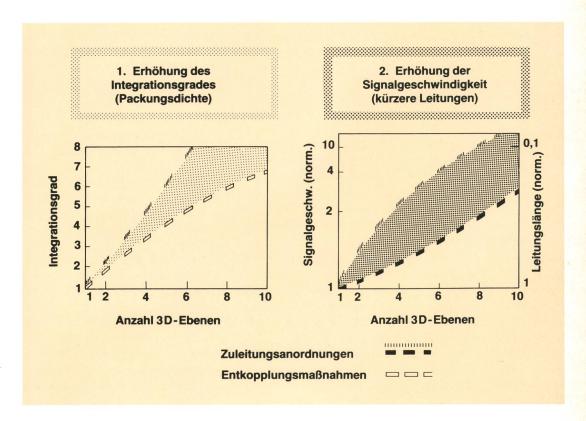

Eine mit der Zahl der Ebenen steigende Packungsdichte bei 3-D-IC ist augenfällig. Für vertikale Zuleitungen ist zwar ein Platzbedarf erforderlich, der aber kaum grösser ist als der enorme Platzbedarf der Zuleitungen bei flächigen IC (50 % und mehr der IC-Fläche). Ausserdem kann der Platz für Zuleitungen durch eine geschickte Aufteilung einer Schaltung in Funktionsblöcke und ihre Anordnung in Ebenen verringert werden (Fig. 3).

Auch bezüglich der Gesamtlänge der Zuleitungen weist 3-D-Anordnung deutliche Vorteile auf. Diese verlaufen grösstenteils vertikal zwischen den in geringem Abstand (voraussichtlich wenige Mikrometer) angeordneten 3-D-Ebenen. Daraus resultieren deutlich höhere Signalgeschwindigkeiten. Erforderlich wird allerdings in Zukunft die Entwicklung 3-D-spezifischer Entwurfsregeln.

Limitierende Faktoren für die Stapelung einer grossen Zahl von 3-D-Ebenen sind die Forderungen nach einer ausreichenden Wärmeabfuhr und nach einer geringen Kapazität der Schaltungen sowie der zurzeit hohe technologische Aufwand zur Herstellung der Ebenen zusammen mit einer drastisch mit der Zahl der Ebenen abnehmenden Ausbeute.

Seit Jahren verfolgt man in Japan mit erheblichem Aufwand das Ziel hoher Packungsdichte durch eine grosse Zahl von Ebenen. Nicht zuletzt wegen der beschränkenden Faktoren ist bisher den japanischen 3-D-Schaltungen der Durchbruch nicht gelungen. Darum setzt die AEG – und inzwischen scheint man dies auch in Japan erkannt zu haben – auf eine andere 3-D-Kategorie, die multifunktionalen 3-D-Systeme, bei denen zwei bis vier Bauelementebenen ausreichen.

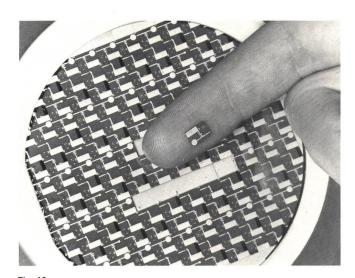

Fig. 1 3-D-IC-Fertigung im Forschungsinstitut Ulm der AEG

<sup>&</sup>lt;sup>1</sup> Vortrag, gehalten am 23. Technischen Presse-Kolloquium der AEG in Kassel

Fig. 2 Prinzip der dreidimensionalen (3-D) Integration

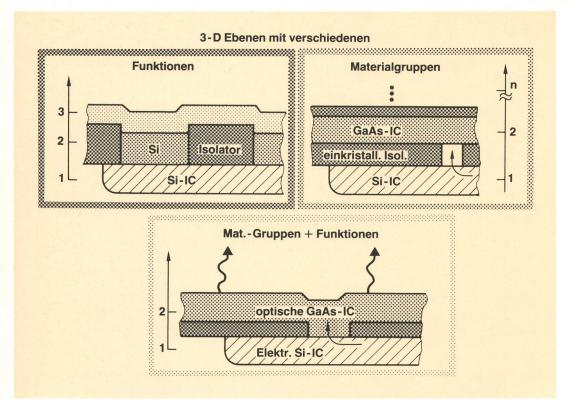

Hierbei werden verschiedenartige Schaltkreise (z. B. analog und digital) oder auch Bauelemente aus verschiedenen Halbleitermaterial-Gruppen (z. B. Si und GaAs) kombiniert (Fig. 4). So können etwa in der ersten Ebene ein konventioneller Silizium-Schaltkreis angeordnet sein, in der zweiten hochkomplexe Vielschicht- oder Heterostruktur-Bauelemente, in der dritten geeignete passive Bauelemente. Denkbar ist auch, dass man einen IC aus einem III/V-Halbleiter (z. B. GaAs) über einen solchen aus Silizium schichtet, getrennt durch eine einkristalline Isolatorschicht, die eine kristallographische Anpassung zwischen den sich in der Gitterstruktur deutlich

unterscheidenden Halbleitergruppen ermöglicht. Die vielleicht interessanteste Variante multifunktionaler 3-D-IC stellt die Stapelung elektronischer Si-IC und optischer GaAs-Bauelemente dar, wodurch kompakte optoelektronische Systeme möglich werden. Dann lassen sich die jeweils herausragenden Materialeigenschaften ausnutzen, einerseits die etablierte Si-Technologie, anderseits die optoelektronischen Eigenschaften der III/V-Halbleiter.

Die Attraktivität derartiger 3-D-Systeme liegt in der Kombinierbarkeit unterschiedlicher Bauelementtypen

Fig. 3 Vorteile der 3-D-Integration (Abschätzung für hochkomplexen Schaltkreis)

515

Fig. 4

Prinzip multifunktionaler

3-D-Systeme

und nicht etwa im Bestreben, eine möglichst hohe Pakkungsdichte zu erreichen. So erwartet man, dass in Zukunft insbesondere multifunktionale 3-D-Systeme an Bedeutung gewinnen werden. Vor etwa 1½ Jahren griff die AEG im Rahmen eines nationalen Verbundvorhabens dieses zukunftsorientierte Forschungsgebiet auf, mit Unterstützung des Bundesministeriums für Technologie (BMFT). Dabei beschreitet die AEG-Forschung völlig neuartige Wege, basierend auf der bereits vor Jahren im Hause entwickelten Technologie der Silizium-Molekularstrahl-Epitaxie (Si-MBE).

# 2 3-D-Technologien

Zum Aufbau von 3-D-Schaltungen kann man zum Teil auf Technologien, wie sie für konventionelle IC benutzt werden, zurückgreifen. Neu zu entwickeln sind allerdings Technologien zur Herstellung der gestapelten Bauelementebenen aus einkristallinen Halbleitern. Grundsätzlich kommen zwei Technologien in Frage. Der vorwiegend eingeschlagene Weg ist die Abscheidung von polykristallinen Halbleitern (insbesondere Polysilizium) auf ein amorphes Material (z. B. SiO<sub>2</sub>), das als Isolator zwischen den aktiven Bauelementebenen dient. Durch einen Rekristallisationsprozess (vorwiegend nach Aufschmelzen mit einem Laser bei Temperaturen über 1000 °C) wird das Polysilizium in monokristallines Silizium (Monosilizium) umgewandelt.

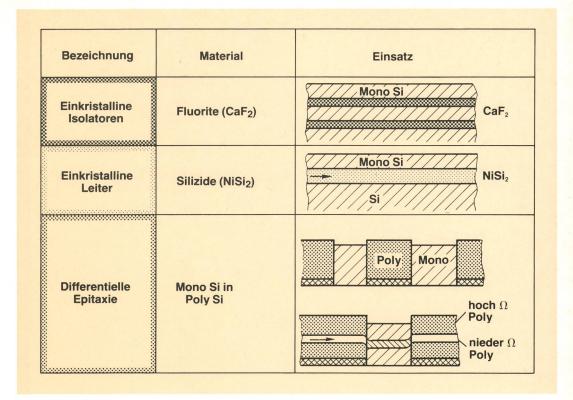

Neuartige Techniken setzen modernste Epitaxieverfahren wie die Si-MBE ein. Sie ermöglicht die direkte Herstellung einkristalliner Halbleiterschichten sowie die Herstellung einkristalliner Isolatoren (wie CaF<sub>2</sub> mit einem zum Si-Kristallgitter passenden Gitterabstand) oder auch die Herstellung einkristalliner Leiter wie das Nikkelsilizid (NiSi<sub>2</sub>). So können beliebige 3-D-Schichtenfolgen aus aktiven Bauelementen, im Wechsel mit Isolatoren oder Leitern, aufgebaut werden. Weiterhin kann man in einem Prozessschritt mit der differentiellen Epi-

taxie monokristalline Halbleiterinseln für aktive Bauelemente in einem «See» aus polykristallinem Halbleitermaterial herstellen (Fig. 5).

Relativ geringe Temperaturen (etwa 550 °C) reichen zum Wachsen der MBE-Schichten aus, niedrig genug auch, um die thermische Beschädigung einer darunterliegenden Bauelementebene zu verhindern.

In der AEG-Forschung wird vorwiegend die differentielle Epitaxie eingesetzt. Ihr Potential liegt bei den multifunktionalen Systemen, ermöglicht aber auch die Stapelung gleichartiger Bauelemente in verschiedenen Ebenen. Die Bedeutung der differentiellen Epitaxie für künftige 3-D-Bauelemente beruht auf den herausragenden Eigenschaften des Polysiliziums, das bei dieser Depositionstechnologie an das simultan gewachsene Monosilizium grenzt:

- Polysilizium ist ein Isolator mit einem etwa 106fach höheren Widerstand als von entsprechend dotiertem Monosilizium. Somit eignet sich das Polysilizium zur seitlichen elektrischen Trennung aktiver Bauelemente in den Monosiliziuminseln.

- Polysilizium ist ein Leiter mit einem dem Monosilizium entsprechenden Widerstand, wenn es nur hoch genug im 1-cm³-Bereich dotiert ist. Damit eignet sich das Polysilizium auch als seitliche Zuleitung zu Monosiliziuminseln.

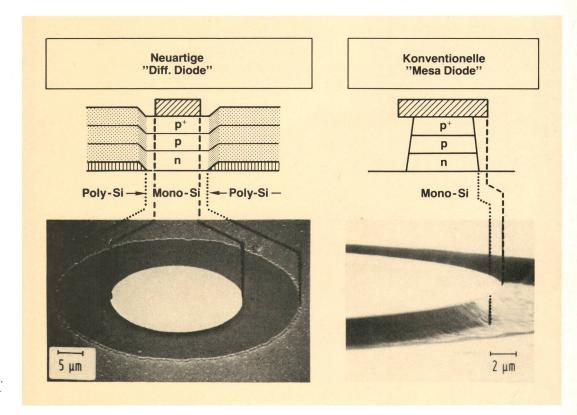

Besondere Aufmerksamkeit ist der Grenze zwischen Monosilizium und Polysilizium zu widmen, in erster Linie wenn der Monosilizium-Bereich, wie für moderne Bauelemente üblich, aus einer Vielzahl von Halbleiterschichten besteht. Die geforderte Isolation durch Polysilizium setzt auch voraus, dass die Bauelementschichten nicht über die Monosilizium/Polysilizium-Grenze hinweg kurzgeschlossen werden. Diese Bedingung ist in der Tat erfüllt, wie Untersuchungen an neuartigen «differentiellen Dioden» (Fig. 6) bewiesen haben, die – anders als kon-

Fig. 5 Zu 3-D-Technologien: Einsatzgebiete der MBE (Molekularstrahlepitaxie)

ventionelle, luftisoliert zu bezeichnende Mesa-Dioden – von isolierendem Polysilizium umgeben sind und deshalb eine nahezu planare Oberfläche besitzen.

Ohnehin ist die differentielle MBE-Diode ein Testbauelement mit Schlüsselfunktion, weil es die Einsetzbarkeit der Technologie der differentiellen MBE für die geplanten 3-D-Bauelemente demonstriert. Man findet nämlich die differentielle Diode als wesentliche Teilkomponente in den 3-D-Konzepten wieder.

# 3 3-D-Konzepte und Versuchsmuster

Die Eignung der differentiellen MBE als neuartige Auftragstechnologie für 3-D-Bauelemente wird anhand einiger Konzepte und Versuchsmuster verdeutlicht. AEG steht damit am Anfang einer Entwicklung, die zurzeit ausschliesslich von ihr verfolgt wird, mit interessanten Perspektiven für die Zukunft.

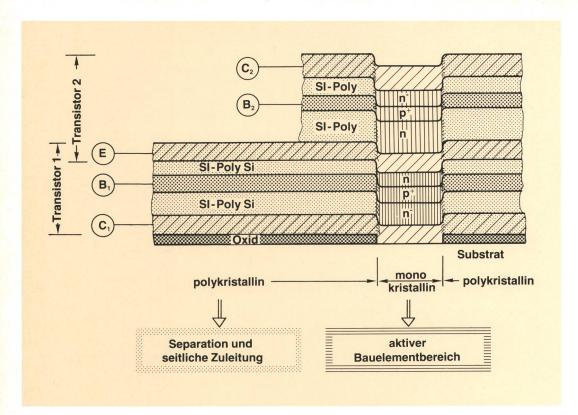

Ein erstes Konzept stellt die Stapelung von mindestens zwei Transistoren dar (Fig. 7). Die aktiven Bauelemente

Fig. 6 Schlüsselbauelement (differentielle Diode): Eignung der MBE-Technologie für 3-D-Systeme. Vergleich mit konventioneller Diode

Fig. 7 Konzept gestapelter (3-D-)Transistoren, integrierbar mit der Technik der «differentriellen MBE» (Separation durch Polysilizium)

liegen im monokristallinen Bereich, der von simultan gewachsenem, polykristallinem Material umgeben ist. Die Transistorschichten können entweder alle aus Silizium bestehen (im Falle eines konventionellen Bipolarttransistors), vorzugsweise aber aus Gründen eines höheren Bauelementwirkungsgrades aus unterschiedlichem Material, wie Silizium und SiGe (Heterobipolartransistor). Zwischen die Bauelementebenen ist eine dünne, gut leitende Schicht eingeschoben – empfehlenswert ist Silizid –, die als gemeinsamer Emitterkontakt beider Transistoren dient und zudem seitlich vom polykristallinen Bereich her an den aktiven Bauelementbereich heranführt. Ähnlich lassen sich auch die Basis- und die Kollektorschichten seitlich kontaktieren.

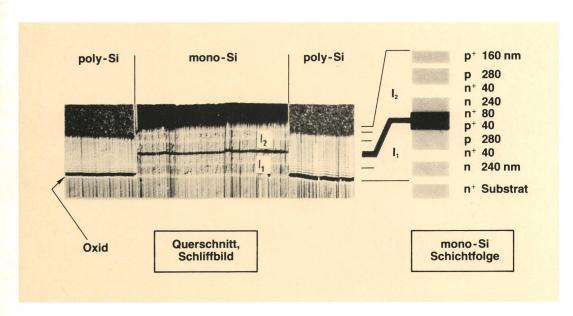

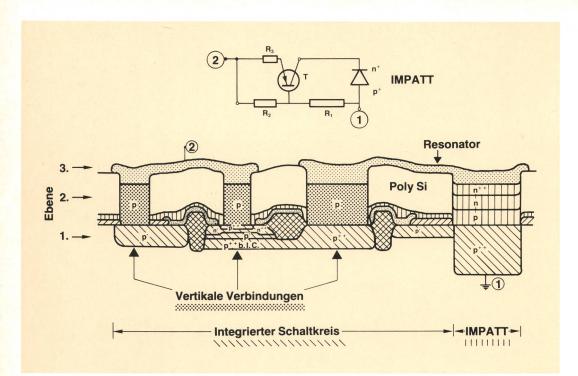

IMPATT-Dioden (impact avalanche transit time) wurden bereits in einer 3-D-Anordnung integriert (Fig. 8). Der

vielschichtige Monosiliziumbereich ist von Polysilizium umgeben, das als einheitliche isolierende Begrenzung dient. Um die Kontaktqualität zwischen den beiden Bauelementen zu verbessern, wurden zwei zusätzliche, hochdotierte, sehr dünne (40 nm und 80 nm) Schichten eingeschoben, die im polykristallinen Bereich aus Kapazitätsgründen entfernt wurden. Diese kompakte 3-D-Anordnung serieller IMPATT-Dioden, die als 90-GHz-Oszillatoren Verwendung finden, zielt einerseits auf eine höhere HF-Leistung hin, anderseits auf eine monolithische Integration mit anderen Bauelementen, die möglicherweise in einer weiteren 3-D-Ebene angeordnet sind. Dabei wird vorzugsweise die Technologie der seitlichen Kontaktierung über gut leitendes Polysilizium angewendet.

Figur 9 zeigt schematisch einen sogenannten intelligenten Mikrowellensender in 3-D-Anordnung mit drei Ebe-

Fig. 8 Realisiertes 3-D-Bauelement aus zwei gestapelten IMPATT

Fig. 9 Multifunktionales 3-D-IC: Geregelter Mikrowellensender (schematisch)

nen. Es ist ein multifunktionaler 3-D-Schaltkreis, der, wie eingangs definiert, in jeder Ebene Bauelemente unterschiedlicher Funktionen besitzt. Die Mikrowellendioden sind in der zweiten Ebene angeordnet, verbunden mit der ersten Ebene, die als stromregulierender integrierter Schaltkreis ausgebildet ist, und mit der dritten Ebene, die den Resonator sowie die in Streifenleitungstechnik ausgebildete und die Mikrowellenleistung abstrahlende Antenne aufnimmt. Eine entsprechende 3-D-Anordnung auf der Empfängerseite, bestehend aus Empfangsantenne in der oberen, Mischerdiode in der mittleren und Signalverarbeitung in der unteren Ebene, ist ebenso vorstellbar.

Fig. 10

Erste Muster von 3-D-IC für Höchstfrequenz

Bei Einsatz der differentiellen MBE präsentiert sich im konkreten Fall ein derartiger dreidimensional angeordneter, in Siliziumtechnik ausgeführter Millimeterwellen-IC (kurz 3-D SIMMWIC) wie in Figur 10 und in Figur 11 gezeigt wird. Nach Herstellung der unteren IC-Ebene, meist in konventioneller Technik, kommt als neue Technologie die differentielle MBE für die zweite 3-D-Ebene zum Einsatz. Diese Ebene nimmt nicht nur die aktive Oszillatordiode auf, sondern ausserdem auch die erforderlichen vertikalen Zuleitungen von der ersten zur zweiten und zur dritten Ebene. Die Zuleitungszonen sind ebenso wie der Diodenbereich aus monokristallinem Silizium durch geeignet dotiertes Polysilizium voneinander elektrisch isoliert. Diese vertikalen Bereiche in der zweiten Ebene lassen sich auch als Widerstände dimensionieren. Dadurch kann gegebenenfalls die Zahl der Widerstände in der ersten Ebene verringert werden, was gleichbedeutend mit einer weiteren Erhöhung der Pakkungsdichte der 3-D-Anordnung ist.

In der dritten Ebene, auf dem isolierenden Polysilizium, sind Zuleitungen, Resonator und Antenne angeordnet. Eine Komponente dieser Anordnung, die vom Polysilizium umgebene IMPATT-Diode, entspricht der bereits getesteten differentiellen MBE-Diode. Zurzeit wird an einer Integration mit den weiteren Komponenten dieses Konzepts gearbeitet.

Ausgehend von der bisherigen Forschung kann man folgende mögliche Einsatzgebiete von 3-D-Schaltungen sehen:

Resultierend aus den bei 3-D-Anordnungen erwarteten k\u00fcrzeren Leitungen ergeben sich Einsatzm\u00f6glichkeiten voraussichtlich dort, wo eine schnelle Signal-

Fig. 11 3-D-SIMMWIC (Silizium-Millimeterwellen-IC): Realisierungsvorschlag mit der Technik der «differentiellen MBE»

verarbeitung bzw. ein schneller Zugriff zu Speicherplätzen erforderlich ist, wie in der Digitaltechnik. In dieser Hinsicht ist auch der durch 3-D-Anordung erreichbare hohe Integrationsgrad von Interesse mit der Konsequenz, deutlich mehr Transistoren auf gleicher Fläche unterzubringen.

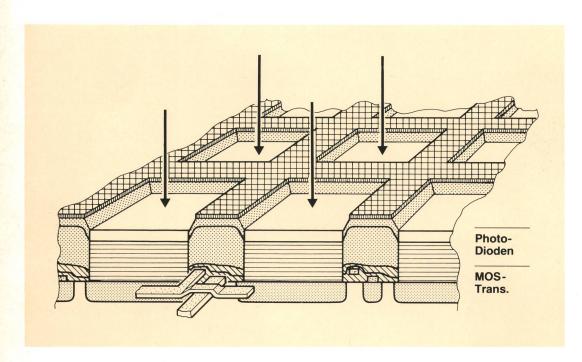

Dank der Kompaktheit multifunktionaler 3-D-Systeme sind diese dort einsetzbar, wo Spezialbauelemente mit ihrer eigenen Ansteuer- oder Ausleseelektronik gekoppelt werden sollen, besonders in Arrays aus diesen Bauelementen. Hierbei zeichnen sich Anwendungen in der Millimeterwellentechnik (z. B. Doppler-Radarantennen) ab. Damit sei noch ein Blick in die Zukunft bei optoelektronischen Arrays geworfen. Entscheidendes Kriterium ist hier die Pixeldichte. Eine Vielzahl von Zuleitungen in der Fläche von den einzelnen Bildpunkten bis zu der zugehörigen, meist weit entfernten Elektronik begrenzt bisher die Bildpunktdichte. Dies löst man dreidimensional, indem man nun die Elektronik *unter* dem optischen Bauelement anordnet (Fig. 12).

#### 4 Schlussfolgerungen

Insgesamt ergeben sich aus der 3-D-Integration faszinierende Entwicklungen für IC von morgen, mit denen die Miniaturisierung erneut weitergetrieben werden kann, die aber auch Eigenschaften erwarten lassen, die bisher nicht darstellbar waren.

Fig. 12 Dreidimensional angeordnetes Bildsensor-Array mit Auslesetransistoren