**Zeitschrift:** Technische Mitteilungen / Schweizerische Post-, Telefon- und

Telegrafenbetriebe = Bulletin technique / Entreprise des postes, téléphones et télégraphes suisses = Bollettino tecnico / Azienda delle

poste, dei telefoni e dei telegrafi svizzeri

Herausgeber: Schweizerische Post-, Telefon- und Telegrafenbetriebe

**Band:** 55 (1977)

**Heft:** 12

**Artikel:** Les équipements de multiplexage numériques pour le service

téléphonique

Autor: Probst, Pierre-André

**DOI:** https://doi.org/10.5169/seals-874164

# Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. Mehr erfahren

# **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. En savoir plus

# Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. Find out more

**Download PDF:** 09.12.2025

ETH-Bibliothek Zürich, E-Periodica, https://www.e-periodica.ch

# Les équipements de multiplexage numériques pour le service téléphonique

Pierre-André PROBST, Berne

621.376.56:621.391.31.037.37:621.395.43.037.37

# Digital-Multiplexeinrichtungen für Telefondienste

Zusammenfassung. Nachdem Eigenschaften der normalisierten PCM-Multiplexer kurz erwähnt sind, werden die Grundsätze der synchronen und der asynchronen Multiplexierung mit Stopftechnik erläutert. Es wird gezeigt, dass in einem plesiochronen Netz die Anwendung hochstabilisierter Taktgeber die synchrone Multiplexierung ermöglicht, unter der Bedingung, dass die Phasensprünge des restituierten Signals angenommen werden können. Zum Schluss werden die Multiplexer mit positiver Stopfung beschrieben, die vom CCITT und von der CEPT empfohlen sind.

Résumé. Après un bref rappel des caractéristiques des multiplexeurs MIC normalisés, les principes du multiplexage synchrone et asynchrone par justification sont exposés. On montre que, dans un réseau plésiochrone, l'utilisation d'horloges à haute stabilité rend possible le multiplexage synchrone, à condition que des discontinuités de phase du signal restitué soient acceptées. Enfin, les multiplexeurs à justification positive des hiérarchies numériques recommandés par le CCITT et la CEPT sont décrits.

### L'apparecchiatura di multiplazione numerica per il servizio telefonico

Riassunto. Ad una breve presentazione delle caratteristiche dei multiplatori PCM normalizzati, segue una relazione sui principi della multiplazione sincrona e asincrona «pulse stuffing» (bit riempitivi). Si illustra come in una rete plesiocroma, l'impiego di orologi ad alta stabilità crea la premessa per la multiplazione sincrona, a condizione che le discontinuità di fase del segnale restituito siano accettate. Da ultimo, sono descritti i multiplatori con tecnica a «pulse stuffing» positiva delle successioni numeriche raccomandate dal CCITT e dalla CEPT.

#### 1 Introduction

Les systèmes de transmission numériques sont structurés en différents niveaux hiérarchiques correspondant chacun à un débit d'information ou à un nombre de voies téléphoniques codées en MIC. Le principe de la modulation par impulsion et codage (MIC) ainsi que des réalisations de multiplexeurs MIC et de systèmes de lignes correspondants ont été décrits dans de nombreuses publications. Le but du présent article est d'examiner, après une brève revue des principaux systèmes MIC existants, les procédés de multiplexage permettant d'atteindre les niveaux supérieurs de la hiérarchie. Enfin, on trouvera les caractéristiques des multiplexeurs numériques normalisés au CCITT¹ et à la CEPT².

# 2 Importance des systèmes de transmission numérique

Les principes de la modulation par répartition dans le temps (MRT) et de la transmission de signaux numériques semblent au premier abord être des inventions récentes. Pourtant, si l'on jette un regard sur l'histoire des télécommunications, on s'aperçoit que les premiers essais de transmission d'information utilisèrent des codes à éléments discrets. Par exemple, le télégraphe aérien inventé par Chappe, et exploité à partir de 1794 sur la ligne Paris-Lille, utilisait un bras mobile pouvant être placé dans un certain nombre de positions par l'opérateur. Chaque position correspondait à un angle défini du bras par rapport à l'horizontale [1]. Le code se composait ainsi d'un certain nombre d'éléments discrets. Le multiplexage de signaux dans le temps est également une invention ancienne puisque, en 1853, un inventeur américain nommé Farmer multiplexait des signaux de télégraphie à l'aide de commutateurs rotatifs. Le système fut ensuite appliqué aux signaux de parole en 1903 par Miner [2].

Faute de composants adéquats, la technique de l'échantillonnage et du multiplexage par répartition dans le temps dut céder le pas à la modulation par répartition de fréquence (MRF). Cependant, les travaux de recherches continuèrent activement et, en 1937, A. H. Reeves inventait, dans les laboratoires ITT à Paris, le principe de la modulation par impulsion et codage (MIC).

Les études sur le système MIC se poursuivirent aux Etats-Unis et, en 1948, les résultats publiés par différents chercheurs parmi lesquels *C. E. Shannon* permettent d'affirmer que les bases théoriques de cette technique étaient acquises. De plus, ces travaux donnèrent la preuve que ce type de modulation est applicable aux signaux de téléphonie. Ce n'est cependant qu'avec l'avènement des semi-conducteurs que l'invention de Reeves put se concrétiser sous forme d'équipements répondant aux exigences requises de fiabilité et de coût.

La mise en service des premiers systèmes MIC date des années de 1960. Depuis lors, les rapides progrès réalisés dans la fabrication des semi-conducteurs et l'invention des circuits intégrés, réunissant dans un espace réduit une multitude de fonctions, ont permis de diminuer les dimensions des équipements tout en améliorant leurs performances et leur fiabilité.

Pour qu'une nouvelle technique s'impose, il ne suffit pas qu'elle offre des performances équivalentes pour le même prix que la technique déjà établie, il faut encore que les avantages soient suffisamment importants pour couvrir les investissements annexes pour son introduction (par exemple, élaboration de nouvelles bases de planification, instruction du personnel, équipements de mesure, etc.).

En ce qui concerne la technique numérique, les principaux avantages sont les suivants:

- Sensibilité moins grande aux perturbations du canal de transmission qu'un signal analogique

- Qualité de la liaison téléphonique pratiquement indépendante de la longueur

- Possibilité de transmettre avec les mêmes équipements différents services tels que données, téléphonie, télévision, fac-similé

<sup>&</sup>lt;sup>1</sup> Comité Consultatif International Télégraphique et Téléphonique

<sup>&</sup>lt;sup>2</sup> Conférence Européenne des Administrations des Postes et des Télécommunications

- Réalisation avisée d'équipements de commutation permettant d'envisager des réseaux entièrement numériques sur lesquels différents services peuvent être commutés et transmis [3]

- Meilleure utilisation des câbles existants

Ce dernier point est valable en ce qui concerne les câbles à paires symétriques, tels qu'ils sont utilisés dans le réseau rural. Par contre, si l'on compare les capacités en voies téléphoniques entre les systèmes analogiques et numériques pour les transmissions interurbaines sur paire coaxiale, le résultat est en faveur de la technique analogique. Par exemple, sur la paire coaxiale de petit diamètre 1,2/4,4 mm, un système MRF à 12 MHz transmet 2700 voies téléphoniques avec un champ d'amplification de 2 km, tandis qu'un équipement de ligne en technique numérique, avec le même pas de régénération, offre une capacité de 1920 voies à un débit de 140 Mbit/s.

L'intérêt de la technique numérique réside, par conséquent, dans les possibilités d'intégration des services de la commutation avec la transmission et permet surtout de disposer de systèmes convenant parfaitement à la transmission de données sans exiger de transcodage complexe. A ces avantages vient s'ajouter le fait que la technique numérique est bien adaptée à certains milieux de transmission, en particulier aux fibres optiques et aux guides d'ondes millimétriques.

Il est fort probable qu'à très longue échéance les réseaux de télécommunication seront entièrement numériques jusqu'à l'abonné. En partant des réseaux actuels, cela signifie que, pendant de nombreuses années encore, les systèmes analogiques et numériques devront cohabiter et coopérer pour assurer l'acheminement du trafic. Cette longue période de transition exige que les travaux de recherches et de normalisation ne s'orientent pas seulement sur les équipements numériques, mais aussi sur les systèmes «hybrides», destinés à interconnecter le réseau analogique avec le réseau numérique et inversement.

#### 3 Multiplexeurs

Du fait que les systèmes de transmission numériques peuvent être empruntés par différents services, on distingue entre multiplexeurs MIC et multiplexeurs numériques. Dans le langage courant, les multiplexeurs des deux types avec leurs systèmes de lignes sont souvent appelés «systèmes MIC». En réalité, cette désignation n'est pas exacte puisque seul le multiplexeur MIC utilise pour le traitement des voies téléphoniques la modulation par impulsion et codage. Les voies, une fois codées, peuvent être multiplexées ou démultiplexées numériquement, exactement de la même façon qu'un signal de données.

Quant aux systèmes de ligne, ils sont caractérisés par leur débit binaire qu'ils transmettent généralement sans distinction du contenu (principe de l'indépendance de la séquence des bits).

#### 31 Multiplexeurs MIC

Le lecteur est prié de se référer à la bibliographie [2, 4] en ce qui concerne le principe de la modulation par impulsion et codage, seules les grandes lignes seront rappelées ici.

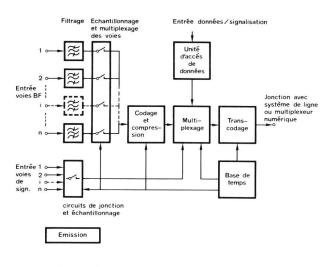

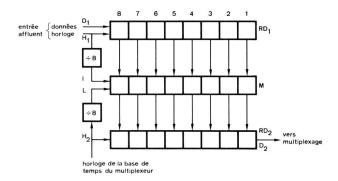

rig. 1 Schéma simplifié d'un multiplexeur MIC

Un multiplexeur MIC opère les fonctions suivantes:

- Codage et décodage des voies basse fréquence

- Traitement de la signalisation associée à ces voies

- Multiplexage et démultiplexage des voies codées, y compris la synchronisation et les éléments binaires de service

- Transcodage du signal résultant en un code compatible avec l'interface

- Surveillance du fonctionnement, déclenchement des alarmes et actions correspondantes

Le schéma-bloc simplifié d'un multiplexeur MIC est représenté dans la *figure 1*. En plus des fonctions mentionnées ci-dessus, l'équipement peut être pourvu d'une unité donnant accès à un ou plusieurs intervalles de temps de la trame. A la place des voies téléphoniques correspondantes, on dispose ainsi d'un ou de plusieurs canaux numériques utilisables pour la transmission de données. On peut appliquer le même principe pour l'intervalle de temps de la trame réservé à la signalisation, si le multiplexeur des canaux de signalisation associé aux voies téléphoniques est réalisé sous forme d'équipement séparé ou lorsque la signalisation sur voie commune est utilisée.

Dans la figure 1, le circuit de codage est utilisé en multiplex de temps par les signaux de voies, ce qui exige du circuit une fiabilité suffisante. Dans divers pays on a, pour diverses raisons, adopté un circuit de codage/décodage voie par voie. Fabriqué en très grandes séries sous forme de circuit intégré, le codec voie par voie est certainement moins onéreux que le système commun à toutes les voies équipé de son circuit de surveillance. Une implantation à

grande échelle d'un tel circuit intégré est en tout cas nécessaire si l'on veut transmettre l'information en technique numérique jusqu'à l'abonné (conversion analogue/numérique et inversement dans l'appareil de l'abonné).

# 32 Multiplexeurs MIC normalisés

Au sein du CCITT et de la CEPT, les travaux de normalisation ont fait de substantiels progrès au cours de ces dernières années. Les premières recommandations du CCITT furent approuvées par la quatrième et la cinquième assemblée plénière en 1968 et 1972, puis publiées dans les livres blancs³ et verts (avis de la série G) [5]. Ces travaux n'auraient évidemment pas pu progresser si, dans un certain nombre de pays, des équipements n'avaient été développés auparavant.

En Suisse, les premiers essais eurent lieu de 1963 à 1965 et la mise en service des premiers systèmes remonte à 1969. Fondés sur des normes nationales, ils sont connus sous la désignation de «systèmes à code B».

Sur le plan international, les systèmes recommandés par le CCITT sont spécifiés dans les avis de la série G 700 relatifs aux caractéristiques des systèmes numériques, à savoir:

- G 703 Caractéristiques générales des jonctions (interfaces)

- G 711 Modulation par impulsion et codage (MIC) des fréquences vocales

- G 712 Caractéristiques de qualité des voies MIC aux fréquences vocales

- G 731 Equipements de multiplexage MIC primaires pour fréquences vocales

- G 732 Caractéristiques des équipements de multiplexage MIC primaires fonctionnant à 2048 kbit/s

- G 733 Caractéristiques des équipements de multiplexage MIC primaires fonctionnant à 1544 kbit/s

- G 744 Equipement de multiplexage MIC du second ordre fonctionnant à 8448 kbit/s

L'équipement spécifié par l'avis G 733 est celui qui a été adopté principalement par les Etats-Unis, le Canada et le Japon, tandis que le système à 2,048 Mbit/s de l'avis G 732 résulte de travaux de normalisation effectués à la CEPT et au CCITT par les administrations européennes. Les caractéristiques des multiplexeurs MIC mentionnés cidessus sont résumées dans le *tableau I*.

# 33 Multiplexeurs numériques

Un équipement de multiplexage numérique a pour fonction de former, à partir d'un certain nombre d'affluents, un signal composé de l'information des affluents, de la synchronisation nécessaire au démultiplexage et des indications de service multiplexées dans le temps. L'opération est purement numérique et fait appel, en ce qui concerne sa réalisation, aux circuits logiques. On verra plus loin que, selon le type de multiplexeur, certaines parties utilisent quelques éléments de circuits analogiques (boucle à verrouillage de phase).

Tableau I. Caractéristiques des multiplexeurs MIC

| Système MIC<br>Avis CCITT                            | Primaire<br>G 732     | Primaire<br>G 733   | Primaire<br>- (Code B) | Secondaire<br>G 744   |

|------------------------------------------------------|-----------------------|---------------------|------------------------|-----------------------|

| Codage des<br>voies BF                               |                       |                     |                        |                       |

| Fréquence<br>d'échantillonnage<br>Genre de code pour | 8 kHz                 | 8 kHz               | 8 kHz                  | 8 kHz                 |

| les voies<br>Nombre d'éléments                       | Binaire               | Binaire             | Ternaire               | Binaire               |

| de code par voie BF Nombre de niveaux                | 8 bit                 | 8 bit               | 5                      | 8 bit                 |

| de quantification                                    | 2 <sup>8</sup> = 256  | $2^8 - 1 = 255^1$   | 3 <sup>5</sup> = 243   | 28 = 256              |

| Nombre de<br>segments de la<br>caractéristique de    |                       |                     |                        |                       |

| compression Débit binaire de la                      | 13 (loi A)            | 15 (loiμ)           | 7                      | 13 (loi A)            |

| voie BF codée                                        | 64 kbit/s             | 64 kbit/s           | 80 kbit/s²             | 64 kbit/s             |

| Signal multiplex                                     |                       |                     |                        |                       |

| Nombre de voies BF<br>Nombre d'intervalles           | 30                    | 24                  | 30                     | 120, 127/1284         |

| detemps<br>Longueur de la                            | 32                    | 24                  | 32                     | 132                   |

| trame                                                | 256 bit               | 193 bit³            | 320 bit                | 1056 bit              |

| Traitement de la                                     | Par                   | Par                 | Par                    | Par                   |

| signalisation voie<br>par voie                       | multitrame            | multitrame          | multitrame             | multitrame            |

| Débit binaire du                                     | 0.040 111             |                     | 0.50.111.              |                       |

| signal multiplex<br>Code à la jonction               | 2,048 Mbit/s<br>HDB 3 | 1,544 Mbit/s<br>AMI | 2,56 Mbit/s<br>B       | 8,448 Mbit/s<br>HDB 3 |

- 1 On réserve deux signaux de caractère pour l'amplitude zéro

- 2 Ce débit résulte du transcodage des 5 éléments ternaires en 10 éléments binaires (code B)

- 3 Un bit par trame est attribué au verrouillage de trame et de multitrame

- 4 Dépendant du système de signalisation (voie par voie; 120 voie commune: 127/128)

#### 331 Multiplexage synchrone

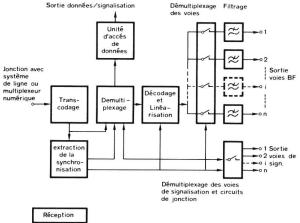

L'opération de multiplexage peut s'effectuer de différentes façons, selon que le signal de rythme des affluents est synchronisé ou non avec l'horloge du multiplexeur. Dans le cas où ces deux signaux sont synchrones entre eux, le débit du signal résultant est égal à la somme des débits des affluents, auxquels vient s'ajouter le mot de verrouillage de trame et les éléments numériques réservés aux indications de service. L'équipement correspondant est le multiplexeur synchrone dont le principe de fonctionnement est indiqué dans la *figure 2*. Les affluents en

Fig. 2 Principe de fonctionnement d'un multiplexeur synchrone

<sup>&</sup>lt;sup>3</sup> On trouve dans le livre blanc (1968) l'avis G 711 dans une première version

provenance d'un autre multiplexeur ou d'un système de ligne sont connectés par l'intermédiaire d'une unité de jonction 1. Le circuit situé à l'entrée de cette unité assure la mise en phase des signaux entrants avec ceux qui sont générés par la base de temps du multiplexeur. Par rapport à ces derniers, les affluents sont affectés d'un décalage de phase constant auquel peuvent être superposées des fluctuations de phase (gigue) provoquées par les systèmes de transmission (ligne et multiplexeur). Si l'amplitude de cette gigue dépasse une certaine valeur, il est nécessaire de l'absorber à l'aide d'une mémoire tampon.

Les unités de jonction (1) et (3) assurent encore la régénération du signal entrant, le transcodage entre le code de jonction et le code binaire (et inversement). Elles peuvent également assurer des fonctions de surveillance, telle que la détection de la perte du signal entrant ou d'un signal caractéristique.

L'opération de multiplexage proprement dite s'effectue dans l'unité (2). On distingue l'entrelacement des bits de celui des intervalles de temps des affluents. Dans l'entrelacement des bits, le signal résultant s'obtient par multiplexage cyclique, bit par bit, des affluents. Il est possible de prélever périodiquement un groupe de bits à chaque affluent et de les multiplexer. Si le train binaire des affluents comporte une structure de trame, elle-même divisée en intervalles de temps composés par exemple de 8 bit, on peut procéder par entrelacement cyclique de ceux-ci.

Cette dernière méthode exige la présence d'un circuit de synchronisation dans l'unité de jonction (1) capable d'extraire les intervalles de temps, car, si les horloges des affluents sont synchrones avec celles du multiplexeur, les signaux obtenus par division des signaux qu'elles produisent ne sont pas toujours en phase. Enfin, un procédé encore plus restrictif consiste à attribuer à chaque intervalle de temps du signal résultant un intervalle de temps précis des affluents, c'est-à-dire que la trame des affluents et celle du signal résultant ont une relation de phase fixe et définie. Il convient de remarquer que l'entrelacement des intervalles de temps impose une restriction quant à l'indépendance de la séquence des bits du signal à l'entrée du multiplexeur, puisque cette méthode exige une structure de trame particulière de l'affluent, indépendamment du service transmis.

Lorsque l'horloge du multiplexeur et celles des affluents fonctionnent en plésiochronisme, c'est-à-dire que les fréquences nominales sont identiques, mais que chaque horloge peut s'écarter indépendamment l'une de l'autre dans des limites spécifiées, on distingue deux cas, selon l'ordre de grandeur des stabilités respectives. En fonctionnement plésiochrone à haute stabilité (par exemple  $\triangle f/f = 10^{-11}$ , f: fréquence de l'étalon), il est possible de multiplexer les affluents selon le même principe que pour les signaux synchrones, à condition de pouvoir tolérer de temps à autre la perte ou la répétition d'un groupe de bits. La figure 3 représente le circuit de conversion d'horloge de l'unité de jonction dans laquelle les signaux des affluents sont pris en charge par l'horloge interne du multiplexeur (ici, comme exemple par groupe de 8 bit). Les données sont d'abord inscrites avec leur propre rythme dans un registre à décalage RD<sub>1</sub>, dont le contenu est transféré tous les 8 bit dans la mémoire intermédiaire M par l'impulsion I issue d'un circuit diviseur par 8. La base de temps du multiplexeur syn-

Fig. 3 Principe de la conversion d'horloge dans l'interface

RD<sub>1, 2</sub> Registre à décalage M Mémoire intermédiaire

D<sub>1</sub>, H<sub>1</sub> Données et horloge de l'affluent

D<sub>2</sub>, H<sub>2</sub> Données de l'affluent et horloge du multiplexeur Impulsion d'inscription dans la mémoire

Impulsion de lecture de la mémoire

thétise, à partir de son horloge pilote, le signal de rythme  $H_2$ , dont la division par 8 donne l'impulsion de lecture L, qui transfère le contenu de la mémoire M dans le registre à décalage de sortie RD<sub>2</sub>.

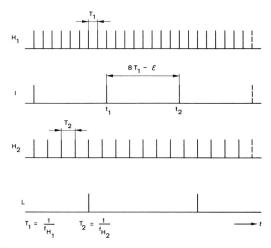

Les données sont ensuite disponibles en série pour l'opération de multiplexage avec les signaux d'autres affluents traités à l'aide du même circuit. Lorsque les horloges H, et H2 sont plésiochrones, le déphasage entre les impulsions de lecture et d'inscription est une fonction du temps. Comme le contenu de la mémoire change tous les 8 bit, aussi longtemps que l'impulsion de lecture L se trouve entre deux impulsions d'inscription I, il n'y aura ni perte ni répétition d'information. Dans l'exemple de la figure 3, le déphasage peut atteindre 8  $T_1$  -  $\mathcal{E}$ , où  $T_1$  est la période d'un bit et  $\mathcal E$  une marge fonction des tolérances des impulsions et du temps nécessaire au transfert des informations. La figure 4 illustre les phases relatives entre les différents signaux, dans le cas où l'horloge du multiplexeur est plus lente que celle de l'affluent, c'est-à-dire que le contenu de la mémoire inscrit au temps t, est renouvelé à t2 sans avoir été lu. Le groupe de 8 bit situé entre t<sub>1</sub> et t<sub>2</sub> n'apparaît pas à la sortie du registre RD<sub>2</sub>. Les données restituées au démultiplexeur sont donc amputées de 8 bit. Dans le cas inverse, où l'horloge H2 est plus rapide que  $H_1$  ( $T_2 < T_1$ ), chaque accumulation de phase su-

Fig. 4 Phases relatives des signaux du circuit de conversion d'horloge ( $T_2 > T_1$ )

périeure à 8  $T_1 - \mathcal{E}$  provoque la répétition d'un groupe de 8 bit. La période d'un tel glissement est fonction de la précision relative des deux horloges  $H_1$ ,  $H_2$  et de la capacité de la mémoire. Cette dernière fixe la grandeur du déphasage tolérable, tandis que la précision relative détermine le temps avec lequel ce déphasage est atteint.

Le temps entre deux pertes ou répétitions d'information, lorsque les deux horloges ont une précision relative  $\alpha$ , est donné par l'expression:

$$t = \frac{\triangle \tau}{\alpha}$$

où  $\wedge \tau$  est le déphasage tolérable en [s].  $\alpha$  est défini comme l'écart Af entre les deux fréquences f, et f2 des horloges H1 et H2 respectivement, rapporté à la fréquence de référence par exemple f<sub>1</sub>. Dans le cas où l'affluent a un débit de 2,048 Mbit/s, et si le circuit d'entrée comporte une mémoire à 8 bit en négligeant C ( $\mathcal{E} \approx$  O), le déphasage tolérable  $\Delta \tau$  est égal à 3,9  $\mu$ s. Si l'on admet le cas le plus défavorable, où chaque horloge oscille à l'extrémité de son domaine de tolérance  $\pm$  10<sup>-11</sup>,  $\alpha$  est alors égal à 2  $\cdot$  10<sup>-11</sup> et le temps t est de 1,95 · 105 s. Ainsi, approximativement toutes les 54 heures et 15 minutes, chaque conversion d'horloge provoquera un glissement de 8 bit. Par rapport aux 4 · 1011 bit transmis dans ce même laps de temps, et compte tenu du taux d'erreur apporté par la transmission, cette altération des performances est sans doute acceptable. Cependant, les conséquences d'une perte ou de la répétition d'un certain nombre de bits ne sont pas les mêmes que celles dues aux erreurs de transmission, car si l'affluent contient une structure de trame, la synchronisation restera possible aussi longtemps que le taux d'erreur n'excède pas une certaine valeur, tandis qu'un glissement raccourcit ou rallonge la trame, provoquant ainsi une perte de verrouillage au démultiplexage. Il est possible d'atténuer les conséquences d'une telle perte de synchronisation en indiquant à l'utilisateur l'instant où se produit le glissement, ou de provoquer celui-ci lorsque le trafic est faible ou même nul.

Pour des multiplexeurs à débit plus rapide que 2,048 Mbit/s, la périodicité des glissements, dans le cas le plus défavorable, est naturellement plus petite que la valeur indiquée plus haut, car, pour une capacité de la mémoire fixe et une stabilité de l'horloge de référence  $\alpha$ , le déphasage tolérable  $\triangle \tau$  est inversement proportionnel à la fréquence  $f_{H_1}$ . La seule possibilité d'augmenter la période des glissements est une plus grande capacité de la mémoire. On se trouve devant deux exigences qui, du point de vue technologique, ne sont pas faciles à concilier: à la fois capacité et vitesse d'accès élevées. La question de savoir si cette technique est applicable à tous les échelons de la hiérarchie est fonction de la fréquence des glissements que l'on peut accepter dans une liaison internationale comportant plusieurs conversions de rythme.

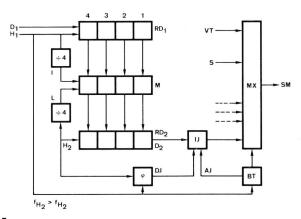

# 332 Multiplexage asynchrone

Si les horloges ne sont pas suffisamment stables, la méthode décrite précédemment n'est plus réalisable, car la capacité de la mémoire devient trop élevée. On a alors recours au multiplexage asynchrone basé sur le principe de

Fig. 5

Circuit de conversion d'horloge dans le multiplexage par justification positive

Registre à décalage R<sub>1, 2</sub> MX Circuit de multiplexage IJ Circuit d'insertion de l'élément de justification Comparateur de phase в́т Base de temps Verrouillage de trame VT Eléments de service SM Signal multiplexé  $D_1$ ,  $D_2$ Données de l'affluent H<sub>1</sub>, H<sub>2</sub> Horloges Inscription Lecture

DJ Demande de justification

AJ Autorisation de justification

la justification4, qui consiste à modifier le débit de l'affluent de telle façon qu'il puisse être pris en charge par le débit attribué à chaque affluent dans le multiplexeur. Trois cas peuvent se présenter selon la relation entre ces deux débits. Dans la justification positive, le débit réservé à chaque affluent est légèrement supérieur à son débit initial maximal. La fréquence des impulsions de lecture est plus élevée que la fréquence des inscriptions dans la mémoire M (fig. 5). Avant qu'un glissement se produise, un dispositif logique va bloquer pour la durée d'un bit la lecture de cette mémoire et insérer, en un endroit précis de la trame, un bit appelé élément numérique de justification et ne contenant pas d'information. La présence de ce bit est signalée par les éléments numériques de service de justification, contenus dans la trame, à l'équipement de démultiplexage, qui opère son extraction, puisqu'il n'est pas porteur d'information. Le multiplexeur met donc à disposition de chaque affluent un débit variable à valeurs discrètes, destiné à absorber les différences de rythme.

Dans la figure 5, on retrouve un circuit d'entrée identique à celui des multiplexeurs synchrones, doté, en plus, d'un comparateur de phase, duquel sont issues les demandes de justification, c'est la base de temps qui autorise, à l'instant présent dans la trame, l'insertion de l'élément numérique de justification.

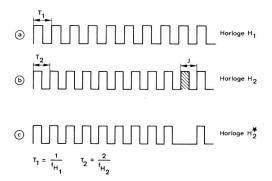

Dans l'équipement de démultiplexage, la base de temps reçoit, par l'intermédiaire des éléments numériques de service, l'indication que l'affluent correspondant contient dans la trame, à l'endroit prescrit, un bit ne portant pas d'information et opère son extraction. La figure 6 représente les horloges du train binaire original (a) d'un affluent, puis celles du signal avec justification (b) et après extraction du bit de justification (c). L'horloge du signal restitué (c) pré-

<sup>&</sup>lt;sup>4</sup> Le terme justification est également connu sous la désignation «bourrage» (en anglais Stuffing)

sente une discontinuité de phase chaque fois qu'un bit de justification est extrait et sa fréquence  $f_{\rm H_2}$  est supérieure à la fréquence initiale  $f_{\rm H_1}$  (entre les discontinuités); en revanche, sa fréquence moyenne, obtenue par lissage à l'aide d'une boucle à verrouillage de phase, est égale à la fréquence initiale.

Le principe de la justification *négative* repose également sur l'adaptation du débit de l'affluent. A ce dernier est attribué un débit plus faible que son débit minimal ( $f_{\rm H_2} < f_{\rm H_1}$ ).

Avant l'apparition d'un glissement, la logique va extraire un bit du signal de l'affluent et le transmettre, dans un endroit précis de la trame, à l'équipement distant. Ce bit, porteur d'information, est réinjecté dans l'affluent par le démultiplexeur.

Enfin, la justification *positive-négative* représente une combinaison des deux méthodes décrites ci-dessus. Le débit disponible à chaque affluent au multiplexage et son débit propre ont la même valeur nominale.

Les deux horloges étant plésiochrones entre elles, les variations provoquées par leurs tolérances vont conduire à une justification positive, une justification négative ou pas de justification. Par conséquent, le démultiplexeur reçoit des éléments numériques de justification de trois ordres possibles: justification positive, pas de justification ou justification négative. Ce procédé augmente la complexité de l'équipement. Cependant, il est possible de réaliser un multiplexage avec justification positive-négative, basé sur la transmission de deux ordres seulement [5].

En fonctionnement plésiochrone, le multiplexage par justification garantit l'indépendance de la séquence des bits des affluents, sans perte d'information, ce qui représente un avantage par rapport au principe de multiplexage synchrone et des glissements qui en résultent. Pourtant, si l'échange des ordres relatifs à la justification entre les multiplexeurs n'est pas suffisamment protégé contre les erreurs de transmission, le circuit de déjustification peut, par exemple, extraire par erreur un bit d'information, provoquant ainsi un glissement. De même, dans le cas de la justification négative, un ordre erroné provoquera, par exemple, l'introduction d'un bit étranger dans la trame de l'affluent. Les conséquences sont donc les mêmes que dans le multiplexage synchrone avec glissements, c'est-àdire perte de verrouillage de trame dans les démultiplexeurs d'ordres inférieurs. Cela met en évidence l'importance d'une bonne protection.

Fig. 6 Restitution de l'horloge de l'affluent au démultiplexeur (justification positive ( $T_1 > T_2$ )

J Emplacement de l'élément numérique de justification

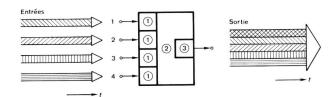

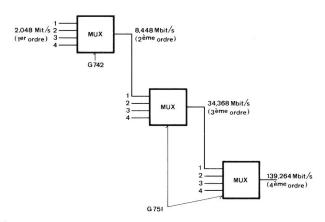

Fig. 7 Hiérarchie numérique basée sur le débit primaire de 2,048 Mbit/s

MUX Multiplexeur

G 742 G 751 } Avis du CCITT dans lesquels les équipements sont recommandés

Une autre caractéristique du multiplexage asynchrone par justification est la production de gigue de phase qui se superpose au signal restitué après démultiplexage. Cette gigue provoquée par la justification et le multiplexage est en partie filtrée par une boucle à verrouillage de phase dans le circuit de sortie du démultiplexeur.

Les propriétés de cette gigue ainsi que la protection des processus de justification sont sujets d'une publication à paraître [6].

# 34 Multiplexeurs numériques normalisés

La présence de deux multiplexeurs MIC primaires normalisés a conduit sur le plan international à la spécification de deux hiérarchies séparées. En effet, les équipements basés sur le débit primaire à 2048 kbit/s ne sont à aucun niveau compatibles avec ceux qui sont basés sur le débit à 1544 kbit/s. La seule possibilité d'interconnexion se situe au niveau 64 kbit/s et comporte certaines restrictions.

La hiérarchie numérique adoptée par la plupart des pays européens est indiquée dans la figure 7. On notera, comme particularité, le multiplexage numérique de quatre affluents et l'entrelacement cyclique des bits indépendamment du niveau. Tous les équipements font appel à la justification positive et peuvent donc être engagés dans un réseau plésiochrone. Les spécifications relatives à ces équipements figurent dans les avis G 742 et G 751 [7]. Cette dernière recommandation prévoit une variante d'équipement entièrement compatible avec ceux de la figure 7 qui opère un multilpexage direct du 2e au 4e ordre. Les caractéristiques principales de ces multiplexeurs sont résumées dans le tableau II. Chaque affluent dispose d'un bit par trame pour la justification, correspondant au débit maximal de justification, tandis que le débit nominal est égal à la différence entre le débit attribué à chaque affluent dans le signal résultant à 2,112 kHz (fréquence nominale du multiplexeur) et le débit nominal de l'affluent. Par exemple, le multiplexeur du 2e ordre dispose par affluent d'un débit de 378 bit par trame, c'est-à-dire de 8457,75 kbit/s. Conformément au principe de la justification positive, ce débit est supérieur de 9,75 kbit/s au débit nominal de l'affluent (8448 kbit/s).

Pour assurer une protection suffisante des indications de justification contre les erreurs, le nombre de bits est

Tableau II. Caractéristiques des multiplexeurs numériques basés sur le débit binaire du premier ordre à 2,048 Mbit/s

| Niveau hiérarchique                                 | 2e ordre                    | 3e ordre                    | 4º ordre                     |

|-----------------------------------------------------|-----------------------------|-----------------------------|------------------------------|

| Débit du signal                                     | 8,448 Mbit/s                | 34,368 Mbit/s               | 139,264 Mbit/s               |

| multiplexé                                          | ± 30 · 10-6                 | ± 20 · 10-6                 | ± 15 · 10-6                  |

| Nombre d'affluents                                  | 4                           | 4                           | 4                            |

| Débit des affluents                                 | 2,048 Mbit/s<br>± 50 • 10-6 | 8,448 Mbit/s<br>± 30 · 10-6 | 34,368 Mbit/s<br>± 20 · 10-6 |

| Intervalles de temps à                              |                             |                             |                              |

| 64 kbit/s¹                                          | 120                         | 480                         | 1920                         |

| Longueur de la trame<br>Signal de verrouillage de   | 848 bit                     | 1536 bit                    | 2928 bit                     |

| trame                                               | 1111010000                  | 1111010000                  | 1111110100000                |

| Nombre de groupes<br>Nombre de bits par affluent et | 4                           | 4                           | 6                            |

| par trame                                           | 206                         | 378                         | 723                          |

| Nombre de bits de justifi-                          | 200                         | 0.0                         | 1.20                         |

| cation par trame et par                             |                             |                             |                              |

| affluent                                            | 1                           | 1                           | 1                            |

| Nombre de bits de service                           |                             |                             |                              |

| de justification par affluent                       | 3                           | 3                           | 5                            |

| Indication de justification                         |                             |                             |                              |

| positive                                            | 111                         | 111                         | 11111                        |

| Indication d'absence de                             |                             |                             |                              |

| justification                                       | 000                         | 000                         | 00000                        |

| Fréquence nominale de                               |                             | 00 075 111                  | 47.50.111                    |

| répétition de la trame                              | 9,96 kHz                    | 22,375 kHz                  | 47,56 kHz                    |

| Débit maximal de justifi-                           | 0.00 1.1.1.                 | 00 075 1.6:4/-              | 47 EC Lb:+/-                 |

| cation par affluent                                 | 9,96 kbit/s                 | 22,375 kbit/s               | 47,56 kbit/s                 |

| Débit nominal de justification                      | 4,23 kbit/s                 | 9,75 kbit/s                 | 19,93 kbit/s                 |

| Code à la jonction (sortie                          | HDB 3                       | HDB 3                       | CMI <sup>2</sup>             |

| du multiplexeur)                                    | ט מעוו                      | ט טטוו                      | OMI                          |

<sup>1</sup> Disponibles pour transmettre de l'information (= nombre de voies codées en MIC)

impair (3 et 5) et lorsque le démultiplexeur décode des combinaisons autres que «tout un» ou «tout zéro», un circuit logique prend une décision en faveur de l'état majoritaire. Si, par exemple, le démultiplexage de la trame du 4° ordre indique dans la combinaison des éléments numériques 3 bit dans l'état «1», la logique décide qu'il y a eu justification au multiplexeur et déclenche les actions appropriées.

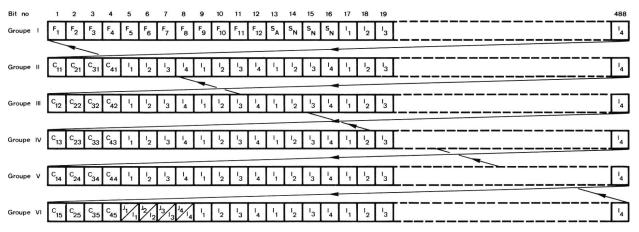

La figure 8 représente la structure de trame du 4° ordre divisé en 6 groupes de 488 bit chacun. Le signal de verrouillage de trame occupe les 12 premières positions du groupe I et il est suivi par 4 bit de service. Les groupes

suivants commencent tous par les éléments numériques de service de justification. Enfin, les positions 5, 6, 7 et 8 du groupe VI sont, soit occupées par des bits d'information, soit par les éléments numériques de justification des affluents 1, 2, 3 ou 4. Si, par exemple, le mot formé par les bits  $C_{31}$ ,  $C_{32}$ ,  $C_{33}$ ,  $C_{34}$  et  $C_{35}$  est 11111, la position n° 7 du groupe VI est occupée par un élément numérique de justification  $J_3$  à extraire avant la restitution du signal de l'affluent n° 3 au démultiplexage.

Le débit normalisé le plus haut de la hiérarchie numérique basée sur le débit primaire de 2,048 Mbit/s est actuellement de 139,264 Mbit/s. La définition d'un 5° ordre devrait être possible dans les prochaines années, car divers systèmes à haute capacité existent déjà au stade expérimental (400 Mbit/s et plus).

Du point de vue de la flexibilité d'exploitation, il semble raisonnable de multiplexer 4 affluents à 139,264 Mbit/s pour obtenir un débit du 5° ordre aux environs de 565 Mbit/s. Mais les caractéristiques des supports de transmission existants doivent également être prises en considération. D'après des études préliminaires [8], le débit optimal en ce qui concerne le câble à paires coaxiales 2,6/9,5 mm correspondrait au multiplexage de 6×139,264 Mbit/s (environ 850 Mbit/s).

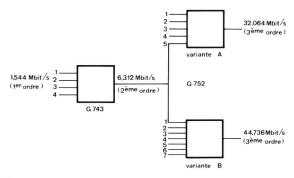

La hiérarchie numérique basée sur le débit primaire de 1,544 Mbit/s est normalisée jusqu'au 3e ordre. La figure 9 représente les équipements recommandés par le CCITT [7]. Ce 3e ordre comporte deux variantes distinctes, dont les débits et les trames ne sont pas compatibles. Le multiplexage à 32,064 Mbit/s a été adopté par le Japon tandis que l'Amérique du Nord utilise 7 affluents pour former une trame à 44,737 Mbit/s. Les spécifications relatives à ces équipements sont résumées dans le tableau III. Le multiplexage s'effectue aussi par justification positive et entrelacement cyclique des bits. Comme particularité, il faut mentionner la structure de multitrame du multiplexeur secondaire et de la variante B du multiplexeur tertiaire. Bien qu'un accord n'ait pas pu être réalisé quant à la normalisation des 4e et 5e ordres, des propositions ont déjà été faites au CCITT. Pour le Japon, ce sont les débits de 100 Mbit/s

Fig. 8 Structure de la trame du 4º ordre (139,264 Mbit/s)

F<sub>1</sub>...F<sub>12</sub> Signal de verrouillage de trame (11111010000)

S<sub>A</sub> Indication d'alarme

S<sub>N</sub> Bits réservés pour usage national

$S_N$  Bits réservés pour usage national  $I_1, I_2, I_3, I_4$  Bits d'information des affluents nos 1, 2, 3 et 4 respectivement

$C_{j1}...\,C_{j5}$

Eléments numériques de service de justification du le affluent

J<sub>1,</sub> J<sub>2,</sub> J<sub>3</sub>, J<sub>4</sub> Eléments numériques de justification des affluents n°s 1, 2, 3 et 4 respectivement

respectivemen

<sup>2</sup> CMI = Abréviation de «coded mark inversion» (code à deux niveaux)

Fig. 9 Hiérarchie numérique basée sur le débit primaire de 1,544 Mbit/s

MUX Multiplexeur

G 743 G 752 Avis du CCITT dans lesquels les équipements sont recommandés

et pour l'Amérique du Nord, le  $4^{\circ}$  ordre est celui du système LD-4 274,176 Mbit/s ( $6\times44,736$  Mbit/s).

En ce qui concerne la justification positive/négative, un équipement a fait l'objet d'une normalisation, il s'agit du

Tableau III. Caractéristiques des multiplexeurs numériques basés sur le débit binaire du premier ordre 1,544 Mbit/s

| Niveau hiérarchique                     | 2° ordre                    | 3e ordre<br>(variante A)     | 3e ordre<br>(variante B)     |

|-----------------------------------------|-----------------------------|------------------------------|------------------------------|

| Débit du signal multiplexé              | 6,312 Mbit/s<br>± 30 · 10-6 | 32,064 Mbit/s<br>± 10 · 10-6 | 44,736 Mbit/s<br>± 20 · 10-6 |

| Nombre d'affluents                      | 4                           | 5                            | 7                            |

| Débit des affluents                     | 1,544 Mbit/s<br>± 50 · 10-6 | 6,312 Mbit/s<br>± 30 · 10-6  | 6,312 Mbit/s<br>± 30 · 10-6  |

| Intervalles de temps à                  |                             |                              |                              |

| 64 kbit/s                               | 96                          | 480                          | 672                          |

| Longueur de la trame                    | 2942 bit                    | 1920 bit                     | 6807 bit                     |

| Signal de verrouillage de<br>trame      | 013                         | 11010/00101<br>alterné       | 10018                        |

| Nombre de groupes                       | 6                           | 6                            | 8                            |

| Nombre de bits par affluent             | "                           | 0                            | ľ                            |

| et par trame                            | 2884                        | 378                          | 672                          |

| Nombre de bits de                       |                             |                              |                              |

| justification par trame et par          |                             |                              |                              |

| affluent                                | 14                          | 1                            | 1                            |

| Nombre de bits de service               |                             |                              |                              |

| de justification par affluent           | 3                           | 3                            | 3                            |

| Indication de justification<br>positive | 111                         | 111                          | 111                          |

| Indication d'absence de                 | 111                         | 111                          | 1111                         |

| iustification                           | 000                         | 000                          | 000                          |

| Fréquence nominale de                   | 000                         | 000                          | 000                          |

| répétition de la trame                  | 5.37 kHz                    | 16,7 kHz                     | 9,4 kHz                      |

| Débit maximal de                        |                             |                              |                              |

| justification par affluent              | 5,37 kbit/s                 | 16,7 kbit/s                  | 9,4 kbit/s                   |

| Débit nominal de justification          | 1,795 kbit/s                | 0,6 kbit/s                   | 3,67 kbit/s                  |

| Code à l'interface                      | B6ZS⁵ ou AMI                | AMI avec                     |                              |

| (sortie du multiplexeur)                | avec brouilleur             | brouilleur                   | B3ZS <sup>9</sup>            |

- 1 Disponibles pour transmettre de l'information (= nombre de voies codées en MIC)

- 2 On forme une multitrame composée de quatre trames (4 X 294 = 1176 bit) dont le signal de verrouillage (011x) est formé par le premier bit du groupe I de chaque trame (x = élément numérique de service)

- 3 Le signal de verrouillage de trame 01 occupe la première position dans le groupe III et le groupe VI

- 4 Par multitrame

- 5 Code bipolaire qui substitue à une séquence de 6 zéros consécutifs le mot 0 + 0 + ou 0 + 0 + -

- 6 Code bipolaire strict (alternate Mark inversion)

- 7 Le signal se compose d'une multitrame formée de 7 trames (4760 bit). Le signal de verrouillage de multitrame est constitué du premier bit de chaque trame. XXYY010 (X, Y éléments numériques de service)

- 8 Premier bit des groupes II, IV, VI et VIII

- 9 Code bipolaire à substitution de trois zéros

multiplexeur numérique de second ordre fonctionnant à 8,448 Mbit/s dont les caractéristiques sont fixées par l'avis G 745.

Mis à part les systèmes mentionnés jusqu'ici, il existe un certain nombre de multiplexeurs dont le débit du signal multiplexé ne correspond pas à un niveau hiérarchique, par exemple, les systèmes à 120 Mbit/s développés au Royaume-Uni ou ceux qui sont exploités en France avec un débit de 52 Mbit/s.

Enfin, pour compléter la liste, il faut mentionner les multiplexeurs de données, de signaux radiophoniques et de télévision dont les caractéristiques sont à l'étude. Les travaux effectués dans ces domaines sont axés sur la compatibilité avec les systèmes déjà normalisés pour la téléphonie

# 4 Système de lignes

Les problèmes spécifiques du système de ligne feront l'objet d'une publication ultérieure, quelques remarques générales seront mentionnées ici. Du point de vue fonctionnel, le régénérateur et le terminal d'une ligne à faible débit ne se distinguent pratiquement pas de ceux d'une ligne à grand débit. Si les fonctions sont identiques, les exigences, les performances et l'environnement sont totalement différents.

Les systèmes à faible capacité sont conçus en premier lieu pour être engagés sur des câbles à paires symétriques construits, à l'origine, pour la transmission de signaux basse fréquence. Le régénérateur doit s'accommoder de caractéristiques électriques souvent médiocres aux fréquences utilisées. La présence d'autres services dans le câble, dont les spectres de fréquence peuvent se chevaucher, pose un sérieux problème de compatibilité (télex, télédiffusion haute fréquence, signalisation à courant continu).

A partir du deuxième ordre hiérarchique, les systèmes de ligne sont engagés sur des câbles à paires coaxiales ou sur des paires symétriques spécialement construites pour la transmission numérique. Les principales perturbations avec lesquelles le développement du système doit tenir compte sont le bruit thermique, les réflexions provoquées par les irrégularités d'impédance [8], les signaux induits par diaphonie et la pollution électromagnétique.

Les débits hiérarchiques normalisés des multiplexeurs répondent, avant tout, aux critères de flexibilité d'exploitation et ne correspondent pas obligatoirement à une utilisation optimale du milieu de transmission. Selon la configuration du réseau existant et des câbles disponibles, il est concevable qu'à un débit hiérarchique ne corresponde pas de système de ligne.

On trouvera par conséquent deux catégories de systèmes de ligne, ceux dont le débit correspond à un niveau hiérarchique et ceux dont la capacité est dictée par d'autres critères.

Sur le plan international, les travaux de normalisation sont en cours, et il n'existe pas encore d'avis sur les équipements de ligne proprement dits. Notons pour terminer que, dans le cadre de la CEPT, le code HDB 3 a été normalisé comme code en ligne pour les systèmes à 2,048 Mbit/s et 8,448 Mbit/s.

#### 5 Conclusions

Les considérations qui précèdent ont montré que la normalisation de la hiérarchie numérique européenne est fort avancée en ce qui concerne les équipements de multiplexage à justification positive. Cette technique permet la numération du réseau lorsque les horloges des multiplexeurs aux divers niveaux hiérarchiques sont synchrones ou plésiochrones. L'introduction du multiplexage synchrone, à condition de disposer d'horloges de référence à haute stabilité, pourrait constituer une solution à envisager, selon la fréquence des glissements que l'on peut tolérer. L'équipement de multiplexage synchrone présente comme avantage une complexité moins grande et n'introduit pas de gigue sur les affluents.

#### **Bibliographie**

- [1] Charbon P. Le télégraphe et sa chronique. Paris, Revue Française des Télécommunications (1974) n° 12.

- [2] Cattermole K. W. Principles of pulse code modulation. London, Iliffe Books Ltd (1969).

- [3] Wuhrmann K. E. Le système de télécommunication intégré MIC IFS-1. Berne, Bull. Techn. PTT 51 (1973) n° 12, p. 554...578.

- [4] Kündig A. Digitale Telephonie. Bern und Stuttgart, Hallwag Verlag (1972).

- [5] CCITT. Livre vert, Tome III (cinquième assemblée plénière, Genève 1972). Publié par l'UIT (1973).

- [6] Coppex G. Considérations sur le multiplexage numérique. A paraître dans le Bulletin technique PTT.

- [7] CCITT. Document AP VI n° 66. VI° assemblée plénière. Genève (1976).

- [8] Käser A. Influence des irrégularités d'impédance des paires coaxiales sur la transmission numérique. Berne, Bull. Techn. PTT 55 (1977) nº 7, p. 322...336.

# Die nächste Nummer bringt unter anderem Vous pourrez lire dans le prochain numéro

G. Bieri Modellanlage für die digitale Vermittlung von Transitverbindungen im Integrierten Fernmeldesystem (IFS)

Installation pilote pour la commutation numérique de communications en transit dans le réseau de télécommunications intégré IFS

E. Vogel Zur formellen Beschreibung von Echtzeitsystemen