|                     |                                                                                                                                                                                                                                                   |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Zeitschrift:</b> | Technische Mitteilungen / Schweizerische Post-, Telefon- und Telegrafenbetriebe = Bulletin technique / Entreprise des postes, téléphones et télégraphes suisses = Bollettino tecnico / Azienda delle poste, dei telefoni e dei telegrafi svizzeri |

| <b>Herausgeber:</b> | Schweizerische Post-, Telefon- und Telegrafenbetriebe                                                                                                                                                                                             |

| <b>Band:</b>        | 51 (1973)                                                                                                                                                                                                                                         |

| <b>Heft:</b>        | 2                                                                                                                                                                                                                                                 |

| <b>Artikel:</b>     | Circuits monolithiques intégrés MOS                                                                                                                                                                                                               |

| <b>Autor:</b>       | Leuenberger, Fritz                                                                                                                                                                                                                                |

| <b>DOI:</b>         | <a href="https://doi.org/10.5169/seals-875276">https://doi.org/10.5169/seals-875276</a>                                                                                                                                                           |

### Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. [Mehr erfahren](#)

### Conditions d'utilisation

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. [En savoir plus](#)

### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. [Find out more](#)

**Download PDF:** 29.12.2025

**ETH-Bibliothek Zürich, E-Periodica, <https://www.e-periodica.ch>**

# Circuits monolithiques intégrés MOS

Fritz LEUENBERGER, Neuchâtel

621.38.049.75 - 181.4

## Integrierte monolythische MOS-Schaltungen

**Zusammenfassung.** Nach einem Vergleich der heute üblichen Technologien zur Herstellung von integrierten MOS-Schaltungen einerseits und integrierten bipolaren Schaltungen anderseits folgt ein kurzer Überblick über die dynamischen logischen MOS-Schaltungen. Sodann wurden die komplementären MOS-Schaltungen behandelt, die durch eine der Frequenz proportionale Leistungsaufnahme charakterisiert sind. Die Vorteile einer neueren MOS-Technologie, die als Steuerelektrode eine polykristalline Siliziumschicht verwendet, sind eingehend erläutert. Die Verwendung von komplementären MOS-Schaltungen in dynamischen logischen Schaltungen und der MOS-Transistor, der zur Reduktion der Schaltkapazitäten auf einem isolierenden Substrat hergestellt wird, gelangen als Beispiel weiterer Verbesserungen des Leistungsverbrauches und Grenzfrequenz zur Diskussion.

**Résumé.** Après une comparaison des technologies actuelles de fabrication des circuits intégrés MOS et bipolaires suit un aperçu des circuits logiques dynamiques MOS. Ensuite sont décrits les circuits à MOST complémentaires qui sont caractérisés par une consommation dynamique de puissance proportionnelle à la fréquence. Les avantages d'une nouvelle technologie MOS, employant une couche de silicium polycristallin comme électrode de commande, sont alors passés en revue. L'utilisation de MOST complémentaires dans des circuits logiques dynamiques de même que l'emploi de transistors MOS fabriqués sur un substrat isolant afin de réduire les capacités sont discutés finalement, en tant qu'exemples d'améliorations futures de la consommation de puissance et de la fréquence limite.

## Circuiti integrati monolitici MOS

**Riassunto.** A un raffronto della tecnologia in uso attualmente per la costituzione di circuiti integrati MOS da un lato e dei circuiti integrati bipolar dall'altro, segue una sintesi dei circuiti dinamici logici MOS. Quindi vengono trattati i circuiti MOS complementari, che sono caratterizzati da un assorbimento di potenza proporzionale alla frequenza. Si spiegano indi a fondo i vantaggi della nuova tecnologia dei MOS, che utilizza quale elettrodo di comando uno strato di silicio policristallino. Quale ulteriore esempio di miglioramento del consumo di energia e del limite della frequenza vengono discussi l'utilizzazione dei circuiti complementari MOS nei circuiti dinamici logici e dei transistori MOS, che per la riduzione della capacità addizionale di connessione vengono fabbricati su substrati isolanti.

Les premières recherches systématiques sur la modulation de la conductivité par un champ électrique perpendiculaire à la surface furent publiées en 1948 par Shockley et Pearson [1]. En 1960, Kahng et Atalla [2, 3] réussirent à fabriquer le premier transistor MOS (Métal-Oxyde-Semiconducteur) utilisable. Malgré les progrès considérables réalisés depuis, il faut avouer que certains problèmes d'alors occupent toujours les technologies d'aujourd'hui: par exemple la formation indésirable d'une couche d'inversion de type N à la surface du collecteur faiblement dopé d'un transistor bipolaire PNP.

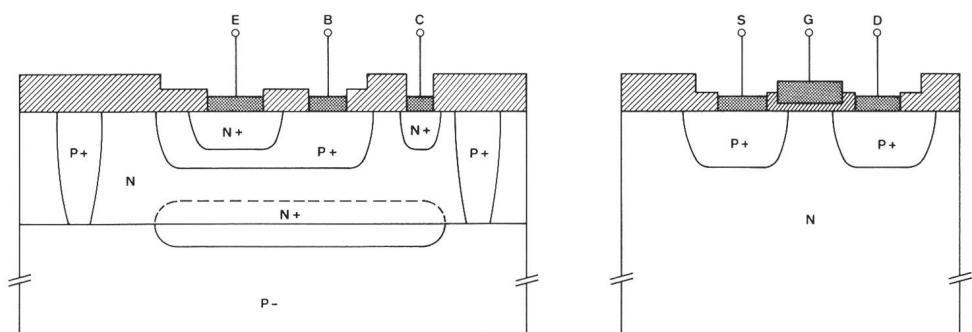

La figure 1 présente les technologies bipolaires et MOS côte à côte. Dans le procédé bipolaire et dans le cas général où une faible résistance série de collecteur est désirée, quatre pas de diffusion sont nécessaires en plus de la croissance d'une couche épitaxiale. Par contre le procédé MOS ne fait pas appel à l'épitaxie et n'a besoin que d'une seule diffusion. Le nombre de masques photolithographiques nécessaires à la réalisation d'un transistor est de six pour le bipolaire et de quatre pour le MOS. Signalons qu'il existe des technologies spéciales permettant de fabriquer des transistors bipolaires ou MOS à l'aide de trois masques

Fig. 1

Comparaison des technologies bipolaires et MOS

Nombre de masques : 6

Nombre de masques : 4

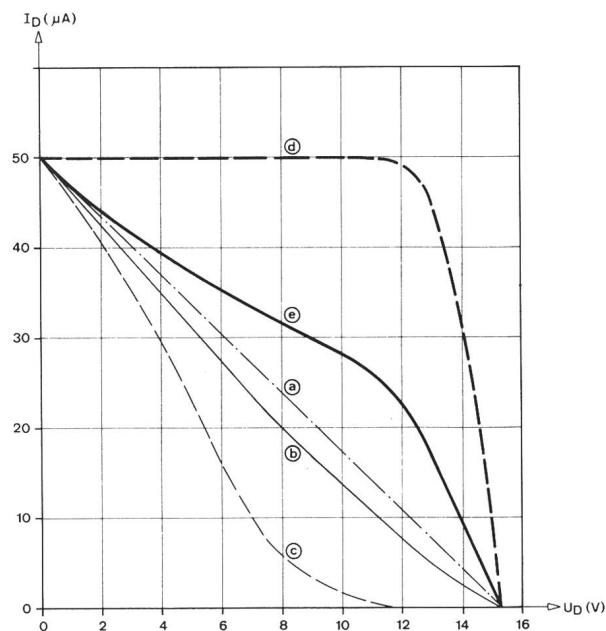

Fig. 2

Équations décrivant le comportement d'un transistor MOS sous tension continue et définition de la tension de seuil

$$\begin{aligned}

I_D &= 0 & V_G &\leq V_T \\

I_D &= \beta \left[ (V_G - V_T) V_D - \frac{V_D^2}{2} \right] & V_D &\leq V_G - V_T \\

I_D &= \frac{\beta}{2} (V_G - V_T)^2 & V_D &\geq V_G - V_T \\

g_m &= \beta (V_G - V_T) \\

\beta &= \frac{W}{L} C_o \mu

\end{aligned}$$

$\mu$  : mobilité des porteurs

$C_o$  : Capacité grille - canal par unité de surface

seulement. D'autre part il s'avère parfois nécessaire d'allonger le procédé de fabrication de base des transistors MOS afin d'éliminer certaines faiblesses. Par exemple, on procède à une passivation de l'oxyde de grille afin d'augmenter sa stabilité vis-à-vis d'un drift ionique. Le problème des couches d'inversion indésirables provoquant des canaux parasites sous l'oxyde peut être rendu négligeable par la réalisation d'oxydes très épais dans la technologie *Planox* et *Locos* ou bien par la diffusion supplémentaire d'un «Channelstopper».

Les équations décrivant le comportement d'un transistor MOS sous tension continue sont rassemblées dans la figure 2. Elles sont valables pour des tensions de grille plus élevées que la tension de seuil du transistor. Pour des tensions plus faibles, on retrouve d'une manière analogue

au transistor bipolaire une dépendance exponentielle du courant de drain en fonction de la tension de grille [4, 5].

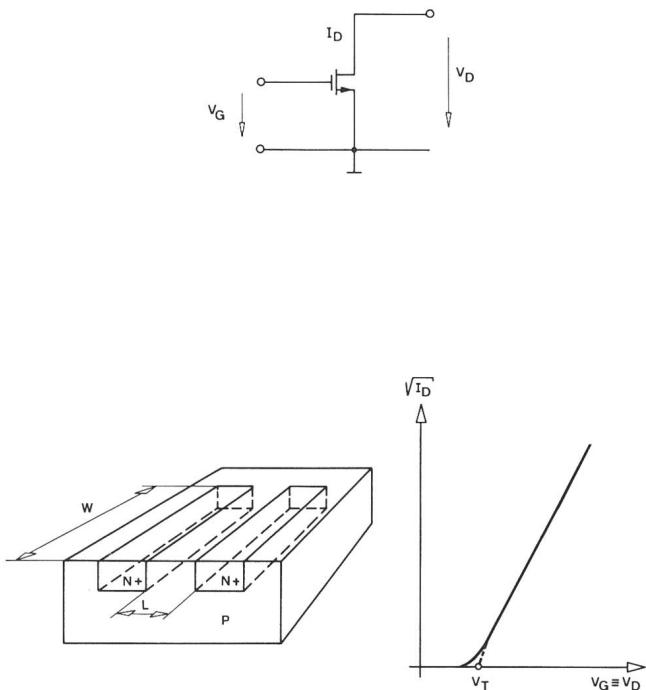

Dans les circuits intégrés comportant exclusivement des transistors MOS, ceux-ci peuvent être non seulement utilisés comme éléments actifs (interrupteurs) mais aussi comme résistances de charge. Selon leur emploi, leurs comportements qualitatifs [6] sont représentés dans la figure 3. Une résistance linéaire de  $300 \text{ k}\Omega$  a été reportée comme grandeur de référence (a). Les courbes (b) et (c) sont valables pour un MOST normalement bloqué dans le régime de la triode ( $V_D \leq V_G - V_T$ ) et dans le régime de saturation respectivement. La courbe (d) se rapporte à un MOST conduisant fabriqué sur un substrat isolé alors que la courbe (e) représente le cas de ce MOST fabriqué sur un substrat homogène. La détérioration observée vis-à-vis de (d) a pour origine le fait que le substrat agit comme seconde électrode de commande. Les principaux avantages de l'emploi d'un MOST conduisant comme résistance de charge sont les suivants: les temps de transition sont très courts car même pour de faibles tensions de sortie ( $V_D$  élevé) le courant à disposition est relativement grand. De plus le domaine de fonctionnement dépend très peu de la

Fig. 3

Courant de drain en fonction de la tension de sortie

- Résistance de  $300 \text{ k}\Omega$  comme charge

- Transistor MOS normalement bloqué  $V_D \leq (V_G - V_T)$

- Transistor MOS normalement bloqué  $V_D \geq (V_G - V_T)$

- Transistor MOS normalement conducteur fabriqué sur un substrat isolé

- Transistor MOS normalement conducteur fabriqué sur un substrat homogène

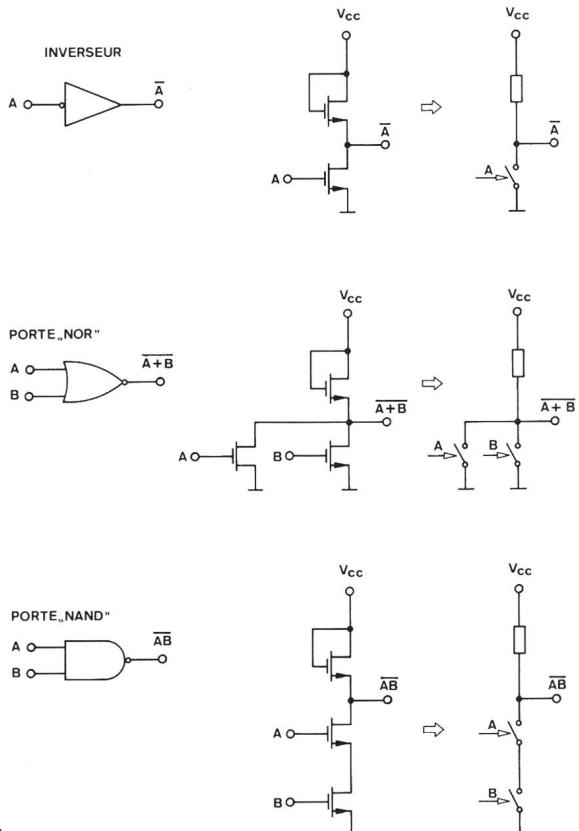

tension d'alimentation. La *figure 4* rassemble les circuits logiques de base qui sont l'inverseur, la porte «NOR» et la porte «NAND». Dans chacun des cas, un transistor MOST sert de résistance de charge. Comme ces trois portes suffisent pour effectuer toutes les opérations logiques compliquées, il s'ensuit que les circuits peuvent être réalisés uniquement avec des transistors MOS.

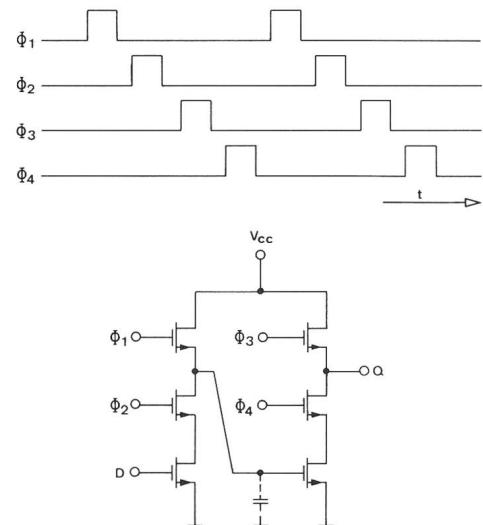

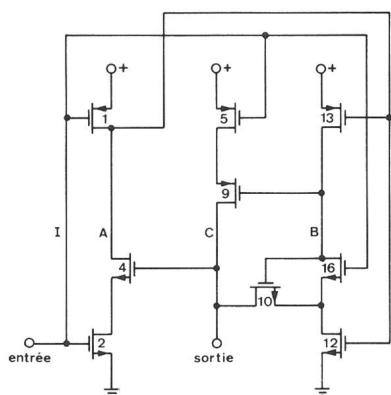

Une possibilité de réduction de la consommation de puissance est offerte par l'emploi de transistors MOS dans ce qu'on nomme les circuits logiques dynamiques. Le schéma d'un flip-flop D dynamique est représenté dans la figure 5. La fonction de chacun des transistors est celle d'un interrupteur. Ces interrupteurs se ferment et s'ouvrent à la cadence des quatre phases  $\Phi_1$  à  $\Phi_4$ . Par la fermeture de  $\Phi_1$ , la capacité d'entrée de l'étage suivant est chargée. Pendant que  $\Phi_2$  est fermé, la capacité conserve sa charge lorsque  $D = 0$  ou bien se décharge si  $D = 1$ . Après l'achèvement de ces deux phases, la valeur D sera donc emmagasinée dans cette capacité. Lorsque  $\Phi_3$  se ferme, la capacité d'entrée du prochain flip-flop se chargera. Lorsque finalement  $\Phi_4$  est fermé, cette capacité reste chargée si  $D = 0$  ou bien se décharge si  $D = 1$ . Après l'achèvement de ces quatre phases, on retrouve donc la valeur de D stockée dans

Fig. 4

## Circuits logiques de base avec leurs symboles et leurs circuits équivalents

Fig. 5 Schéma d'un flip-flop D (delay) et des quatre signaux d'horloge

la capacité d'entrée du flip-flop suivant. On constate que les seuls courants qui circulent sont ceux qui sont nécessaires à la charge des capacités. Une nouvelle simplification est représentée à la *figure 6*. La tension d'alimentation  $V_{cc}$  de la figure 5 ne sera mise à contribution que lorsque les phases  $\Phi_1$  et  $\Phi_3$  seront présentes. On pourra donc employer  $\Phi_1$ , respectivement  $\Phi_3$ , comme alimentation.

Etant donnés les courants de fuite inévitables des diodes, la durée du stockage de l'information dans les capacités de transition est limitée. Cela signifie que ce circuit dynamique ne peut fonctionner que jusqu'à une certaine limite inférieure de fréquence d'horloge. A température ambiante, cette fréquence est typiquement de l'ordre de 5 à 20 kHz. Il s'ensuit, en outre, que la réalisation d'un circuit dynamique pose de hautes exigences au degré de perfectionnement de la technologie.

A côté de l'emploi de ces circuits dynamiques réalisés à l'aide d'un seul type de transistors MOS, par exemple des MOST à canal P, la consommation de puissance peut être réduite d'un facteur très important par l'emploi de circuits à MOST complémentaires [7]. L'inverseur à MOST complémentaires est illustré à la figure 10.

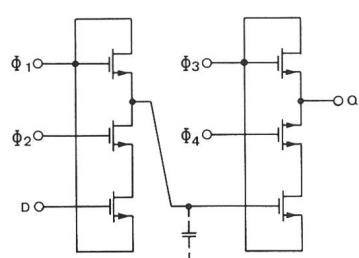

Fig. 6

Flip-flop dynamique pour lequel les phases  $\Phi_1$ , et  $\Phi_2$  respectivement sont employées comme alimentation

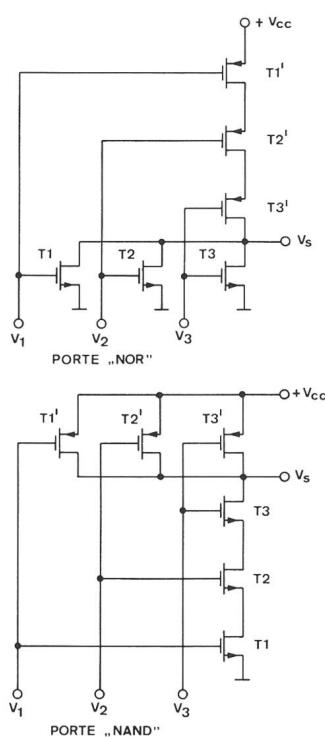

mentaires est constitué par la mise en série d'un MOST à canal P et d'un MOST à canal N. Ainsi dans les états logiques 0 et 1 aucun courant ne circule, à part les courants de fuite de quelques pA, puisque dans chaque état un des deux transistors est bloqué. Lorsque plusieurs inverseurs CMOS sont branchés les uns à la suite des autres, la sortie de l'un devra charger ou décharger la capacité d'entrée du suivant lors de chaque changement d'état. Le courant moyen est  $I = fCV_{cc}$  et la puissance est donnée par  $P = fCV_{cc}^2$  ( $f$ : fréquence d'entrée,  $C$ : capacité pondérée et  $V_{cc}$ : tension d'alimentation). La consommation de puissance dynamique est donc proportionnelle à la fréquence. Dans le cas d'une chaîne de diviseurs de fréquence, cela signifie que lorsque, par exemple, le premier étage consomme  $1 \mu\text{W}$ , une chaîne de diviseurs de longueur quelconque exige au plus  $2 \mu\text{W}$ . A cette consommation dynamique s'ajoute la consommation statique, due aux courants de fuite des diodes, qui est faible dans la plupart des cas. Dans la figure 7, nous avons reproduit le schéma des portes «NOR» et «NAND» réalisées à l'aide de MOST complémentaires. Pour la porte «NOR», lorsque les tensions d'entrée  $V_1$  à  $V_3$  sont faibles, les transistors  $T_1$  à  $T_3$  sont bloqués tandis que les transistors  $T_1'$  à  $T_3'$  conduisent, la tension de sortie est élevée. Si par exemple la tension  $V_1$  est élevée,  $T_1$  devient conducteur,  $T_1'$  bloqué et la tension de sortie est faible. En logique

Fig. 7

Portes «NOR» et «NAND» réalisées à l'aide de transistors MOS complémentaires

Fig. 8

Schéma d'un étage d'un diviseur de fréquence à transistors MOS complémentaires

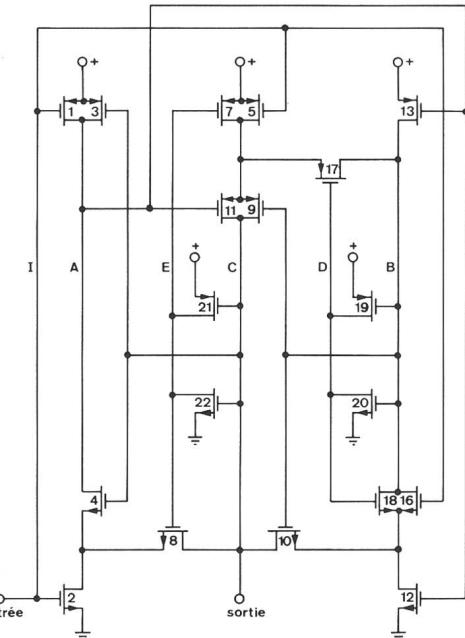

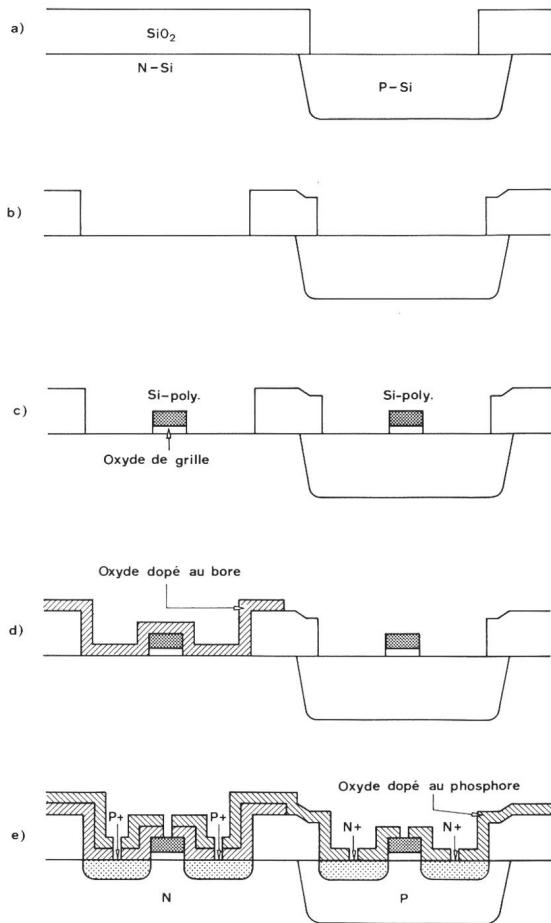

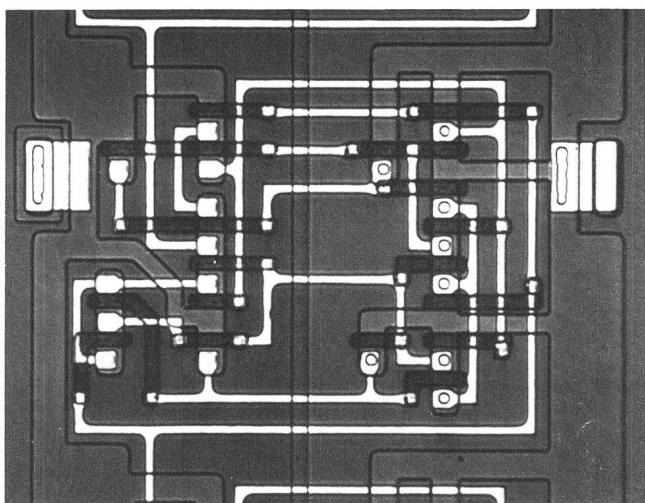

positive, le circuit travaille donc en porte «NOR». Le fonctionnement de la porte «NAND» peut s'expliquer d'une manière analogue. La figure 8 montre le schéma d'un étage diviseur de fréquence complémentaire [8] développé au Centre Electronique Horloger de Neuchâtel. Il est formé de 10 transistors à canal P et de 9 transistors à canal N. Il se caractérise par une sécurité de fonctionnement élevée, car seule une des équations du système n'est pas satisfaite pour chaque état instable possible. Par conséquent, une seule variable pourra changer d'état à la fois. De plus, seule la variable d'entrée I est nécessaire.  $\bar{I}$  est superflu et un inverseur d'entrée est donc inutile, ce qui réduit la consommation. Ce diviseur de fréquence à trois étages a été réalisé dans notre laboratoire en technologie à grille en silicium. La différence importante par rapport à la technologie classique à grille métallique est que l'électrode de grille, formée par une couche en silicium polycristallin, est déposée avant la diffusion des régions source et drain du transistor. Ainsi il est possible de réduire la diffusion latérale d'environ  $3 \mu\text{m}$  à une fraction de  $\mu\text{m}$ . Cela correspond à une réduction sensible des capacités parasites. La séquence de fabrication, représentée à la figure 9, permet la diffusion simultanée des régions  $P^+$  et  $N^+$  grâce à l'emploi d'oxydes dopés comme sources de diffusion, ce qui contribue à nouveau à la réduction des capacités parasites. La figure 10 est une microphotographie de l'étage central de ce diviseur de fréquence à trois étages. La longueur effective du canal des

Fig. 9

Etapes principales de la séquence de fabrication d'un circuit à MOST complémentaires en technologie à grille en silicium

Fig. 10

Microphotographie de l'étage central d'un diviseur à 3 étages

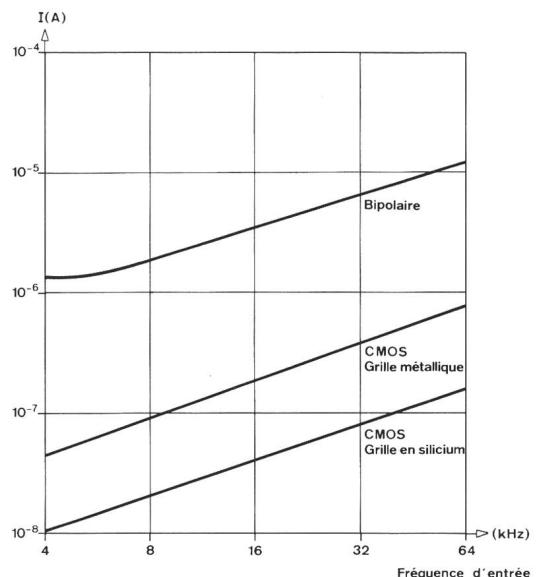

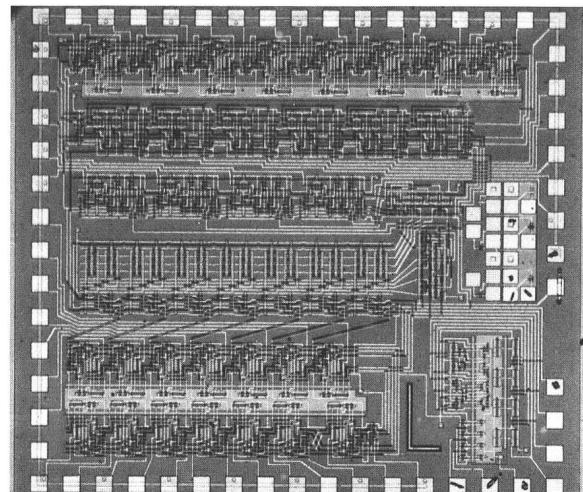

MOST est d'environ  $5 \mu\text{m}$  et la largeur des interconnexions métalliques est de  $6 \mu\text{m}$ . Un étage occupe une surface de  $0,05 \text{ mm}^2$ . A titre de comparaison, on a reporté dans la figure 11 la consommation de courant d'un diviseur de fréquence de 15 étages en fonction de la fréquence d'entrée, diviseur réalisé en version bipolaire [9], CMOS à grille métallique [10] et CMOS à grille en silicium [8]. La tension d'alimentation est de  $1,35 \text{ V}$  dans les trois cas. La figure 12 représente la microphotographie d'un circuit CMOS développé au Centre Electronique Horloger, en technologie à grille en silicium. Il s'agit d'un circuit d'interface entre une

Fig. 11

Courant consommé par des diviseurs de fréquence à 15 étages réalisés en version bipolaire, CMOS à grille métallique et CMOS à grille en silicium (tension d'alimentation:  $1,35 \text{ V}$ )

Fig. 12

Microphotographie d'un circuit CMOS en technologie à grille en silicium comprenant 1200 transistors

partie dynamique à quatre phases à MOST à canal P et d'une partie de commande de l'affichage d'une calculatrice miniature réalisée en technique TTL. Le nombre de transistors est de 1200. La consommation de puissance des circuits à MOST complémentaires peut être réduite davantage en passant, d'une manière analogue au cas des circuits non complémentaires, des circuits statiques aux circuits dynamiques.

La figure 13 montre un étage diviseur dynamique [8] déduit de l'étage statique de la figure 8. La consommation peut ainsi être réduite de 1,6 nW/kHz à environ 0,8 nW/kHz. Ce gain d'un facteur 2 correspond en gros à la réduction du nombre des transistors de 19 (circuit statique) à 10 (circuit dynamique).

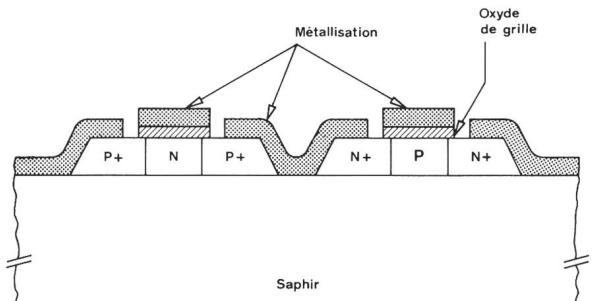

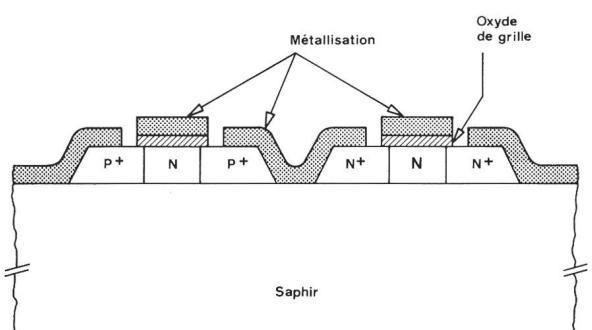

Quelles sont encore les possibilités technologiques permettant une réduction supplémentaire de la puissance consommée? Certaines dimensions critiques, telle la longueur de canal, peuvent être encore diminuées. Dans la technologie Planox ou Locos, les capacités des diodes sont réduites, en remplaçant en partie les jonctions PN par des régions d'oxyde. D'autres améliorations restent encore possibles grâce à l'emploi d'un substrat isolant [11, 12, 13]. Sur un substrat en saphir (fig. 14), on dépose une couche

Fig. 13

Etage d'un diviseur CMOS dynamique, déduit de l'étage statique de la figure 8

épitaxiale d'environ 1  $\mu\text{m}$  d'épaisseur de silicium d'orientation (100). Des petites îles de silicium de la dimension d'un MOST sont gravées dans un premier pas photolithographique. Comme en technologie CMOS, le substrat complémentaire doit être fabriqué soit par diffusion, soit par implantation ionique. Les deux types de régions source et drain peuvent, par exemple, être diffusés simultanément grâce à l'emploi d'oxydes dopés. Des circuits à grille métallique sont aussi réalisables sur un substrat isolé, mais une technologie optimalisée fera bien entendu appel au procédé à grille en silicium. Selon la grandeur des éléments, la capacité drain-substrat peut ainsi être réduite

a)

b)

Fig. 14

Structures CMOS fabriquées sur un substrat isolant (saphir)

d'un à deux ordres de grandeur. La densité des courants de fuite est cependant deux à trois ordres de grandeur plus élevée qu'avec un substrat homogène. La variante représentée dans la figure 14b ne fait appel qu'à un substrat d'un seul type. Le MOST à canal P travaille dans le mode d'enrichissement usuel. Par contre, le MOST à canal N est plutôt employé comme transistor à film mince. Si la couche de silicium est assez mince et son dopage suffisamment faible, le potentiel de contact entre l'électrode de champ et le silicium suffit à former une zone d'appauvrissement qui s'étend jusqu'au substrat isolé. Le courant restant, limité par la charge d'espace, peut être rendu négligeable sous des conditions favorables. Une tension de grille positive rend le transistor conducteur par la formation d'une couche d'accumulation d'électrons.

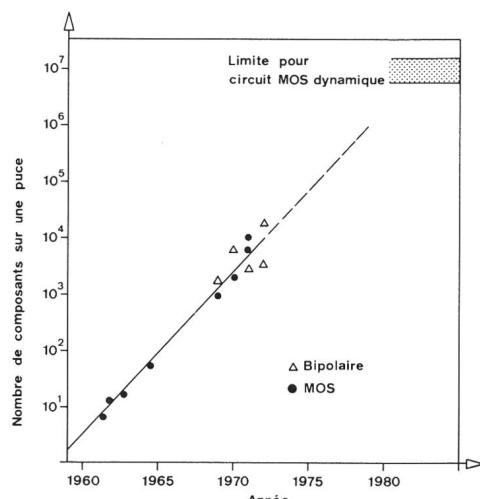

Avec les méthodes photolithographiques usuelles, il est fondamentalement possible d'intégrer des MOST avec des dimensions minimales de  $6 \times 14 \mu\text{m}$ . Dans une publication récente [14], un MOST a été proposé, dont la plus grande dimension est de  $1,2 \mu\text{m}$ . Bien qu'il soit possible de former des structures possédant ces dimensions à l'aide de sys-

tèmes à faisceaux électroniques, une réalisation pratique se heurte encore à d'énormes difficultés. La *figure 15* montre l'évolution du nombre des composants par puce au cours du temps [14]. En employant les structures minimales mentionnées ci-dessus, il serait possible d'atteindre le nombre effarant de 10 millions de composants par puce! Une structure MOS typique étant définie par environ 25 points de coordonnées, le système à faisceaux électroniques devrait reproduire séquentiellement 250 millions de points de coordonnées par circuit. La question fondamentale qui se pose alors est de savoir comment réaliser la liaison entre une puce comprenant 10 millions de composants et le monde extérieur.

Fig. 15

Evolution du nombre des composants par puce au cours du temps

## Bibliographie

- [1] Shockley W., Pearson G. L. Modulation of conductance of thin films of semiconductors by surface charges. *Physical Review*, 74 (1948) July, p. 232...233.

- [2] US Patent No 3102230, Electrical Field Controlled Semiconductor Devices, filed May 31, 1960 and issued on August 27, 1963 to *D. Kahng*.

- [3] US Patent No 3056888, Semiconductor Triode, filed August 17, 1960 and issued on October 2, 1962 to *M. M. Atalla*.

- [4] Barron M. B. Low Level Currents in Insulated Gate Field Effect Transistors. *Solid State Electronics*, 15 (1972) March, p. 293...302.

- [5] Swanson R. M., Meindl J. D. Ion Implanted Complementary MOS Transistors in Low-Voltage Circuits. *IEEE Journal of Solid-State Circuits* SC-7, (1972) April, p. 146...153.

- [6] Crawford R. Implanted depletion loads boost MOS array performance. *Electronics*, (1972) April 24, p. 85...90.

- [7] Wanlass F. M., Sah C. T. Nanowatt logic using field effect metal oxide semiconductor triodes. *ISSCC Digest*, (1963), p. 32...33.

- [8] Vitzoz E., Gerber B., Leuenberger F. Silicon Gate CMOS Frequency Divider for the Electronic Wrist Watch. *IEEE Journal of Solid-State Circuits* SC-7, (1972) April, p. 100...104.

- [9] Ruegg H., Thommen W. Bipolar Micropower Circuits for Crystal Controlled Timepieces. *IEEE Journal of Solid State Circuits* SC-7, (1972) April, p. 105...111.

- [10] Leuenberger F., Vitzoz E. Complementary-MOS Low-Power Low-Voltage Integrated Binary Counter. *Proceedings of the IEEE*, 57 (1969) September, p. 1528...1532.

- [11] Hofstein S. R. An Analysis of Deep Depletion Thin-Film MOS Transistors. *IEEE Transactions on Electron Devices* ED-13, (1966) December, p. 846...855.

- [12] Heiman F. P. Thin Films Silicon-on-Sapphire Deep Depletion MOS Transistors. *IEEE Transactions on Electron Devices* ED-13, (1966) December, p. 855...862.

- [13] Boleky E. J., Meyer J. E. High Performance CMOS Memories Using Silicon-on-Sapphire Technology. *IEEE Journal of Solid-State Circuits* SC-7, (1972) April, p. 135...145.

- [14] Hoeneisen B., Mead C. A. Fundamental Limitations in Microelectronics – I. MOS Technology. *Solid State Electronics*, 15 (1972) July, p. 819...829.

- Adresse de l'auteur: Fritz Leuenberger, Centre électronique horloger SA, CH-2000 Neuchâtel