**Zeitschrift:** Technische Mitteilungen / Schweizerische Post-, Telefon- und

Telegrafenbetriebe = Bulletin technique / Entreprise des postes, téléphones et télégraphes suisses = Bollettino tecnico / Azienda delle

poste, dei telefoni e dei telegrafi svizzeri

Herausgeber: Schweizerische Post-, Telefon- und Telegrafenbetriebe

**Band:** 48 (1970)

Heft: 3

Artikel: Expandierender Digital-Analog-Wandler mit einem Leiternetzwerk für

die PCM-Technik

Autor: Merz, Pierre-André

**DOI:** https://doi.org/10.5169/seals-876045

# Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. Mehr erfahren

## **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. En savoir plus

### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. Find out more

**Download PDF:** 18.11.2025

ETH-Bibliothek Zürich, E-Periodica, https://www.e-periodica.ch

# Expandierender Digital-Analog-Wandler mit einem Leiternetzwerk für die PCM-Technik

Pierre-André MERZ, Zürich

621.376.56

Zusammenfassung. In der PCM-Übertragungstechnik verwandelt man auf der Empfangsseite das Codesignal in das ursprüngliche Analogsignal zurück. Über Aufbau und Eigenschaften von Digital-Analog-Wandlern zur Decodierung binärer Codesignale wird berichtet. Es folgt eine Untersuchung über die Expandierung eines komprimierten Codesignals. Ein praktisch aufgebauter Digital-Analog-Wandler mit Dynamikexpansion zur Decodierung von 30 Sprachkanälen wird beschrieben.

#### Convertisseur expanseur analogique digital à structure scalaire pour la technique MIC

Résumé. Dans la technique de transmission MIC, le signal de code est converti côté réception en signal analogique reproduisant le signal original. L'article montre la structure et les caractéristiques de convertisseurs analogiques digitaux pour le décodage de signaux de code binaires. Suit une étude sur l'expansion d'un signal de code comprimé. On décrit pour finir la construction d'un convertisseur analogique digital avec expansion dynamique pour le décodage de 30 canaux vocaux.

# Convertitore numerico-analogico espansore a struttura scalare per la tecnica PCM

Riassunto. Nella tecnica di trasmissione PCM si riconverte, dal lato della ricezione, il segnale codificato nel segnale analogico-originale. L'articolo illustra la struttura e la qualità del convertitore numerico analogico per la decodificazione dei segnali binari codificati. Segue uno studio sull'espansione del segnale codificato compresso. Inoltre si descrive la realizzazione pratica di un convertitore numerico-analogico con espansione di dinamica per la decodificazione di 30 canali vocali.

### 1. Einleitung

Für die Mehrfachausnützung von bestehenden NF-Leitungen beginnt sich die Pulscodemodulation (PCM) durchzusetzen. Auf der Sendeseite werden n Kanäle (zum Beispiel n = 30) in einem Analog-Digital-Wandler im Zeitmultiplexverfahren codiert. Das codierte Signal wird über ein entpupinisiertes NF-Aderpaar übertragen, nach gewissen Leitungslängen regeneriert und auf der Empfangsseite in einem Digital-Analog-Wandler wieder in Analogsignale zurückverwandelt. In klassischen Digital-Analog-Wandlern werden die zeitlich aufeinanderfolgenden Impulse eines ankommenden Codesignals an RC-Gliedern direkt zu einem Analogsignal verarbeitet. Man spricht in diesem Falle von Direkt-Codierern. Bekannte Direkt-Codierer sind der Shannon-Decoder und der Shannon-Rack-Decoder.

Bei modernen Digital-Analog-Wandlern gelangt das ankommende Codesignal zuerst auf eine Speicherschaltung; das heisst, die Seriecodegruppe wird in eine Parallelcodegruppe umgewandelt. Die Speicherschaltung steuert einen Gewichtssatz, der gewichtete Ströme abgibt. In einem Summenverstärker (gegengekoppelter Operationsverstärker) werden die gewichteten Ströme summiert und in eine analoge Spannung verwandelt. Diese Methode hat gegenüber der «direkten Decodiermethode» den Vorteil, dass

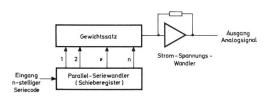

Prinzip eines Digital-Analog-Wandlers

Fig. 2

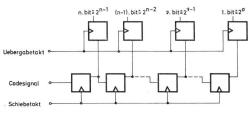

Serie-Parallelwandler (Schieberegister) mit Speicherschaltung

komprimierte Codesignale mit einem stückweise linearen Kompandergesetz mit einfachen digitalen Mitteln wieder expandiert werden können.

In diesem Bericht soll das Problem der Digital-Analog-Umwandlung mit Speicherschaltung und Gewichtssatz näher untersucht werden, insbesondere zur Decodierung von komprimierten PCM-Signalen in bipolare Analogsignale.

#### 2. Lineare Digital-Analog-Wandler

2.1 Decodierung eines binären Codesignals in ein unipolares Analogsignal [1]

Digital-Analog-Wandler bestehen, wie dies in Figur 1 dargestellt ist, im wesentlichen aus drei Teilen:

- Einem Serie-Parallelwandler (Schieberegister) mit Speicherschaltung, der die empfangene Seriecodegruppe in eine Parallelcodegruppe umwandelt.

- Einem digital gesteuerten Gewichtssatz, der gewichtete Ströme abgibt und

- einem Stromspannungswandler (gegengekoppelter Operationsverstärker), der die gewichteten Ströme summiert und in eine analoge Spannung umwandelt.

Ein Serie-Parallel-Wandler mit Speicherschaltung ist in Figur 2 dargestellt. Das ankommende n-stellige Codesignal

wird mit dem Schiebetakt (Impulsfolge mit der gleichen Folgefrequenz wie das Codesignal) in das Schieberegister eingeschrieben. Danach übergibt der Übergabetakt das Codewort vom Schieberegister in eine Speicherschaltung, die aus n Speicherelementen besteht. Jedem bit ist ein Speicherelement (Flip-Flop) zugeordnet. Das Codewort liegt nun in «Parallelform» vor und kann zur eigentlichen Decodierung benützt werden. Die erste bit-Stelle entspricht der kleinsten Wertigkeit 2° (least significant bit); jedes nachfolgende bit hat eine um den Faktor 2 grössere Wertigkeit; das n. bit entspricht der grössten Wertigkeit 2<sup>n-1</sup> (most significant bit).

Der Decodiervorgang muss zeitlich bis zum Eintreffen des nächsten Übergabetaktes abgeschlossen sein, weil dann ein neues Codewort vom Schieberegister an die Speicherschaltung übergeben wird. Die Pulsdiagramme zum Serie-Parallel-Wandler sind aus *Figur 3* ersichtlich.

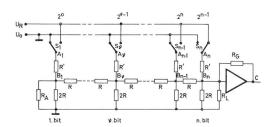

Als Gewichtssatz sind folgende zwei Schaltungsanordnungen von Bedeutung:

- Ein Netzwerk, bei dem mit Hilfe von gewichteten Widerständen entsprechende Ströme erzeugt und einem Summenverstärker zugeführt werden.

- Ein «Leiternetzwerk», dem Ströme verschiedenen Knotenpunkten zugeführt werden, die zum Ausgang ein gewichtetes Verhältnis haben.

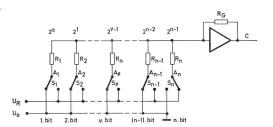

Ein gewichtetes Widerstandsnetzwerk ist in *Figur 4* dargestellt. Es besteht aus n Gewichtswiderständen,  $R_1$ ,  $R_2$ ... $R_n$ , n Gewichtsschaltern,  $S_1$ ,  $S_2$ ... $S_n$  und einer Referenzspannungsquelle  $U_R$ . Jeder Widerstandswert R bildet ein binäres Gewicht  $2^{\nu-1}$ , dem das  $\nu$ te bit des Codewortes zugeordent ist. Ist der Zustand des  $\nu$ . bit eine logische 1, so ist der Widerstand  $R_{\nu}$  an die Referenzspannungsquelle  $U_R$  geschaltet; das Gewicht  $2^{\nu-1}$  ist eingeschaltet. Ist der Zustand des  $\nu$ . bit eine logische 0, so ist der Widerstand  $R_{\nu}$  an die Bezugsspannungsquelle (Masse) geschaltet; das Gewicht  $2^{\nu-1}$  ist ausgeschaltet. Die Gewichtsströme werden im Summenverstärker addiert und in eine analoge Spannung

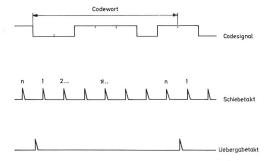

Fig. 3

Pulsdiagramm zum Serie-Parallel-Wandler

Fig. 4

Gewichtssatz mit gewichtetem Widerstandsnetzwerk zur Decodierung eines binären Codesignals in ein unipolares Analogsignal

umgewandelt. Die Widerstände aller ausgeschalteten Gewichte werden an die Bezugsspannungsquelle (Masse) geschaltet, so dass am Eingang des Summenverstärkers immer die gleiche Quellenimpedanz erscheint.

Ein Gewichtssatz mit einem «Leiternetzwerk» (Laddernetwork) ist in Figur 5 dargestellt. Die Decodierung geschieht in einem Widerstandsnetzwerk mit den Widerständen 2 R, R, dem Abschlusswiderstand RA und dem Lastwiderstand R<sub>L</sub>. Schaltbare identische Konstantstromquellen, bestehend aus der Referenzspannung UR den Widerständen R' und den Schaltern S speisen je einen Knotenpunkt B des Widerstandsnetzwerkes. Jeder schaltbaren Stromquelle ist ein bit des Codewortes zugeordnet. Ist der Zustand des  $\nu$ . bit eine logische 1, so ist der entsprechende Widerstand R' mit dem Schalter S, an die geregelte Referenzspannungsquelle UR geschaltet; es fliesst ein konstanter Strom in den Knotenpunkt B,. Ist der Zustand des  $\nu$ . bit eine logische 0, so ist der entsprechende Widerstand R' mit dem Schalter S, an die Bezugsspannungsquelle (Masse) geschaltet; es fliesst kein Strom in den Knotenpunkt B, Jeder identische Strom, der ins Leiternetzwerk fliesst, hat ein gewichtetes Verhältnis zum Ausgangsknoten B<sub>n</sub>. Der Strom im ersten Knoten B<sub>1</sub> hat den geringsten Einfluss auf das decordierte Analogsignal (least significant bit); der Einfluss jedes aufeinanderfolgenden Knotenstromes wird um den Faktor 2 vergrössert (binärer Code); der letzte Knotenstrom im Knoten Bn hat den grössten Einfluss auf das decodierte Analogsignal (most significant bit). Eine Schaltung dieser Art ist in [2] beschrieben; sie wurde von Bell in ihrer 224 Mb/s PCM-Endschaltung [3]

## 2.2 Decodierung eines binären Codesignals in ein bipolares Analogsignal

Die im Abschnitt 2.1 beschriebenen Gewichtssätze liefern unipolare Analogsignale, das heisst das decodierte Analogsignal liegt zwischen der Bezugsspannung  $U_{\rm o}$  und einer maximalen Spannung  $U_{\rm max}$ , da die Gewichtsströme nur in einer Richtung fliessen.

Gewichtssatz mit Leiternetzwerk zur Decodierung eines binären Codesignals in ein unipolares Analogsignal

Oft ist es wünschenswert, ein Codesignal direkt in ein bipolares Analogsignal umzuwandeln; dies ist besonders bei einem sogenannten gefalteten Code ein grosser Vorteil. Gefaltete Code haben für beide Polaritäten eines Analogsignals ein identisches Codewort, dem ein zusätzliches Vorzeichen-bit beigefügt ist. Der Gewichtssatz eines bipolaren Digital-Analog-Wandlers kann dann für beide Polaritäten des Analogsignals identisch angesteuert werden. Das Vorzeichen-bit entscheidet, ob positive oder negative Gewichtsströme fliessen sollen.

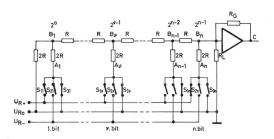

Ein Gewichtssatz mit einem Leiternetzwerk, das digitale Codesignale in positive und negative Analogsignale umwandelt, ist in *Figur 6* dargestellt.

An jedem Fusspunkt A des n-stelligen Leiternetzwerkes befinden sich drei elektronische Schalter  $S_1$ ,  $S_2$  und  $S_3$ .  $S_1$  verbindet den Fusspunkt A mit der positiven Referenzspannung  $U_{R+}$ ,  $S_2$  den Fusspunkt A mit der negativen Referenzspannung  $U_{R-}$ , und  $S_3$  den Fusspunkt A mit der Bezugsspannung  $U_{R0}$ .

Ein (n+1)-stelliger binärer Code, beispielsweise ein gefalteter Code, soll in ein bipolares Analogsignal umgewandelt werden. Ein bit ist das sogenannte Vorzeichen-bit. Ist der Zustand des Vorzeichen-bits eine logische 1, so ist das decodierte Analogsignal positiv; ist der Zustand des Vorzeichen-bit eine logische 0, so ist das decodierte Analogsignal negativ.

Von den übrigen n bit ist jedem Fusspunkt  $A_{\nu}$  das  $\nu$ .bit zugeordnet.

Ist der Zustand des  $\nu$ .bit eine logische 1, so wird der Fusspunkt  $A_{\nu}$  entweder mit dem Schalter  $S_{1\nu}$  an die positive Referenzspannung  $U_{R+}$  oder mit dem Schalter  $S_{2\nu}$  an die negative Referenzspannung geschaltet.

Ist der Zustand des  $\nu$ .bit eine logische 0, so schaltet der Schalter  $S_{3\nu}$  den Fusspunkt  $A_{\nu}$  an die Bezugsspannung  $U_{Ro}$  (Masse). Die Spannung  $U_{Ro}$  liegt dabei in der Mitte zwischen  $U_{R+}$  und  $U_{R-}$ . Jeder Fusspunkt  $A_{\nu}$ , der an die positive oder negative Referenzspannung geschaltet ist, liefert an den Ausgangsknoten  $B_n$  des Leiternetzwerks einen Teilstrom, der ein gewichtetes Verhältnis zum Fusspunkt  $A_{\nu}$

hat. Die Spannung am ersten Fusspunkt  $A_1$  liefert den geringsten Teilstrom an den Ausgangsknoten  $B_n$  (least significant bit). Die Spannung an jedem weiteren Fusspunkt  $A_2$ ,  $A_3$ ... $A_n$  liefert einen je um den Faktor 2 erhöhten Teilstrom an den Ausgangsknoten. Die Spannung am letzten Fusspunkt  $A_n$  liefert den grössten Teilstrom an den Ausgangsknoten (most significant bit).

Im darauffolgenden Stromspannungswandler (Operationsverstärker) werden die gewichteten Teilströme summiert und in eine Analogspannung umgewandelt.

## 3. Expandierende Digital-Analog-Wandler

#### 3.1 Das 13-Segmente-Kompandergesetz

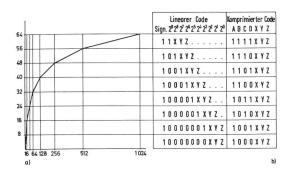

Zur Verbesserung des Signalgeräuschabstandes in PCM-Anlagen wird das zu übertragende Signal kompandiert (komprimiert auf der Coderseite, expandiert auf der Decoderseite). Die Kompression im Coder lässt sich besonders gut in Form einer stückweisen linearen Kompressionscharakteristik verwirklichen.

Das Prinzip der stückweisen linearen Kompressionscharakteristik ist in [4] ausführlich beschrieben. Es geht darum, die zu übertragende Stellenzahl eines n-stelligen Codes zu verringern, wobei ein gewisser Fehler in Kauf genommen wird.

Will man beispielsweise nur eine m-stellige Genauigkeit eines n-stelligen Codes, dann leitet man aus dem ursprünglichen Code zwei Codegruppen ab; die erste enthält die m Stellen (Feinstruktur), die zweite legt mit x Stellen die Lage (Segmentinformation) der m Stellen im n-stelligen Code fest. Von den m Stellen braucht die erste Stelle nicht übertragen zu werden, weil sie vom logischen Zustand der x Stellen der zweiten Codegruppe eindeutig bestimmt ist.

Das 13-Segmente Kompandergesetz [5] ist in Figur 7 dargestellt. Einem n=10stelligen Binärcode ist eine 11. Stelle als Vorzeichen-bit beigefügt. Der n=10stellige Binärcode wird mit einer m= vierstelligen Genauigkeit übertragen. Zur Bestimmung der genauen Lage (Segmentinformation) der m=4 Stellen (., X, Y, Z) benötigt man zu-

Fig. 6

Gewichtssatz mit Leiternetzwerk zur Decodierung eines binären

Codesignals in ein bipolares Analogsignal

Fig. 7 13-Segment-Kompandergesetz (nur positive Vorzeichen)

sätzlich x=3 Stellen (B, C, D). Die drei Stellen B, C, D bestimmen auch eindeutig den logischen Zustand der ersten Stelle der m=4 Stellen; sie wird deshalb nicht übertragen.

Die erste m-Stelle ist 0, falls alle drei Stellen B, C, D eine logische 0 haben; sie ist 1, falls irgend eine oder mehrere der drei x-Stellen eine logische 1 hat.

Zusammen mit dem Vorzeichen-bit A wird demnach ein 7stelliges Codewort A, B, C, D, X, Y, Z übertragen, um ein 11stelliges Codewort (2048 Amplitudenstufen) mit einer 4stelligen Genauigkeit zu übertragen. Das 13-Segmente Kompandergesetz ist für eine Polarität (positives Vorzeichen) in Figur 7 dargestellt, sie zeigt graphisch den stückweise linearen Streckenzug und die «Wahrheitstabelle».

# 3.2 Decodierung eines nach dem 13-Segmente-Kompandergesetz komprimierten Codes

Ein komprimierter Code muss auf der Decoderseite vor dem Decodieren expandiert werden, um wiederum das ursprüngliche Analogsignal zu erhalten.

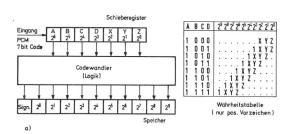

Der mit einer stückweise linearen Kompressionscharakteristik komprimierte Code kann mit einer Schaltungsanordnung gemäss Figur 8 expandiert werden.

Ein ankommendes 7stelliges Codesignal wird in ein Schieberegister eingeschrieben. Parallel zum Schieberegister liegt der Codewandler. Je nach dem logischen Zustand der Ziffern B, C, D erscheinen die Ziffern X, Y, Z an drei bestimmten, nebeneinanderliegenden Ausgängen. Wenn mindestens eine der Ziffern B, C, D eine logische 1 aufweist, so hat die erste Stelle der m = 4 Stellen eine logische 1. Dieser Wert wurde nicht übertragen; er wird im Codewandler gebildet und erscheint am Ausgang neben der Ziffer X. Die Zusammenhänge zwischen Eingangsgrössen und Ausgangsgrössen des Codewandlers sind in der Wahrheitstabelle dargestellt. Der Vergleich der beiden Wahrheitstabellen von Figur 7 und Figur 8 zeigt, dass das

auf der Coderseite digital komprimierte Codesignal auf der Decoderseite im Codewandler wieder digital expandiert wird. Die Ausgangssignale des Codewandlers gelangen auf eine Speicherschaltung, wo auch das Vorzeichen-bit A mitberücksichtigt wird. Die gespeicherten Signale dienen zur Ansteuerung eines 10stelligen Gewichtssatzes, wie er in Abschnitt 2.2 beschrieben ist.

## 4. Praktisch ausgeführter expandierender Digital-Analog-Wandler mit einem Leiternetzwerk

Zur Decodierung von 30 im PCM-Zeitmultiplex codierten Sprachkanälen wurde ein Digital-Analog-Wandler entwickelt. Vom 8stelligen Codewort eines jeden ankommenden Zeitkanals wird die letzte bit-Stelle für die Übertragung des Synchronwortes und der Kennzeichen verwendet.

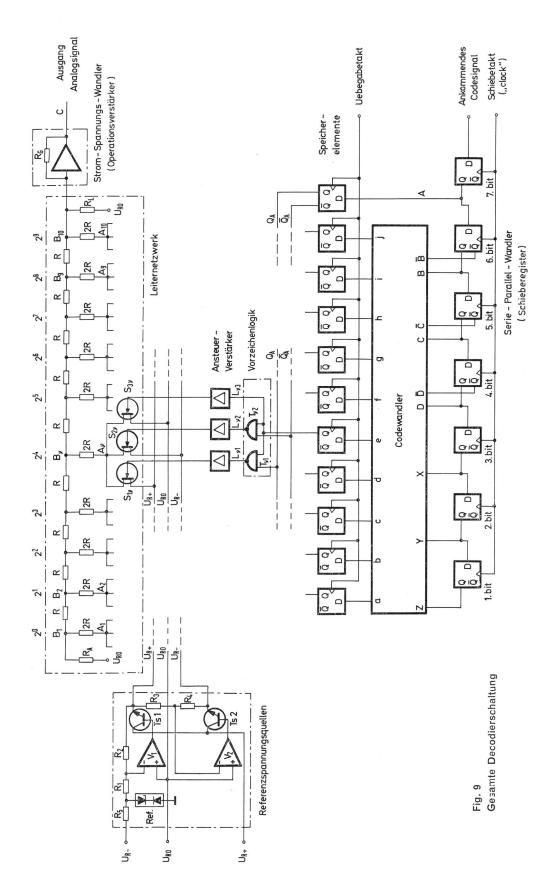

In Figur 9 ist die gesamte Decodiereinrichtung dargestellt. Sie besteht aus einem Serie-Parallel-Wandler (Schieberegister), einem Codewandler zur Expandierung nach dem 13-Segmente-Kompandergesetz, 11 Speicherelementen für das expandierte Codewort, einem Leiternetzwerk samt Vorzeichenlogik und Ansteuerungen für die Gewichtsschalter, einem Stromspannungswandler (Operationsverstärker) und je einer positiven und negativen Referenzspannungsquelle.

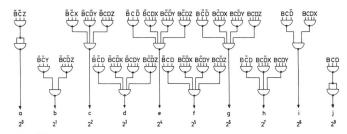

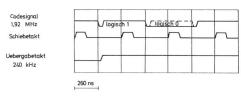

Die sieben Sprach-bit des 8stelligen Codesignals werden mit dem Schiebetakt (Impulsfolgefrequenz 1,92 MHz) in den Serie-Parallel-Wandler (Schieberegister) eingeschrieben. Parallel zum Schieberegister liegt der Codewandler, wie er im Abschnitt 3.2 beschrieben wurde. Die gesamte Schaltung ist ausschliesslich mit integrierten TTL-Bausteinen aufgebaut. Das Detailschema ist in Figur 10 dargestellt. Die Ausgänge des Codewandlers führen gemäss Figur 9 auf Speicherelemente (D-Flip-Flop), in welchen die Ansteuersignale für die zehn Knotenpunkte des Leiternetzwerkes mit einem gemeinsamen Übergabetakt (Pulsfolgefrequenz 240 kHz) übergeben und dort zur eigentlichen Decodierung gespeichert werden. Das siebente bit des ankommenden Codesignals wird vom Schieberegister mit dem Übergabetakt direkt an ein Speicherelement übergeben. Das gespeicherte siebente bit (QA, QA) dient zur Steuerung der Vorzeichen-

Fig. 8

Digitale Expandierung

Fig. 10

Detailschema des Codewandlers gemäss Figur 9

logik. Die Oszillogramme von Codesignal, Schiebetakt und Übergabetakt sind in *Figur 11* dargestellt.

Die gespeicherten Ansteuersignale steuern gemäss Figur 9 die Gewichte eines Gewichtssatzes mit Leiternetzwerk, wie im Abschnitt 2.2 beschrieben.

In der praktischen Ausführung sind die drei elektronischen bipolaren Schalter  $S_1$ ,  $S_2$ ,  $S_3$  an jedem Fusspunkt A des Leiternetzwerkes Feld-Effekt-Transistoren (FET). Ist der Zustand des gespeicherten  $\nu$ . Ansteuersignals eine logische 1, so wird bei einem Vorzeichen-bit  $Q_A=1$  der Fusspunkt  $A_{\nu}$  mit dem FET-Schalter  $S_{1\nu}$  an die positive Referenzspannung  $U_{R+}$  geschaltet, bei einem Vorzeichen-bit  $Q_A=0$  mit dem FET-Schalter  $S_{2\nu}$  an die negative Referenzspannung  $U_{R-}$ . Ist der Zustand des gespeicherten  $\nu$ . Ansteuersignals eine logische 0, so wird der Fusspunkt  $A_{\nu}$  mit dem FET-Schalter  $S_{3\nu}$  an die Bezugsspannung  $U_{Ro}$  geschaltet, unabhängig vom logischen Zustand des Vorzeichen-bit.

Die Widerstände des Leiternetzwerkes müssen so gewählt werden, dass die Querwiderstände 2 R' zusammen mit den Eigenwiderständen R<sub>FET</sub> der FET-Schalter den doppelten Widerstandswert der Längswiderstände R haben. Die Durchlasswiderstände von Feldeffekt-Transistoren variieren stark mit der Temperatur und haben verhältnismässig grosse Exemplarstreuungen. Man wählt deshalb ein hochohmiges Leiternetzwerk, um den störenden Einfluss der Schalterwiderstände in zulässigen engen Grenzen zu halten.

Mit dem praktisch aufgebauten Leiternetzwerk erreichte man eine Decodiergenauigkeit gemäss *Tabelle I.* Diese Messwerte gelten über einen Temperaturbereich von + 5 °C...+ 70 °C. Die Segmentzahl bezieht sich dabei auf den positiven Bereich des 13-Segmente-Kompandergesetzes (Fig. 7), die Resultate gelten aber für beide Polaritäten.

Tabelle 1: Decodiergenauigkeit des Leiternetzwerkes mit den FET-Schaltern.

| Segment | Stufe  | Decodier-Genauigkeit |

|---------|--------|----------------------|

| 1       | 1      | ± 1%                 |

| 1       | 215    | $\pm$ 0,5 $\%$       |

| 2       | 1631   | $\pm$ 0,3 $\%$       |

| 37      | 321960 | + 0,2 $%$            |

Gegenüber dem theoretischen Quantisierungsfehler auf der Coderseite kann ein Decodierfehler von etwa 0,3% vernachlässigt werden.

Am Ausgang des Leiternetzwerkes erscheint das decodierte Signal als pulsamplitudenmodulierter Analogstrom. Im anschliessenden Stromspannungswandler wird dieser

Im anschliessenden Stromspannungswandler wird dieser Strom in eine Analogspannung umgewandelt. Die Analogspannung gelangt zu den 30 empfangsseitigen Kanalabtastschaltern.

In einer weiteren Einheit (gemäss Figur 9) werden die beiden Referenzspannungsquellen  $U_{\rm R+}$  und  $U_{\rm R-}$  erzeugt. Die Absolutbeträge der positiven Referenzspannung  $U_{\rm R+}$  und der negativen Referenzspannung  $U_{\rm R-}$  bezüglich der Bezugsspannung  $U_{\rm Ro}$  müssen über den ganzen Stromund Temperaturbereich gleich gross sein. Abweichungen bewirken nichtlineare Verzerrungen im decodierten bipolaren Analogsignal.

Ein erster Regler, bestehend aus einem Operationsverstärker V1 und einem Transistor Ts1, ist mit der Widerstandskombination R1, R2 an den invertierenden Eingang des Operationsverstärkers gegengekoppelt. Zur Erzeugung der positiven Referenzspannung  $U_{R+}$  ist an den beiden Eingängen des Operationsverstärkers eine temperaturkompensierte «absolute» Referenzspannung (Temperaturkompensiertes Referenzelement) angelegt. Ein zweiter Regler, bestehend aus V2 und Ts 2, ist mit R3, R4 an den invertierenden Eingang des Operationsverstärkers V2 gegengekoppelt. Dieser erzeugt die negative Referenzspannung U<sub>R-</sub>, indem an den Eingängen des Operationsverstärkers die positive Referenzspannung U<sub>R+</sub> mit der Bezugsspannung U<sub>Ro</sub> verglichen wird. Wählt man das Widerstandsverhältnis R<sub>3</sub>:R<sub>4</sub> = 1:1, so ist die negative Referenzspannung U<sub>R</sub>\_ bezüglich der Bezugsspannung U<sub>R</sub>o dem Betrage nach gleich gross wie U<sub>R+</sub>.

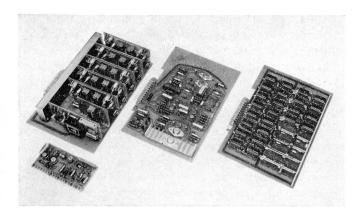

Figur 12 zeigt die Baugruppen des Digital-Analog-Wandlers. Auf der rechts dargestellten Baugruppe befinden sich das Schieberegister und der Codewandler, der das komprimierte 7stellige Codewort in einen 11stelligen Code expandiert. Die Logik besteht aus TTL-Bausteinen. Die Baugruppe in der Mitte zeigt die positive und negative Referenzspannungsquelle für die Gewichte sowie drei Längsregler zur Erzeugung von drei weiteren im Decoder benötigten Span-

Fig. 11

Impulsdiagramme zum Digital-Analog-Wandler

Fig. 12 Baugruppen des Digital-Analog-Wandlers

nungen. Auf der dritten Baugruppe, links, befinden sich folgende Schaltungskomponenten: das 10stellige Leiternetzwerk, der Stromspannungswandler mit einem diskreten Operationsverstärker, eine Speicherschaltung für das Vorzeichen-bit, zehn Gewichtsschalter samt Schalteransteuerung, die Vorzeichenlogik sowie elf Speicherelemente. Auf einem weiteren Plättchen befindet sich eine zweite Variante des Stromspannungswandlers mit einem integrierten Operationsverstärker, der anstelle der diskreten Ausführung eingesetzt werden kann.

#### 5. Schlussbemerkung

Zur Verbesserung der Sprachqualität wird in den neuesten CEPT-Empfehlungen eine 8-bit-Codierung vorgeschlagen. Im Blick darauf wurde die in diesem Bericht beschriebene Schaltungsanordnung versuchsweise auf 8 Stellen erweitert. Dabei hat sich gezeigt, dass der erweiterte Digital-Analog-Wandler für ein 8-bit-PCM-System verwendet werden kann.

#### Literatur

- [1] C. R. Pearman, A. E. Popodi: How to Design High-Speed D-A Converters. Electronics, 1964, p. 28...32.

- [2] E. F. Kovanic: A High-Accuracy 9-bit Digital-to-Analog Converter Operating at 12 Mc. IEEE Trans. on Communication and Electronics, March 1965, p. 185...191.

- [3] Experimental 224 Mb/s PCM Terminals. BSTJ Vol XLIV Nov. 1965 No. 9, p. 1813...1887.

- [4] DAS 1 219 973 Deutsche KI.: 21a1 36/12. Verfahren und Schaltungsanordnung zur Verringerung der bei der Übertragung eines codierten Wertes benötigten Stellenzahl, insbesondere in PCM-Systemen.

- [5] CCITT Com. XV No. 77-F, Annexe 1, S. 27ff, vom 14. 9. 1966.

Adresse des Autors: Pierre-André Merz, c/o Albiswerk Zürich AG Badenerstrasse 580, CH-8048 Zürich.