**Zeitschrift:** Ingénieurs et architectes suisses

**Band:** 125 (1999)

**Heft:** 1-2

Artikel: Mémoires vives à très haute densité

Autor: Sallese, Jean Michel / Fazan, Pierre

DOI: https://doi.org/10.5169/seals-79613

# Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. Mehr erfahren

# **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. En savoir plus

## Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. Find out more

**Download PDF: 23.11.2025**

ETH-Bibliothek Zürich, E-Periodica, https://www.e-periodica.ch

# Par Jean Michel Sallese et Pierre Fazan, Laboratoire d'Electronique Générale, EPFL, 1015 Lausanne

# Mémoires vives à très haute densité

Aussi discrets qu'omniprésents, les semi-conducteurs font aujourd'hui partie de notre vie quotidienne, qu'ils soient implantés sur les diverses cartes qui garnissent un portefeuille ou dans les nombreux appareils «intelligents» qui nous facilitent l'existence, mais leur fonctionnement demeure le plus souvent mystérieux. Sous l'appellation générique de «semi-conducteurs», se cachent une multitude de composants électroniques intégrés sur un support en silicium, le grand défi technologique consistant en leur miniaturisation continue. Les mémoires dites DRAM1, par exemple ont crû en capacité de stockage, de façon exponentielle, tandis que la dimension de leurs circuits diminuait sans cesse. La poursuite de cette évolution ne sera possible qu'avec l'exploration de structures tridimensionnelles et l'utilisation de nouveaux matériaux. Pour préparer la venue des mémoires DRAM de très haute densité, le laboratoire d'électronique générale de l'EPFL s'intéresse aux mécanismes de formation et de fabrication de structures en trois dimensions et participe au développement de nouveaux concepts de mémoires.

# Où s'arrête la miniaturisation?

Les différents composants électroniques qui équipent la plupart des appareils et équipements que nous utilisons (ordinateurs, téléphones, voiture) se présentent sous la forme d'une puce, d'une dimension souvent inférieure au centimètre carré, qui est intégrée sur un matériau aux propriétés de conduction électrique particulière appelé semi-conducteur. Parmi les différents types de semi-conducteurs, le silicium représente actuellement l'élément le plus communément utilisé. Par extension, ce terme de « semi-conducteur » qualifie tout le domaine des circuits électroniques intégrés.

Il s'agit d'un marché en pleine croissance (15 % par an, en moyenne) qui aura atteint les 140 milliards de dollars en 1998. Et les mémoires vives, ou *DRAM*, qui équipent tous les ordinateurs, représentent quinze à vingt pour cent des composants produits.

Le développement de ce marché est gouverné par le besoin permanent de réaliser des circuits électroniques numériques dont la densité en termes de composants unitaires, ainsi que la rapidité d'exécution sont de plus en plus élevées. Ainsi l'évolution des mémoires *DRAM* se caractérise par l'introduction, tous les trois ans, d'une nouvelle génération plus performante (quatre fois plus d'in-

formations) et plus compacte (la taille de la cellule unitaire diminue jusqu'à 40 % et sa surface baisse d'un facteur 2 à 3). Ces cellules unitaires sont ensuite répliquées en grand nombre et groupées pour constituer une mémoire. Et l'avenir de l'informatique et des télécommunications repose sur l'augmentation des performances de ces mémoires.

Les progrès technologiques de ces vingt-cing dernières années ont permis de multiplier par un million la capacité d'une mémoire, puce qui comporte actuellement 256 Mégabits (soit 256 millions de cellules unitaires sur lesquelles l'information va être stockée), pour une taille de 2,80 cm<sup>2</sup>. Cependant, les objectifs à moyen et long termes visent des densités excédant le Gigabit par puce (plus d'un milliard de cellules) et, pour 2015, l'introduction d'une mémoire de 1 Terabit (1012 cellules) si l'évolution actuelle se poursuit. A ces efforts de miniaturisation s'ajoutent des exigences de fiabilité et de qualité drastiques.

Nous nous proposons de donner ci-après un aperçu des principes de fonctionnement de ces mémoires *DRAM* et de leurs perspectives de développement.

Dans tout circuit numérique, et dans les ordinateurs en particulier,

l'information est représentée sous une forme binaire qui peut prendre deux valeurs discrètes à savoir 0 et 1. Un traitement efficace de l'information exige souvent la mémorisation de ces données sur un support digital. Ainsi. les premiers modèles de mémoires digitales dignes de ce nom étaientils constitués de tores, sortes d'aimants miniatures dans lesquels une information s'inscrivait sous la forme d'un champ magnétique. Par la suite, avec l'avènement des circuits intégrés, divers concepts de mémoires ont été proposés avec des densités d'intégration encore jamais égalées.

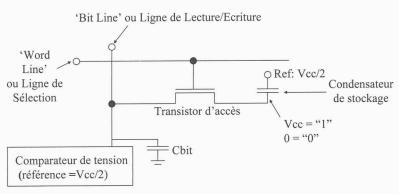

La structure d'une mémoire DRAM consiste en plusieurs millions, voire milliards, de cellules unitaires dont une représentation symbolique est donnée à la figure 1. Chaque cellule élémentaire est constituée d'un transistor d'accès et d'un condensateur de stockage. Dans cette cellule, l'information binaire est représentée sous la forme d'une charge électrique, présente sur l'électrode du condensateur qui est reliée au transistor d'accès. Le transistor d'accès (transistor de type MOS) est utilisé ici en simple interrupteur et a pour seul rôle d'isoler le condensateur du reste du circuit. Il est connecté, d'un côté à la «bit line», ou ligne d'écriture/lecture, de l'autre il est relié à la « word line », ou ligne de sélection. Ces deux accès suffisent à repérer la cellule mémoire. Cette facilité d'accès, à n'importe quelle cellule, à n'importe quel moment, justifie l'appelation de «random access memory », par opposition à un accès séquentiel à l'information. En supposant que le potentiel de référence du condensateur est de  $V_{cc}/2$  (où  $V_{cc}$  est la tension d'alimentation du circuit de la mémoire DRAM), une information binaire 1 ou 0 sera symbolisée par une charge de  $+C(V_{cc}/2)$  ou de

Fonctionnement des mémoires digitales

<sup>&</sup>lt;sup>1</sup> Pour « Dynamic Random Access Memory », soit mémoire RAM dynamique ou mémoire vive dynamique

• Cellule DRAM de base: 1 Transistor, 1 Condensateur, introduite en 1967 par R.H. Dennard (IBM)

Fig. 1.- Schéma d'une cellule élémentaire de mémoire DRAM

$-C(V_{cc}/2)$  (où C représente la capacité exprimée en farads), selon que le potentiel de la ligne d'écriture (bit line) ait été préalablement affecté à un potentiel égal à  $V_{cc}$  ou à 0 volt.

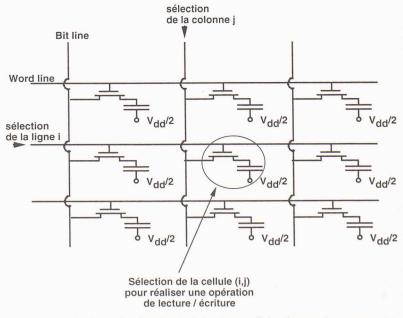

D'un point de vue géométrique, les lignes d'écriture (bit line) et de sélection (word line) sont perpendiculaires entre elles. Cette architecture permet d'organiser les cellules élémentaires sous une forme matricielle (fig. 2), ce qui accroît considérablement la densité d'intégration réalisable.

Cependant, des pertes de courant dans le circuit sont à l'origine de la décharge des condensateurs de stockage. Ces courants de fuite se produisent principalement au travers du transistor (qui n'est pas un interrupteur idéal malgré sa fiabilité) et du diélectrique qui constitue le condensateur de stockage. Aussi, la charge de la cellule mémoire doit-elle être rafraîchie pour pouvoir maintenir son état de charge, c'est à dire que l'information doit être lue et réécrite en permanence. Avec les technologies actuelles, la fréquence de réécriture est de l'ordre de la centaine de millisecondes. Une conséquence directe inhérente à ce type de dispositif est la perte définitive de l'information aussitôt que le circuit n'est plus alimenté en tension. Cette caractéristique a donné le nom de dynamiques à ces mé-

moires (DRAM), par opposition aux mémoires statiques (SRAM). Ce type de mémoire est donc volatile et se distingue des mémoires non volatiles (telles que les EPROM, EEPROM, Flash ou FERAM) qui conservent leur information même lorsque le circuit n'est plus alimenté.

L'écriture d'une information s'opère en activant le transistor au moyen de la ligne de sélection, connectant ainsi le condensateur de stockage à la ligne d'écriture dont on impose le potentiel. Par cette action, une charge apparaît 7 sur l'armature du condensateur (fig. 1). Ensuite, le transistor de commande retourne à son état «fermé» et isole à nouveau le condensateur. De même, lorsqu'il s'agit de lire une information présente sur une cellule particulière, l'interrupteur «transistor» est activé par l'intermédiaire de la ligne de sélection et l'information est recueillie sur la ligne d'écriture/lecture, entraînant de ce fait la décharge du condensateur. Selon la variation de potentiel détectée sur la ligne d'écriture, il est possible d'identifier le signe de la charge qui était présente sur l'armature du condensateur juste avant sa lecture. Cette opération très délicate s'effectue au moyen d'amplificateurs ultra-sensibles qui sont intégrés sur la puce mémoire.

Malheureusement, la ligne d'écriture possède sa propre capacité symbolisée ici par Cbit et dont la présence aura pour effet de réduire sensiblement la variation de potentiel à détecter. Aussi est-il indispensable que la charge présente sur les armatures du condensateur soit suffisamment élevée pour être détectée sans ambi-

Fig. 2.- Exemple de matrice de mémoire DRAM. Les cellules élémentaires sont assemblées en réseaux toujours plus denses.

valence et éviter ainsi toute erreur lors de la relecture.

La technologie actuelle des circuits de détection ne permet pas de réduire la capacité de stockage en deçà de 30 femto-farads (10-15 farads), ce qui représente environ 1 million d'électrons stockés sur les armatures d'un condensateur alimenté sous une tension de cinq volts environ. En dessous de cette valeur, il devient pratiquement impossible de relire une information avec une fiabilité proche de 100 %. De ce fait, la taille du condensateur de stockage est le facteur limitatif de la densité d'intégration des mémoires dynamiques, surtout lorsque l'on vise des générations de DRAM dont la densité devra excéder le Gigabit (Gb).

# Fabriquer un condensateur tridimensionnel

La nécessité de réaliser des mémoires *DRAM* de très haute densité (plus d'un Gigabit sur une même puce) se heurte actuellement à des problèmes technologiques complexes, auxquels s'ajoutent des exigences de fiabilité extrême, dans un contexte de production en masse. Une précision de l'ordre du centième de micron (10-5 millimètres) est exigée pour les composants qui seront intégrés sur des plaques de silicium pouvant atteindre 300 millimètres de diamètre.

La taille de la cellule mémoire unitaire, paramètre essentiel, doit être minimisée (sans violer pour autant le critère des 30 fF) afin de réaliser des puces dont les dimensions restent compétitives aussi bien d'un point de vue technologique qu'économique. Ainsi, la taille d'une cellule mémoire est passée de 30 mm² pour une densité de 1 Mb à 0,6 mm² pour 256 Mb. Le tableau reproduit à la figure 3 montre les prévisions pour les densités dépassant 256 Mb.

Pour réaliser cette réduction de la surface des cellules, plusieurs solutions ont été proposées. Elles se basent essentiellement sur la relation simple qui exprime la capacité d'un condensateur en fonction de seulement trois paramètres, à savoir la surface du condensateur (S), la nature du diélectrique (sa constante diélectrique relative  $\varepsilon$ ) ainsi que son épaisseur (d):

$C = \varepsilon \, \varepsilon_0 \, S/d$

où  $\varepsilon_0$  représente la permittivité du vide.

Avec cette contrainte d'une capacité de 30 fF par cellule, plusieurs stratégies ont été et sont encore poursuivies.

Dans les générations de mémoires d'une densité inférieure à 256 Kb (c'est à dire contenant moins de 256 000 cellules unitaires), les condensateurs étaient planaires et l'oxyde de silicium ou SiO<sub>2</sub>, produit directement par oxydation thermique du substrat ou disque de silicium, servait de diélectrique. Pour les densités allant de 1 à 16 Mb, la constante diélectrique de l'oxyde de silicium devenait insuffisante et l'industrie a opté pour le nitrure de silicium ou Si<sub>3</sub>N<sub>4</sub>, dont la constante diélectrique atteint 7,2 contre 3,9 pour l'oxyde de silicium. Dans ce cas, l'isolant se compose

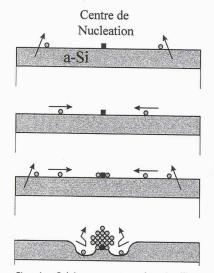

Fig. 4.– Schéma montrant la cristallisation du silicium (procédé HSG: Hemispherical Grained Silicium)

de deux couches diélectriques superposées, SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub>, désignées sous le nom de «ON». Cette association permet d'améliorer sensiblement la fiabilité de la structure en bénéficiant de la qualité supérieure que présente l'oxyde de silicium. Une solution apparemment simple, pour augmenter encore la capacité du condensateur, consiste à réduire l'épaisseur du diélectrique. Cependant, au-delà de 5 nm d'épaisseur, les électrons passent à travers l'isolant par un effet quantique appelé « effet tunnel». Tout se passe comme si, en dessous d'une certaine épaisseur, l'isolant devenait un très bon conducteur lorsqu'il est en présence d'un champ électrique! En outre, il devient très difficile de contrôler l'uniformité de films isolants si minces sur des disques de

| Caractéristiques/année                            | 1997    | 1999     | 2001                           | 2003                           | 2006      | 2009      | 2012       |

|---------------------------------------------------|---------|----------|--------------------------------|--------------------------------|-----------|-----------|------------|

| Densité de la<br>mémoire <i>DRAM</i> (bits)       | 256 Mb. | 1 gigab. | 2 gigab.                       | 4 gigab.                       | 16 gigab. | 64 gigab. | 256 gigab. |

| Surface de la cellule unitaire (µm²)              | 0,56    | 0,22     | 0,14                           | 0,09                           | 0,036     | 0,014     | 0,006      |

| Surface d'une «puce»<br>mémoire <i>DRAM</i> (cm²) | 2,80    | 4        |                                | 5,60                           | 7,90      | 11,20     | 15,80      |

| Diélectrique DRAM utilisé                         | ON      | ON       | Ta <sub>2</sub> O <sub>5</sub> | Ta <sub>2</sub> O <sub>5</sub> | BST       | BST       | BST        |

| Temps de rétention<br>de l'information (ms)       | 64-128  | 128-256  | 128-256                        | 256-512                        | 512-1024  | 1024-2048 | 2048-4096  |

silicium pouvant atteindre 20 ou 30 cm de diamètre.

Pour se lancer dans des densités supérieures (16 et 64 Mb), l'utilisation de la troisième dimension devenait indispensable. On réalisa ainsi des condensateurs ayant la forme de cylindres ou d'ailerons (stacked capacitors), afin d'obtenir une capacité importante avec une surface projetée minimale. Cependant, cette configuration ne permettait pas d'excéder les 64 Mb. Une autre solution efficace consiste à utiliser le silicium à grains hémisphériques ou HSG (Hemispherical Grained Silicium) obtenu par un traitement spécifique d'une couche de silicium amorphe. Le concept sous-jacent vise à augmenter la surface apparente du silicium en formant sur celle-ci des îlots de silicium nanométriques. Il devrait pouvoir être appliqué pour des mémoires d'une densité allant jusqu'à 4 Gb.

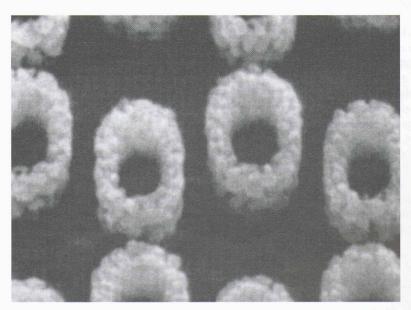

On peut résumer le processus de la manière suivante: après avoir déposé le silicium amorphe, qui représente l'électrode inférieure du condensateur de stockage, on élève la température vers 550°C, sous vide, de manière à permettre aux atomes de surface de se déplacer. Au cours de cette migration, les atomes de silicium vont rencontrer des sites préférentiels (sites de nucléation) aléatoirement répartis sur la surface, au contact desquels ils vont s'agglutiner. Ils formeront ainsi des nano-sphères dont les dimensions peuvent varier entre 10 et 50 nm pour les applications dans les DRAM. Dans la pratique, ce procédé permet d'accroître la surface du silicium d'un facteur 2,5 sans pour autant détériorer les caractéristiques de la structure. Un des avantages incontestables de cette technologie réside dans sa simplicité et dans sa totale compatibilité avec toutes les étapes de fabrication qui peuvent comptabiliser jusqu'à quatre cents manipulations lors de la fabrication d'une mémoire DRAM. La figure 5 montre des condensateurs de mémoires DRAM réalisés au moyen de cette technique.

# Matériaux exotiques et technologies nouvelles

Pour les densités de mémoire supérieures à 4 Gb, requises par les futurs ordinateurs, ces technologies deviennent insuffisantes. De nouveaux matériaux diélectriques, présentant une constante diélectrique bien supérieure à celle du nitrure de silicium, doivent être maîtrisés. Parmi les candidats po- 9 tentiels, l'oxyde de tantale Ta<sub>2</sub>O<sub>5</sub>, dont la constante diélectrique est voisine de 25, et certains oxydes complexes tels que le (Ba, Sr)TiO<sub>3</sub>, ou BST, à constante diélectrique supérieure à 100, sont vraisemblablement les matériaux d'avenir. Toutefois, l'utilisation de ces nouveaux matériaux ne va pas sans engendrer de nouveaux problèmes tels que la compatibilité de leur élaboration avec la technologie silicium conventionnelle et leur fiabilité à long terme. A noter cependant que le concept HSG reste entièrement compatible avec ces nouveaux procédés en mettant à profit la rugosité de la topographie pour accroître la surface qui recevra le diélectrique.

### Vers la «nanoélectronique»

La stratégie de développement des mémoires DRAM est double: d'une part faire évoluer aussi loin que possible les technologies existantes et, d'autre part, sonder les procédés de fabrication avancés faisant appels à des matériaux exotiques tels que le BST et le Ta<sub>2</sub>O<sub>5</sub>. Nul doute que les recherches avancées dans ces domaines de pointe auront des répercussions considérables non seulement dans le secteur des mémoires, mais également dans celui de la « nanoélectronique » qui requiert de nouveaux matériaux pour réaliser des composants tels que les transistors MOS dont la zone active équivaudrait au plus à trois cents atomes mis bout à bout!

Fig. 5.- Photo de condensateurs HSG tirée de l'article de Kinam Kim et al., IEEE Transactions on Electron Devices, vol. 45, no. 3, march 1998