**Zeitschrift:** Bulletin technique de la Suisse romande

**Band:** 92 (1966)

**Heft:** 8: Foire de Bâle, 16-26 avril 1966

**Artikel:** Circuits logiques à très faible consommation de puissance

Autor: Mange, Daniel

**DOI:** https://doi.org/10.5169/seals-68354

## Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. Mehr erfahren

#### **Conditions d'utilisation**

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. En savoir plus

#### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. Find out more

**Download PDF:** 18.11.2025

ETH-Bibliothek Zürich, E-Periodica, https://www.e-periodica.ch

# BULLETIN TECHNIQUE **DE LA SUISSE ROMANDE**

Paraissant tous les 15 jours

#### ORGANE OFFICIEL

- de la Société suisse des ingénieurs et des architectes

- de la Société vaudoise des ingénieurs et des architectes (SVIA) de la Section genevoise de la SIA de l'Association des anciens élèves de l'EPUL (Ecole polytechnique de l'Université de Lausanne)

- et des Groupes romands des anciens élèves de l'EPF (Ecole polytechnique fédérale de Zurich)

#### COMITÉ DE PATRONAGE

- Président: E. Martin, arch. à Genève Vice-président: E. d'Okolski, arch. à Lausanne Secrétaire: S. Rieben, ing. à Genève

- Membres:

- H. Gicot, ing.; M. Waeber, arch. G. Bovet, ing.; Cl. Grosgurin, arch.; J.-C. Ott, ing. Fribourg: Genève:

- Genève: G. Bovet, ing., Ci. Grosgata, arch.

Neuchâtel: J. Béguin, arch.

Valais: G. de Kalbermatten, ing.; D. Burgener, arch.

Vaud: A. Chevalley, ing.; A. Gardel, ing.;

M. Renaud, ing.; J.-P. Vouga, arch.

#### CONSEIL D'ADMINISTRATION

- de la Société anonyme du « Bulletin technique »

- Président: D. Bonnard, ing.

- Membres: Ed. Bourquin, ing.; G. Bovet, ing.; M. Bridel; J. Favre, arch.; A. Robert, ing.; J.-P. Stucky, ing.

Adresse: Avenue de la Gare 10, 1000 Lausanne

D. Bonnard, E. Schnitzler, S. Rieben, ingénieurs; M. Bevilacqua, Rédaction et Editions de la S.A. du « Bulletin technique »

Tirés à part, renseignements Avenue de Cour 27, 1000 Lausanne

RÉDACTION

| l an           |   | Fr. 40.—<br>» 33.— | Etranger | Fr. | 44.— |

|----------------|---|--------------------|----------|-----|------|

| Prix du numéro | » | » 2.—              | »        | »   | 2.50 |

Chèques postaux: «Bulletin technique de la Suisse romande »,  $N^{\circ}$  10 - 5778, Lausanne

Adresser toutes communications concernant abonnement, vente au numéro, changement d'adresse, expédition, etc., à: Imprimerie La Concorde, Terreaux 29, 1000 Lausanne

#### ANNONCES

#### Tarif des annonces:

| 1/1 | page |  |  | Fr. | 385.— |

|-----|------|--|--|-----|-------|

| 1/2 | >>   |  |  | >>  | 200.— |

| 1/4 | >>   |  |  | >>  | 102.— |

| 1/8 | >>   |  |  | >>  | 52.—  |

Adresse: Annonces Suisses S.A. Place Bel-Air 2. Tél. (021) 22 33 26, 1000 Lausanne et succursales

#### SOMMATRE

Circuits logiques à très faible consommation de puissance, par Daniel Mange, chaire électronique de l'EPUL.

Bibliographie. — Les congrès.

Documentation générale. — Nouveautés, informations diverses.

# CIRCUITS LOGIQUES À TRÈS FAIBLE CONSOMMATION **DE PUISSANCE**

par DANIEL MANGE, chaire d'électronique de l'Ecole polytechnique de l'Université de Lausanne (EPUL)

#### Avant-propos

Le développement de l'électronique ces dix dernières années est dû principalement aux possibilités offertes par les transistors. Le transistor non seulement a remplacé avantageusement le tube dans de nombreux domaines, mais a suscité des applications nouvelles. Parmi ces dernières, les plus importantes sont celles qui concernent le traitement « digital » de l'information. On spécifie par là que les grandeurs caractérisant cette information sont traitées sous forme de « digits », c'est-à-dire de chiffres ou de lettres, ou de suites de chiffres ou de lettres, ceci par opposition aux dispositifs dits « analogiques » qui utilisent l'information sous forme de variables continues. Une même information peut s'exprimer sous ces deux formes, ainsi l'heure peut être indiquée par la position des aiguilles (forme analogique) ou affichée par un ensemble de chiffres (forme digitale).

Une calculatrice électronique moderne avec ses multiples possibilités est probablement l'exemple le plus raffiné et spectaculaire du traitement digital de l'information. D'autres réalisations apparaissent chaque jour, élargissant le champ d'application des techniques digitales, contribuant entre autres à automatiser la fabrication, la production, à contrôler le trafic, bref, à seconder et remplacer l'esclave intellectuel moderne pour toutes tâches où son esprit est affecté à des besognes ingrates ne tolérant aucune fantaisie ou imagination, et devant répondre à des consignes strictes.

Si le transistor a permis l'essor considérable des techniques digitales auquel nous assistons, c'est qu'il se prête particulièrement bien à la réalisation de « circuits logiques ». Grâce à ces circuits logiques, on peut effectuer des « opérations logiques » beaucoup plus rapidement et commodément qu'avec les moyens connus auparavant. Sans entrer dans le détail des opérations ou fonctions logiques, rappelons qu'il s'agit de propositions relatives à deux possibilités : « juste » ou « faux », « présent » ou « absent » matérialisées dans les circuits logiques par deux états distincts appelés l'état « 0 » et l'état « 1 ». On peut s'étonner à première vue qu'une machine à calculer puisse fonctionner si elle ne travaille qu'avec des « 0 » et des « 1 ». L'exemple du télex ne transmettant sur la ligne télégraphique qu'une suite de « 0 » et de « 1 » nous détrompera.

Le circuit logique est donc l'élément de base commun à tout dispositif électronique destiné au traitement digital de l'information, quel que soit le but final recherché.

Nous espérons, par ce préambule, avoir souligné l'importance des techniques digitales dans l'électronique actuelle, et avoir permis au néophyte de se faire une idée très générale du circuit logique \*.

Il va de soi que l'enseignement de l'électronique à l'EPUL s'est adapté à l'évolution de cette branche. Désireux par ailleurs de contribuer au développement d'avantgarde dans ce domaine, nous avons entrepris depuis 1963 à la chaire d'électronique de l'EPUL des travaux de recherche grâce à l'aide du Fonds pour l'encouragement des recherches scientifiques (Fonds Hummler). Ces travaux ont principalement pour objet l'étude de circuits électroniques utilisables dans une montre électronique. L'impératif d'une pile à loger dans le boîtier d'une montre-bracelet et devant durer au moins une année nous a conduit à étudier des circuits consommant un courant extrêmement faible, de l'ordre de grandeur de 0,1 µA, soit environ le

millionième de celui d'une ampoule de lampe de poche. La conséquence d'une telle réduction de courant est une baisse de la cadence maximum à laquelle le circuit est encore susceptible de travailler, c'est donc une baisse de ses performances. Notre collaborateur, M. Daniel Mange, a étudié les lois qui caractérisent un tel comportement et a recherché systématiquement quelle structure de circuit logique s'avère la plus favorable sous cet aspect particulier.

Nous sommes reconnaissants au Bulletin technique de publier une étude aussi spécialisée et traitant une matière peu commune pour la majorité de ses lecteurs ; il témoigne ainsi de la participation de l'EPUL au développement des techniques modernes.

Professeur R. Dessoulavy.

\* Pour une documentation plus ample, consulter un ouvrage d'introduction aux circuits logiques tels : J. Korthals Altes : Circuits de logique à transistors. Monographie Philips ; ou P. Naslin : Principe des calculatrices numériques automatiques. Monographie Dunod.

#### Résumé

Le but de la présente étude est de déterminer les performances dynamiques de diverses structures logiques dans le domaine de la micropuissance  $(0,01 \pm 100 \ \mu W)$  par circuit).

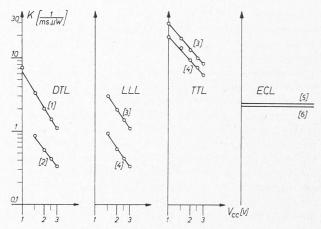

La mesure du temps de propagation moyen  $t_{pd}$  permet de comparer — en fonction de la puissance dissipée par étage P — la rapidité des portes « NOR » ou « NAND » dans six logiques différentes (RTL, DCTL, DTL, LLL, TTL et ECL). On représente alors pour chaque logique la variation de  $t_{pd}$  avec P et l'on calcule pour chaque mesure la valeur du coefficient de mérite  $K=1/(t_{pd}\cdot P)$ . Il est alors possible — à tension d'alimentation constante — de classer les différents types de logiques selon la valeur de K, et il apparaît que les logiques DCTL et TTL sont — à cet égard — les plus favorables.

#### 1. Introduction

Une étude des diviseurs de fréquence en anneau constitués par des circuits logiques à couplage direct DCTL (« Direct Coupled Transistor Logic »), nous a conduits à examiner systématiquement les performances d'autres types de logiques à de très faibles puissances.

Il est possible de montrer qu'à l'aide d'un seul type fondamental de circuit — porte du type NON-OU = = « NOR » ou NON-ET = « NAND » — on peut réaliser toutes les fonctions logiques désirées. Une série de mesures a donc été faite sur les portes « NOR » et « NAND » se rattachant à six types principaux de logiques (RTL, DCTL, DTL, LLL, TTL, ECL), pour mettre en évidence la rapidité obtenue en fonction de la consommation de puissance.

#### 2. Principe des mesures

Pour obtenir de façon simple une indication essentielle quant aux performances en vitesse des circuits testés, on réalise un oscillateur en anneau formé d'un nombre impair de portes « NOR » ou « NAND »; la sortie de la dernière de ces portes est alors directement reliée à l'entrée de la première. Le système global est instable et, à chaque étage, on observe un signal dont

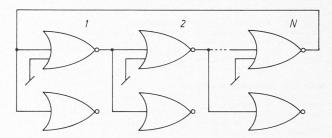

Fig. 1. — Oscillateur en anneau formé de N étages à portes « NOR ».

N impair; fan-in = 2 et fan-out = 2.

la fréquence F est liée au temps de propagation moyen  $t_{pd}$  par la relation suivante admise en général :

$$t_{pd} = \frac{1}{2N \cdot F}$$

où N est le nombre des étages couplés (fig. 1). Nos essais ont été entrepris avec N=3.

D'autre part — à tension d'alimentation constante — la variation de la résistance de charge de la porte « NOR » ou « NAND » étudiée permettra de modifier la puissance consommée. Le courant continu I absorbé par un étage et la tension d'alimentation  $V_{\it CC}$  détermineront la puissance dissipée P.

Enfin — pour chaque valeur de la résistance de charge (100 k $\Omega$ , 1 M $\Omega$ , 10 M $\Omega$  et éventuellement 100 M $\Omega$ ) — on mesure les valeurs de  $t_{pd}$  et de P à des tensions  $V_{CC}$  de 3 V, 2,5 V, 2 V, 1,5 V et 1 V, sauf dans le cas de la logique non saturée ECL où les tensions d'alimentation restent fixes. Dans le cas où la résistance de charge vaut 10 M $\Omega$ , ces mesures sont alors répétées quatre fois, selon le tableau suivant :

| Fan-in =           | Fan-out =          |

|--------------------|--------------------|

| nombre des entrées | nombre des sorties |

| 1                  | 1                  |

| 1                  | 2                  |

| 2                  | 1                  |

| 2                  | 2                  |

Rappelons qu'une porte logique caractérisée par un fan-in de 2 et un fan-out de 2 permet déjà de réaliser un diviseur de fréquence du type « en anneau ».

Pour conclure, la connaissance de  $t_{pd}$  et de P permettra de caractériser chaque logique par un facteur de mérite  $K=1/(t_{pd}\cdot P)$ , facteur qu'on désire le plus grand possible.

#### 3. Les différents types de portes logiques

#### 3.1 Généralités

La figure 2 montre l'ensemble des portes logiques qui ont été mesurées, la configuration électrique de chacune d'elles et sa fonction logique, l'abréviation et le symbole généralement admis par les constructeurs.

Le transistor utilisé, du type 2N1711, est caractérisé par un très faible courant de fuite  $I_{CBo}$  ( $10^{-9}$  A) et par un grand gain  $h_{FE}$  à de très faibles courants ( $h_{FE} \geq 30$  à  $I_C = 1$   $\mu$ A). Enfin, toutes les mesures ont été exécutées à la température ambiante :  $T = T_{amb} \cong 20^{\circ}$ C. Il est bien clair que les changements de la température peuvent entraı̂ner des modifications considérables dans les performances relevées, par suite notamment des variations de la tension base-émetteur  $V_{BE}$  des transistors.

## 3.2 Logique RTL: Resistor Transistor Logic

Etant donnée l'utilisation d'un transistor à très faible courant de fuite  $I_{CBo}$ , il est possible de négliger la polarisation auxiliaire  $V_{BB}$  nécessaire au blocage de la base ; cette remarque est également valable pour tous les autres types de logiques mesurées ci-après.

Soulignons encore que la valeur de la résistance  $R_B$  n'a pas été calculée selon la méthode du « cas le plus défavorable », mais qu'on a arbitrairement choisi trois situations différentes :

$\begin{array}{ll} \text{Cas RTL}_1:\,R_B=R_C/10\\ \text{Cas RTL}_2:\,R_B=R_C\\ \text{Cas RTL}_3:\,R_B=10\cdot R_C \end{array}$

En effet, les mesures entreprises avec  $R_B = R_C/10$  (cas RTL<sub>1</sub>) ont montré l'impossibilité du fonctionnement avec un fan-in = 2 par le fait que les conditions statiques n'étaient pas satisfaites. C'est pourquoi on a testé le dispositif avec des valeurs de  $R_B$  supérieures à  $R_C/10$  (cas RTL<sub>2</sub> et RTL<sub>3</sub>).

## 3.3 Logique DCTL: Direct Coupled Transistor Logic

La logique DCTL est caractérisée par un couplage direct entre le collecteur d'un transistor et la base de celui de l'étage suivant. Toutefois, pour garantir un fan-out supérieur à un et résoudre le problème de la répartition du courant dans les bases de plusieurs transistors alimentés parallèlement (« current hogging problem » dû à la dispersion des caractéristiques de  $V_{BE}$ ), on est contraint d'imposer une résistance  $R_B$  non nulle : dans ce cas, on obtient une logique DCTL modifiée, pour laquelle on choisit arbitrairement  $R_B = R_C/10$ :

Cas DCTL:  $R_B = 0$ Cas DCTL modifiée:  $R_B = R_C/10$

## 3.4 Logique DTL: Diode Transistor Logic

La porte « NOR » est ici constituée par des diodes au silicium à faible courant de fuite (OA 202) suivies d'une résistance de base dont la valeur est :  $R_B = R_C/10$ .

# 3.5 Logique ECL: Emitter Coupled Logic

La logique ECL est non saturée, c'est-à-dire que la jonction base-collecteur des transistors en commutation

| Logique                                          | Schéma                                                                                    | Fonction | Symbole                             |

|--------------------------------------------------|-------------------------------------------------------------------------------------------|----------|-------------------------------------|

| RTL  Resistor Transistor Logic                   | V <sub>CC</sub>                                                                           | NOR      |                                     |

| DCTL  Direct Coupled Transistor Logic            | V <sub>CC</sub><br>R <sub>C</sub>                                                         | NOR      |                                     |

| DCTL<br>modifiée                                 | V <sub>CC</sub><br>R <sub>C</sub>                                                         | NOR      | $Z = \overline{A} + + \overline{M}$ |

| DTL<br>Diode<br>Transistor<br>Logic              | V <sub>CC</sub><br>R <sub>C</sub>                                                         | NOR      |                                     |

| ECL Emitter Coupled Logic  (Logique non saturée) | $R_{\varepsilon}$ $R_{\varepsilon}$ $R_{\varepsilon}$ $R_{\varepsilon}$ $R_{\varepsilon}$ | NOR      |                                     |

|                                                  | V <sub>CC</sub> R <sub>B</sub>                                                            | NAND     | A                                   |

| TTL<br>Transistor<br>Transistor<br>Logic         | V <sub>CC</sub>                                                                           | NAND     | Z = A··M                            |

Fig. 2. — Les différents types de portes logiques.

n'est à aucun moment polarisée dans le sens de la conduction; en évitant ainsi de stocker des charges dans cette jonction, on raccourcit le délai d'évacuation (« storage delay ») et l'on obtient une vitesse de commutation supérieure à tous les autres types de logiques pour des courants de collecteur élevés. Cependant, cette logique ne présente que peu d'intérêt à de très faibles puissances; on la représente uniquement à titre comparatif.

En choisissant arbitrairement les résistances aux valeurs suivantes :

$$R_E=10~\rm{M}\Omega\pm5~\%$$

;  $1~\rm{M}\Omega\pm5~\%$  ;  $100~\rm{k}\Omega\pm5~\%$  et  $R_C=R_E/10,$

on a déterminé par le calcul du « cas le plus défavorable » — et pour chacune des trois résistances  $R_E$  — les valeurs des tensions d'alimentation  $V_{EE}$  et  $V_{CC}$  pour lesquelles on évite la saturation des transistors.

# 3.6 Logique LLL: Low Level Logic

La porte à diodes est reliée ici à la base du transistor par l'intermédiaire de deux autres diodes en série, dans le but de garantir un blocage complet de ce même transistor lorsque l'étage précédent est dans l'état de saturation.

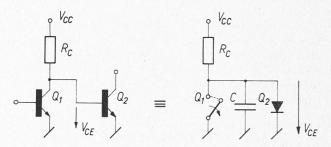

## 3.7 Logique TTL: Transistor Transistor Logic

Dans ce cas, la porte « NAND » est dérivée de la solution LLL: les diodes d'entrée sont remplacées par une série de transistors dont bases et collecteurs sont communs, tandis que les émetteurs constituent les différents fan-in. Ajoutons que, actuellement, la technique des circuits intégrés permet de réaliser un transistor unique à émetteurs multiples.

#### 4. Représentation des mesures

# 4.1 Temps moyen de propagation $t_{pd}$ et puissance dissipée par étage P

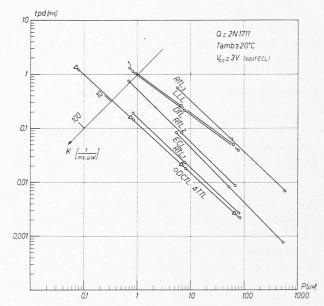

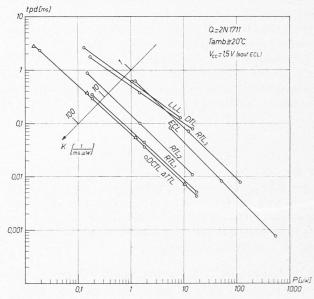

Pour comparer globalement les performances en fréquence des différents types de logique étudiées, on a représenté — à tension d'alimentation  $V_{CC}$  constante — les valeurs de  $t_{pd}$  en fonction de P pour une gamme des résistances de charge de 100 k $\Omega$  à 10 M $\Omega$  — et jusqu'à 100 M $\Omega$  pour les logiques DCTL et TTL — avec un fan-in = 1 et un fan-out = 1:

sur la figure 3 :  $V_{cc} = 3$  V (sauf pour la logique ECL) ;

sur la figure 4 :  $V_{CC} = 1.5 \text{ V}$  (sauf pour la logique ECL).

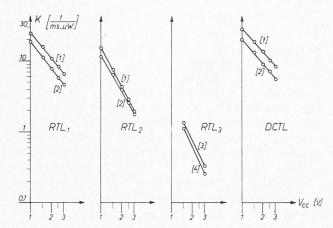

## 4.2 Facteur de mérite K

Dans le cas où l'on désire à la fois une fréquence de fonctionnement maximum et une consommation de puissance minimum, on cherchera à obtenir un facteur de mérite K maximum, avec  $K=1/(t_{pd}\cdot P)$ . On représente alors — pour chaque type de logique — la variation de K avec la tension d'alimentation  $V_{cc}$ , à résistance de charge constante, avec un fan-in = 1 et un fan-out = 1:

sur la figure 5 : logiques RTL<sub>1</sub>, RTL<sub>2</sub>, RTL<sub>3</sub> et DCTL; sur la figure 6 : logiques DTL, LLL, TTL et ECL.

#### 5. Interprétation des mesures

# 5.1 Allure générale des phénomènes transitoires dans la logique DCTL à très faible courant

Raisonnons sur une porte DCTL (fan-in = 1 et fanout = 1) qui est connectée à une autre porte selon le schéma de la figure 7.

Considérant que  $Q_1$  conduisait et  $Q_2$  était bloqué, étudions le renversement de la situation à la suite d'un

Fig. 3. — Variation du temps moyen de propagation  $t_{pd}$  en fonction de la puissance dissipée par étage P.

$V_{CC}=3$  V (sauf pour la logique ECL) ; fan-in =1 ; fan-out =1.

Fig. 4. — Variation du temps de propagation moyen  $t_{pd}$  en fonction de la puissance dissipée par étage P.

$V_{\it CC} = 1,\! 5$  V (sauf pour la logique ECL) ; fan-in = 1 ; fan-out = 1.

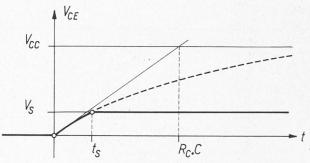

blocage brusque de  $Q_1$ . La figure 8 montre que la tension  $V_{BE}$  croît jusqu'à la valeur  $V_s$  caractérisant la saturation de  $Q_2$ .

# 5.2 Calcul du facteur de mérite K pour la logique DCTL Pour une tension de seuil $V_s$ petite vis-à-vis de $V_{CC}$ , il vient : $t_s \cong V_s \cdot \frac{R_C \cdot C}{V_{CC}}$ où C représente la capacité totale des transistors et des connexions.

Le temps de propagation moyen  $t_{pd}$  étant proportionnel à  $t_s$ , et la puissance moyenne par étage P étant proportionnelle à  $\frac{V_{CC}^2}{R_C}$ , alors K vaut :

$$K = \frac{1}{t_{pd} \cdot P} \sim \frac{1}{C \cdot V_s \cdot V_{CC}}$$

Fig. 5. — Facteur de mérite  $K=1/(t_{pd}\cdot P)$  en fonction de la tension d'alimentation  $V_{CC}$  pour les logiques RTL<sub>1</sub>, RTL<sub>2</sub>, RTL<sub>3</sub> et DCTL.

Fan-in = 1 et fan-out = 1. Cas [1]:  $R_C=10~M\Omega$  ; [2]:  $R_C=100~k\Omega$  ; [3]:  $R_C=1~M\Omega$  ; [4]:  $R_C=10~k\Omega$  .

K est donc une fonction hyperbolique de  $V_{CC}$ , caractérisée par une pente de —45° effectivement observée dans le diagramme logarithmique de la figure 5 (cas DCTL). Quand la résistance de charge  $R_C$  augmente, la tension  $V_s \equiv V_{BE}$  décroît légèrement par suite de la diminution du courant de base, ce qui entraîne une augmentation de K (cf. courbes [1] et [2] de la figure 5).

De plus, cette relation montre que le coefficient de mérite K ne peut être amélioré notablement que par deux moyens :

- Diminution des capacités internes du transistor utilisé ainsi que des capacités parasites des connexions.

- 2. Diminution de la tension d'alimentation  $V_{cc}$ .

L'élément actif étant donné (transistor 2N1711), le seul paramètre libre est  $V_{CC}$ ; pour avoir K maximum, cette valeur doit être la plus petite possible, en respectant toutefois l'hypothèse de départ :  $V_{CC} \gg V_s \equiv V_{BE}$ .

#### 5.3 Relations entre temps de propagation t<sub>pd</sub> et puissance P

Dans le cas de la logique DCTL toujours, on tire de la valeur de K la relation suivante:

$$t_{pd} \sim C \cdot V_{CC} \cdot \frac{V_s}{P} = \frac{C \cdot V_s}{I}$$

A tension  $V_{CC}$  constante,  $t_{pd}$  est donc pratiquement une fonction hyperbolique de la puissance P; il est représenté par une droite de pente —45° dans le graphique logarithmique. Les mesures des figures 3 et 4 (logique DCTL) corroborent cette hypothèse, avec un angle toutefois légèrement inférieur à 45° par suite de la diminution de  $V_s \equiv V_{BE}$  à de très faibles courants. Par ailleurs, la formule précédente montre que  $t_{pd}$  varie inversement proportionnellement à I, quelle que soit  $V_{CC}$ .

#### 5.4 Mesures sur les autres logiques

Les résultats mesurés sur les autres types de logiques (à l'exception de ECL) diffèrent de ceux qu'on vient d'analyser essentiellement par la présence de tensions de seuil  $V_s$  différentes :

soit par l'adjonction de résistances de base supplémentaires;

Fig. 6. — Facteur de mérite  $K=1/(t_{pd}\cdot P)$  en fonction de la tension d'alimentation  $V_{CC}$  pour les logiques DTL, LLL, TTL et ECL.

$\begin{array}{l} \text{Fan-in} = 1 \text{ et fan-out} = 1, \\ \text{Cas } [1] : R_C = 10 \ M\Omega \, ; \, [2] : R_C = 100 \ k\Omega \, ; \, [3] : R_B = 10 \ M\Omega \, ; \, [4] : R_B = \\ = 100 \ k\Omega \, ; \\ [5] : V_{EE} = -5,25 \ V \, ; \ V_{CC} = +0,80 \ V \, ; \ R_E = 100 \ k\Omega \, ; \\ [6] : V_{EE} = -5,25 \ V \, ; \ V_{CC} = +0,65 \ V \, ; \ R_E = 10 \ M\Omega. \end{array}$

Fig. 7. — Porte DCTL et schéma équivalent pour le blocage.

Fig. 8. — Transitoire de blocage du transistor  $Q_1$ .

2. soit par l'adjonction d'un transistor ou de diodes supplémentaires.

# 5.5 Effets du fan-in et du fan-out

Les essais avec des fan-in = 2 et fan-out = 2 ont été entrepris exclusivement dans le cas où la résistance de charge vaut  $10 \text{ M}\Omega$ , et ils ont permis de classer les logiques en quatre groupes caractéristiques :

Le groupe 1 (RTL<sub>2</sub>, DCTL, DCTL modifiée), caractérisé par des portes à résistances ou à transistors, montre que le fan-out a peu d'influence sur le facteur de mérite K. Par contre, dans les cas où le fan-in est obtenu par la mise en parallèle de deux transistors (DCTL et DCTL modifiée), on remarque une diminution très nette de K. En effet, un tel montage conduit à doubler pratiquement la valeur de la capacité  $C_{BC}$ , ralentissant ainsi considérablement le temps de blocage.

Le groupe 2 (DTL) montre que les portes à diodes permettent de réaliser des fan-in sans influence sur le temps de propagation. Seul le fan-out ralentit quelque peu la vitesse de fonctionnement.

Le groupe 3 (ECL) n'a pas été testé : on sait que, dans une telle logique, les influences d'un fan-in et d'un fanout supplémentaires sont négligeables.

Le groupe 4 enfin (LLL et  $\overline{\text{TTL}}$ ) est constitué par des portes logiques du type « NAND ». Dans ce cas, augmenter le fan-out conduit à réduire la constante de temps  $R_B \cdot C$ ; c'est pourquoi — dans le cas  $\overline{\text{TTL}}$  notamment — pour un fan-out de 2, le facteur de mérite K est augmenté de 50 % environ. Le fan-in est — par contre — sans aucune influence pour  $\overline{\text{LLL}}$  (porte à diodes) et d'une légère influence pour  $\overline{\text{TTL}}$  (porte à transistors).

Dans la plupart des cas, les influences sur  $t_{pd}$  dues au fan-in et au fan-out sont superposables.

#### 6. Conclusions

Il est possible de réaliser un diviseur de fréquence en anneau avec un seul type de circuit : une porte « NOR » (ou « NAND ») caractérisée par un fan-in = 2 et par un fan-out = 2.

On désire obtenir une telle porte pour laquelle le facteur de mérite K soit maximum. Des trois logiques dont les performances à cet égard sont les meilleures — TTL, DCTL et DCTL modifiée — nous résumons sur le tableau 1 les valeurs de K à tension d'alimentation  $V_{CC}$  constante.

Tableau 1

Comparaisons du facteur de mérite K pour les trois logiques TTL, DCTL et DCTL modifiée

| Logique VCC      | 3 V  | 2,5 V | 2 V   | 1,5 V | 1 V  |

|------------------|------|-------|-------|-------|------|

| TTL              | 7,85 | 9,95  | 13,05 | 17,95 | 30   |

| DCTL             | 8,2  | 10    | 13,4  | 18,4  | 28,3 |

| DCTL<br>modifiée | 6,5  | 8,2   | 10,8  | 15,7  | 24,3 |

$\begin{array}{l} {\rm Fan\text{-}in}=1\;;\;{\rm fan\text{-}out}=1\;;\\ Rc\;\;({\rm ou}\;\;R_B\;\;{\rm pour}\;\;{\rm TTL})=10\;\;M\Omega\;;\\ R_B\;\;({\rm pour}\;\;{\rm DCTL}\;\;{\rm modifi\acute{e}e})=1\;\;M\Omega\;;\\ [K]={\rm kHz}/\mu{\rm W}=10^{+9}\cdot J^{-1} \end{array} \label{eq:fitting}$

Pour des fan-in et fan-out supérieurs, les résultats sont consignés dans le tableau 2.

Tableau 2

Facteur de mérite K

| $_{\rm Logique} v_{\rm \it CC}$ | 3 V  | 2,5 ∇ | 2 ∇  | 1,5 ∇ | 1 ∇  |

|---------------------------------|------|-------|------|-------|------|

| TTL                             | 10,5 | 13,1  | 16,4 | 21,9  | 40,5 |

| DCTL                            | 6,15 | 7,55  | 9,7  | 12,8  | 19,4 |

| DCTL<br>modifiée                | 4,8  | 6     | 7,75 | 11,1  | 17,3 |

$\begin{array}{l} \text{Fan-in} = 2 \; ; \; \text{fan-out} = 2 \; ; \\ R_{\mathcal{C}} \; \; (\text{ou} \; R_{\mathcal{B}} \; \text{pour} \; \text{TTL}) = 10 \; M\Omega \; ; \\ R_{\mathcal{B}} \; (\text{pour} \; \text{DCTL} \; \text{modifiée}) = 1 \; M\Omega \; ; \\ [K] = \text{k} \, \text{Hz} / \mu \text{W} = 10^{+9} \cdot J^{-1} \end{array} ;$

On voit donc que la logique TTL est extrêmement avantageuse, surtout par le fait qu'une augmentation du fan-out réduit son temps de propagation moyen  $t_{pd}$ . Il semble que c'est avec elle que les performances du rapport fréquence/puissance d'un diviseur en anneau seront optimales: comme des conditions de stabilité statique empêchent la réalisation pratique des circuits DCTL (« current hogging problem »), c'est donc avec les structures DCTL modifiée et TTL que nous comptons poursuivre nos essais sur des diviseurs de fréquence en anneau.

Les conclusions auxquelles nous avons abouti sont valables pour la température ambiante ( $T_{\rm amb} \cong 20^{\rm o}{\rm C}$ ) et pour le transistor 2N1711. Il va de soi que l'effet de la température ne doit pas être négligé dans le choix d'un système : rappelons à cet égard que l'utilisation de très faibles tensions d'alimentation  $V_{CC}$  se heurte à des difficultés à de basses températures, étant donné que  $V_{BE}$  augmente et  $h_{FE}$  diminue. D'autre part, nous sommes conscients du fait qu'il existe des transistors bien meilleurs que celui choisi pour les essais (2N1711) : ce dernier était en effet le seul à disposition au début de nos travaux.

Il est aussi évident que les facilités d'intégration des différentes logiques sont également déterminantes pour le choix d'un circuit qui sera réalisé sous la forme microminiaturisée.

Disons enfin que nos conclusions rejoignent celles d'autres auteurs ayant surtout exploré des domaines de puissance supérieurs au µW.

#### BIBLIOGRAPHIE

- (1) Zeller, J. et Dessoulavy, R.: Propriétés de transistors « Planar » au silicium à de très faibles courants. Bulletin technique de la Suisse romande n° 25 (1963), p. 405-411.

- (2) Moore, G. E.: Semiconductor Integrated Circuits. Microelectronics. McGraw-Hill (1963), p. 325-332.

- (3) BOULTER, B. A.: The Multiple Emitter Transistor in Low Power Logic Circuits. Micropower Electronics. Pergamon Press (1964), p. 105-120.

- (4) Meindl, J. D.: Static and Dynamic Performance of Micropower Transistor Logic Circuits. Proceedings of the IEEE, December (1964), p. 1575-1580.

- (5) GAERTNER, W. W.: Nanowatt Devices. Proceedings of the IEEE, June (1965), p. 592-604.

- (6) Mange, D.: Diviseur de fréquence à très faible consommation de puissance. Bulletin technique de la Suisse romande nº 19 (1964), p. 334-336.

Ce travail a été effectué avec l'aide du Fonds pour l'encouragement des recherches scientifiques, auquel nous exprimonsnotre gratitude.

Adresse de l'auteur: Daniel Mange, ing. dipl. EPUL Chaire d'électronique de l'EPUL 16, ch. de Bellerive 1000 Lausanne