**Zeitschrift:** Bulletin technique de la Suisse romande

**Band:** 89 (1963)

**Heft:** 25

**Artikel:** Propriétés de transistors "Planar" au silicium à de très faibles courants

**Autor:** Zeller, J. / Dessoulavy, R.

**DOI:** <https://doi.org/10.5169/seals-66359>

#### Nutzungsbedingungen

Die ETH-Bibliothek ist die Anbieterin der digitalisierten Zeitschriften auf E-Periodica. Sie besitzt keine Urheberrechte an den Zeitschriften und ist nicht verantwortlich für deren Inhalte. Die Rechte liegen in der Regel bei den Herausgebern beziehungsweise den externen Rechteinhabern. Das Veröffentlichen von Bildern in Print- und Online-Publikationen sowie auf Social Media-Kanälen oder Webseiten ist nur mit vorheriger Genehmigung der Rechteinhaber erlaubt. [Mehr erfahren](#)

#### Conditions d'utilisation

L'ETH Library est le fournisseur des revues numérisées. Elle ne détient aucun droit d'auteur sur les revues et n'est pas responsable de leur contenu. En règle générale, les droits sont détenus par les éditeurs ou les détenteurs de droits externes. La reproduction d'images dans des publications imprimées ou en ligne ainsi que sur des canaux de médias sociaux ou des sites web n'est autorisée qu'avec l'accord préalable des détenteurs des droits. [En savoir plus](#)

#### Terms of use

The ETH Library is the provider of the digitised journals. It does not own any copyrights to the journals and is not responsible for their content. The rights usually lie with the publishers or the external rights holders. Publishing images in print and online publications, as well as on social media channels or websites, is only permitted with the prior consent of the rights holders. [Find out more](#)

**Download PDF:** 18.02.2026

**ETH-Bibliothek Zürich, E-Periodica, <https://www.e-periodica.ch>**

# BULLETIN TECHNIQUE DE LA SUISSE ROMANDE

paraissant tous les 15 jours

## ORGANE OFFICIEL

de la Société suisse des ingénieurs et des architectes

de la Société vaudoise des ingénieurs et des architectes (S.V.I.A.)

de la Section genevoise de la S.I.A.

de l'Association des anciens élèves de l'EPUL (Ecole polytechnique

de l'Université de Lausanne)

et des Groupes romands des anciens élèves de l'E.P.F. (Ecole

polytechnique fédérale de Zurich)

## COMITÉ DE PATRONAGE

Président : E. Martin, arch. à Genève

Vice-président : E. d'Okolski, arch. à Lausanne

Secrétaire : S. Rieben, ing. à Genève

Membres :

Fribourg : H. Gicot, ing.; M. Waeber, arch.

Genève : G. Bovet, ing.; Cl. Grosgeurin, arch.; J.-C. Ott, ing.

Neuchâtel : J. Béguin, arch.; R. Guye, ing.

Valais : G. de Kalbermatten, ing.; D. Burgener, arch.

Vaud : A. Chevalley, ing.; A. Gardel, ing.;

M. Renaud, ing.; J.-P. Vouga, arch.

## CONSEIL D'ADMINISTRATION

de la Société anonyme du « Bulletin technique »

Président : D. Bonnard, ing.

Membres : Ed. Bourquin, ing.; G. Bovet, ing.; M. Bridel; J. Favre,

arch.; A. Robert, ing.; J.-P. Stucky, ing.

Adresse : Avenue de la Gare 10, Lausanne

## RÉDACTION

D. Bonnard, E. Schnitzler, S. Rieben, ingénieurs ; M. Bevilacqua,

architecte

Rédaction et Editions de la S. A. du « Bulletin technique »

Tirés à part, renseignements

Avenue de Cour 27, Lausanne

## ABONNEMENTS

|                          |                 |                   |

|--------------------------|-----------------|-------------------|

| 1 an . . . . .           | Suisse Fr. 34.— | Etranger Fr. 38.— |

| Sociétaires . . . . .    | » 28.—          | » 34.—            |

| Prix du numéro . . . . . | » 1.60          |                   |

Chèques postaux : « Bulletin technique de la Suisse romande »,

N° II 57 76, Lausanne

Adresser toutes communications concernant abonnement, vente au

numéro, changement d'adresse, expédition, etc., à : Imprimerie

La Concorde, Terreaux 29, Lausanne

## ANNONCES

Tarif des annonces :

1/1 page . . . . . Fr. 350.—

1/2 " . . . . . " 180.—

1/4 " . . . . . " 93.—

1/8 " . . . . . " 46.—

Adresse : Annonces Suisses S. A.

Place Bel-Air 2. Tél. (021) 22 33 26. Lausanne et succursales

Propriétés de transistors « Planar » au Silicium à de très faibles courants, par J. Zeller et R. Dessoulavy, chaire d'électronique de l'Ecole polytechnique de l'Université de Lausanne (EPUL).

Bibliographie. — Les congrès.

Documentation générale. — Documentation du bâtiment. — Nouveautés, informations diverses.

## PROPRIÉTÉS DE TRANSISTORS « PLANAR » AU SILICIUM A DE TRÈS FAIBLES COURANTS

par J. ZELLER et R. DESSOULAVY, chaire d'électronique de l'Ecole polytechnique de l'Université de Lausanne (EPUL).

### Sommaire

*Les propriétés statiques et dynamiques relevées sur des transistors « Planar » au Si confirment la validité du schéma de remplacement en  $\pi$ . Grâce à ce schéma, on peut prévoir le comportement en régime alternatif ou en régime d'impulsions d'un montage amplificateur. Ces résultats sont confirmés par l'expérience. Aux très faibles courants, la fréquence d'utilisation maximum d'un montage à transistors est réduite considérablement du fait de l'importance relative des capacités parasites.*

### 1. Introduction

Il peut être intéressant, dans certaines utilisations, de réduire au minimum la puissance consommée par des dispositifs à transistors.

Les raisons en sont les suivantes :

- L'énergie à disposition est faible (par exemple satellite, montre électronique, appareils portables en général, si leur poids ou leur volume sont limités).

- La dissipation de chaleur par élément doit être réduite au minimum (circuits à grande densité d'éléments, pour lesquels l'évacuation de la chaleur sans augmentation excessive de la température locale limite la dissipation par élément).

Pour diminuer la consommation d'énergie d'un dispositif à transistors, il faut réduire la tension et le courant.

La tension de service ne peut guère être réduite en dessous du volt, étant donné la tension nécessaire à la polarisation de la diode base-émetteur ; on peut agir de manière beaucoup plus efficace sur le courant, en le réduisant à des valeurs extrêmement faibles de l'ordre de grandeur de  $10^{-9}$  A.

Cependant, les transistors usuels au Ge ne peuvent fonctionner à de très faibles courants pour les raisons suivantes :

- courant inverse de collecteur  $I_{CB_0}$  trop élevé ;

- baisse du gain en courant  $h_{FE}$ , due principalement à la recombinaison des porteurs minoritaires à la surface du transistor dans la région de la jonction base-émetteur.

L'utilisation de transistors au Si permet d'obtenir des courants inverses pratiquement négligeables ( $I_{CB_0} < 10^{-9}$  A). D'autre part, grâce au procédé « Planar » (protection de la surface du transistor, en particulier des

Fig. 1.

Transistor *npn* — définition des courants et tensions.

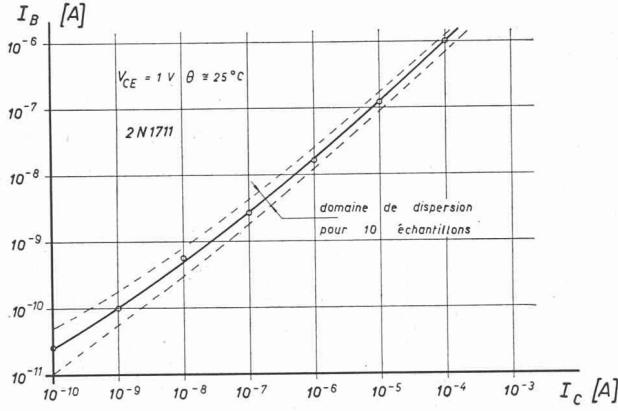

Fig. 2.1. — Courant de base  $I_B$  en fonction du courant de collecteur  $I_C$ .

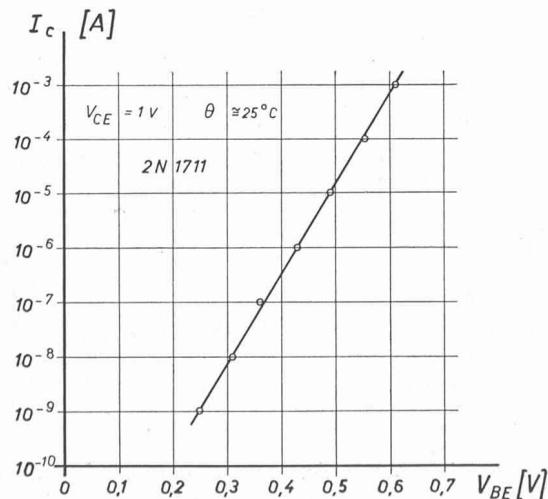

Fig. 2.2. — Gain en courant  $h_{FE}$  et  $h_{re}$  en fonction du courant de collecteur  $I_C$ .

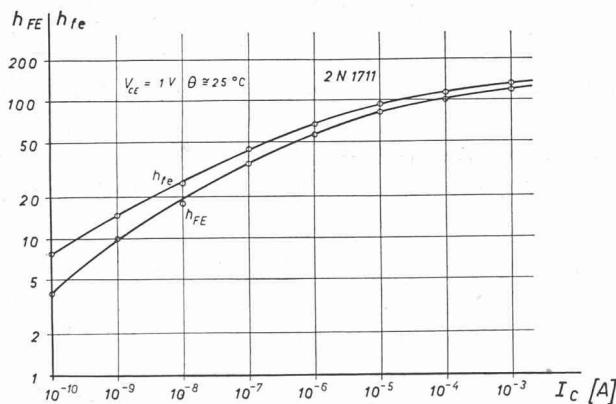

Fig. 2.3. — Courant de collecteur  $I_C$  en fonction de la tension base-émetteur  $V_{BE}$ .

jonctions, par une couche passive d'oxyde de Si), la valeur de  $h_{FE}$  est encore acceptable à de très faibles courants. Ainsi, pour un transistor 2N 1711, on obtient pour  $I_C = 10^{-9} \text{ A}$ ,  $h_{FE} \approx 10$ .

Dans l'étude suivante, nous vérifierons la validité du schéma de remplacement en  $\pi$  pour de tels transistors fonctionnant à de faibles courants, et mettrons en évidence les limitations de leur utilisation.

## 2. Caractéristiques statiques d'un transistor « Planar »

Dans les exemples qui suivent, nous avons utilisé le transistor 2N 1711 \*.

Les courants et tensions sont définis par le schéma de la figure 1.

Les caractéristiques moyennes de dix échantillons sont représentées par les diagrammes des figures 2.1 à 2.5.

### 2.1 Courant de base en fonction du courant de collecteur $I_B = f(I_C)$

### 2.2 Gain en courant en fonction du courant de collecteur

$$h_{FE} = \frac{I_C}{I_B} = f(I_C) \quad h_{re} = \frac{dI_C}{dI_B} = f(I_C)$$

Le gain en courant continu est déterminé à partir de  $I_B = f(I_C)$ .

D'autre part, on montre que le gain pour les accroissements

$$h_{re} = \frac{dI_C}{dI_B} = h_{FE} \frac{d \ln I_C}{d \ln I_B}$$

Cette relation permet de déterminer  $h_{re}$  à partir du diagramme  $I_B = f(I_C)$ , dont les échelles sont logarithmiques.

### 2.3 Courant de collecteur en fonction de la tension base-émetteur $I_C = f(V_{BE})$

La fonction  $-I_E = f(V_{BE})$  est pratiquement confondue avec la fonction  $I_C = f(V_{BE})$  pour  $I_C > 10^{-9} \text{ A}$ .

Si la résistance de la connexion de base  $r_{bb'}$  est négligeable, le courant ( $-I_E$ ) dans un transistor obéit à une loi exponentielle

$$(1) \quad -I_E = I_S \left( \exp \frac{qV_{BE}}{kT} - 1 \right) \cong I_S \exp \frac{qV_{BE}}{kT}$$

si  $I_C \cong -I_E$ :

$$(2) \quad \ln I_C \cong \frac{q}{kT} V_{BE} + \ln I_S$$

équation d'une droite de pente  $\frac{q}{kT}$  si l'on porte  $I_C$  avec une échelle logarithmique.

Les mesures de la figure 2.3 donnent  $\frac{kT}{q} = 26 \text{ mV}$  pour  $\theta = 25^\circ \text{C}$ , ce qui correspond bien à la valeur théorique.

On détermine d'autre part  $I_S \cong 10^{-13} \text{ A}$ .

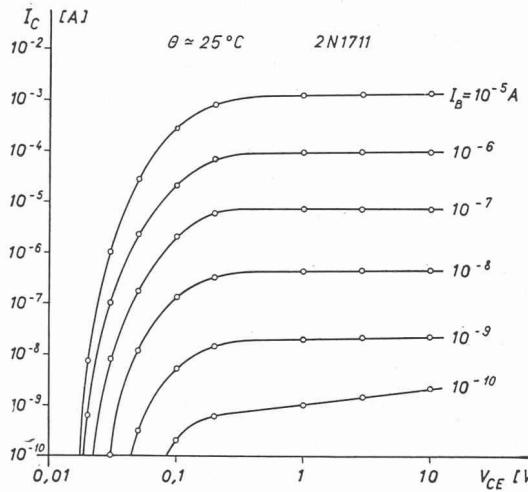

### 2.4 Courant de collecteur en fonction de la tension collecteur-émetteur pour différents courants de base

$$I_C = f(V_{CE}) \quad I_B = \text{cte}$$

\* Exemple examiné de SGS.

Fig. 2.4. — Courant de collecteur  $I_C$  en fonction de la tension collecteur-émetteur  $V_{CE}$  pour différents courants de base  $I_B$ .

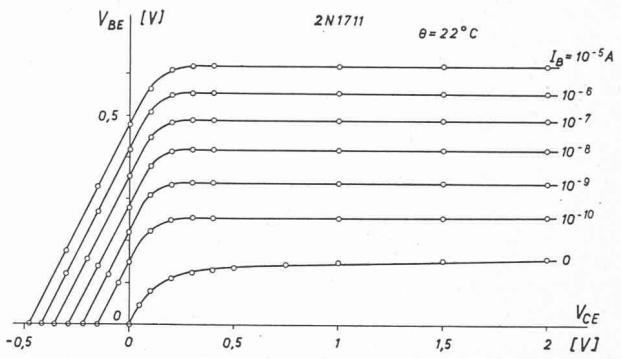

### 2.5 Tension base-émetteur en fonction de la tension collecteur-émetteur pour différents courants de base

$$V_{BE} = f(V_{CE}) \quad I_B = \text{cte}$$

### 3. Conductances d'entrée

#### 3.1 Montage base commune

Par définition  $g_e = \frac{dI_E}{dV_{EB}}$

La relation (1) étant vérifiée expérimentalement pour  $h_{fe} \gg 1$ , on obtient la valeur théorique de  $g_e$ , soit :

$$(3) \quad g_e = \frac{-I_E}{kT} \cong \frac{|I_E|}{0,026} \cong 39 |I_E| \left[ \frac{A}{V} \right]$$

pour  $\theta = 25^\circ C$ .

Ainsi,  $g_e$  ne dépend que du courant imposé à l'émetteur.

#### 3.2 Montage émetteur commun

$$(4) \quad g_{be} = \frac{dI_B}{dV_{EB}} = \frac{g_e}{1 + h_{fe}} \cong \frac{39 |I_E|}{1 + h_{fe}} = 39 \frac{I_C}{h_{fe}} \left[ \frac{A}{V} \right]$$

On peut donc, connaissant uniquement  $I_c$  ou  $-I_E$  et  $h_{fe}$ , connaître la conductance d'entrée du transistor considéré.

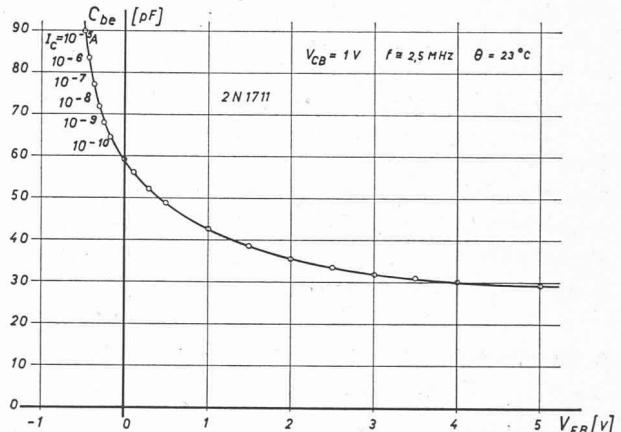

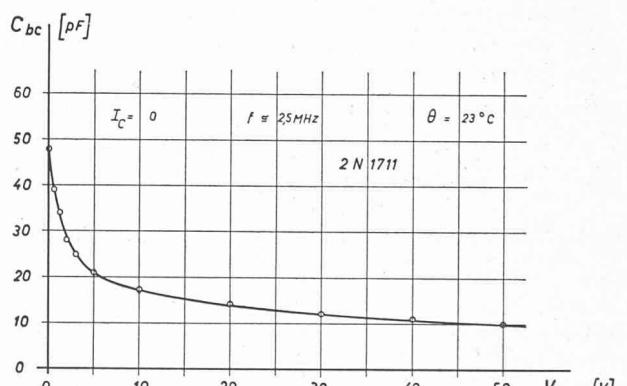

### 4. Mesure des capacités du transistor

Les mesures suivantes ont été effectuées au Q-mètre, en montage base commune.

#### 4.1 Capacité base-émetteur en fonction de la tension émetteur-base $C_{be} = f(V_{EB})$

#### 4.2 Capacité base-collecteur en fonction de la tension inverse collecteur-base $C_{bc} = f(V_{CB})$

On peut remarquer que, lorsque les jonctions sont polarisées en sens bloquant, les capacités de charge d'espace de ces jonctions obéissent à une loi de la forme

Fig. 2.5. — Tension base-émetteur  $V_{BE}$  en fonction de la tension collecteur-émetteur  $V_{CE}$  pour différents courants de base  $I_B$ .

Fig. 4.1. — Capacité base-émetteur  $C_{be}$  en fonction de la tension émetteur-base  $V_{EB}$ .

Fig. 4.2. — Capacité base-collecteur  $C_{bc}$  en fonction de la tension collecteur-base  $V_{CB}$ .

$$(5) \quad C = A(V + V_o)^{-\frac{1}{3}}$$

où  $V_o$  est la hauteur de la barrière de potentiel de la jonction considérée en l'absence de polarisation extérieure.

Dans le sens de la conduction,  $C_{be}$  suit encore cette loi dans notre cas, c'est-à-dire que la capacité de diffusion est jusqu'à un courant  $I_C$  de  $10^{-5} A$  négligeable par rapport à la capacité de charge d'espace de la jonction.

Ce résultat correspond à la capacité d'une jonction où la transition entre les deux types d'impuretés est graduelle et linéaire.

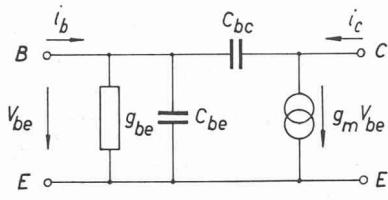

Fig. 5.1. — Schéma équivalent pour l'amplification de faibles accroissements  $i_c$ ,  $i_b$ ,  $V_{be}$ .

### 5. Schéma équivalent au transistor pour l'amplification de signaux de faible amplitude

Les résultats précédents mènent naturellement au schéma équivalent simplifié de la figure 5.1.

Si l'on ajoute à ce schéma une résistance  $r_{bb'}$  en série dans la connexion de base et des conductances  $g_{bc}$  et  $g_{ce}$  en parallèle sur les bornes  $B-C$  et  $C-E$ , on obtient le schéma équivalent en  $\pi$  couramment utilisé dans les circuits conventionnels en haute fréquence. Ces grandeurs sont pratiquement négligeables dans notre cas et n'ont pas été représentées (2N 1711 :  $r_{bb'} = 50 \Omega$ ).

La conductance mutuelle  $g_m$  vaut pratiquement  $g_e$  dont la valeur est indiquée dans la formule (3), tant que le gain en courant  $h_{fe} \gg 1$ .

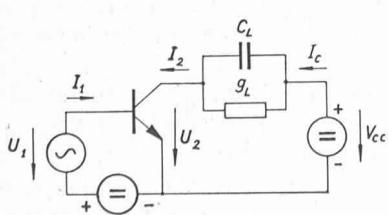

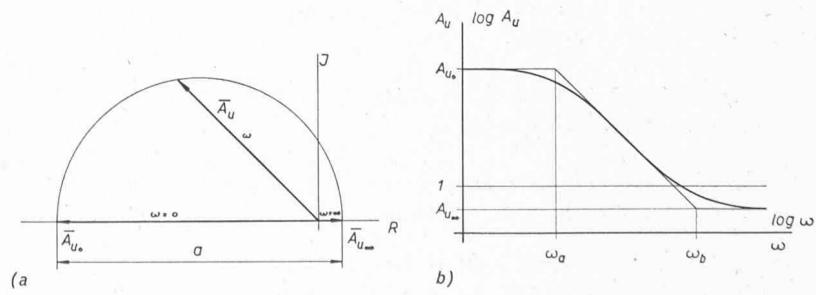

### 6. Amplification de faibles signaux sinusoïdaux

Les éléments du schéma équivalent de la figure 5.1 étant maintenant connus, on peut exprimer les rapports d'amplification de tension  $A_u$  et de courant  $A_i$ , lorsque le transistor est chargé par une admittance quelconque  $\bar{Y}_L$ .

Supposons l'exemple de l'amplificateur de la figure 6.1 où le transistor est chargé par une admittance  $\bar{Y}_L = g_L + j\omega C_L$ .

On obtient pour  $\bar{A}_u$  :

$$(6) \quad \bar{A}_u = \frac{\bar{U}_2}{\bar{U}_1} = \frac{-g_m + j\omega C_{bc}}{g_L + j\omega(C_L + C_{bc})}$$

qui peut se mettre également sous la forme

$$(7) \quad \bar{A}_u = \frac{C_{bc}}{C_L + C_{bc}} - \frac{\frac{g_m}{g_L} + \frac{C_{bc}}{C_L + C_{bc}}}{1 + j\omega \frac{C_L + C_{bc}}{g_L}} = \bar{A}_{u_0} \frac{1 - j\frac{\omega}{\omega_a}}{1 + j\frac{\omega}{\omega_a}}$$

où nous appellerons

$$\bar{A}_{u_0} = -\frac{g_m}{g_L} \quad \bar{A}_{u_\infty} = \frac{C_{bc}}{C_L + C_{bc}}$$

Fig. 6.1. — Amplificateur chargé par une admittance  $\bar{Y}_L = g_L + j\omega C_L$ .

$$\begin{aligned} \omega_b &= \frac{g_L}{C_L + C_{bc}} & \omega_a &= \frac{g_m}{C_{bc}} \\ a &= \left| \bar{A}_{u_0} \right| + \left| \bar{A}_{u_\infty} \right| = \frac{g_m}{g_L} + \frac{C_{bc}}{C_L + C_{bc}} \end{aligned}$$

ce qui amène aux représentations de la figure 6.2.

Pour  $\bar{A}_i$ , nous avons :

$$(8) \quad \bar{A}_i = \frac{g_L g_m + \omega^2 C_L C_{bc} + j\omega(C_L g_m - g_L C_{bc})}{g_L g_{be} - \omega^2 [C_L(C_{be} + C_{bc}) + C_{be} C_{bc}] + j\omega[g_L(C_{be} + C_{bc}) + C_L g_{be} + C_{bc}(g_m + g_{be})]}$$

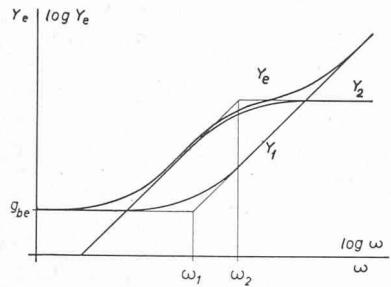

Cette expression n'exprime pas clairement l'allure de ses variations en fonction de la pulsation  $\omega$  du signal appliqué. Aussi, pour analyser cette grandeur  $\bar{A}_i$  peut-on partir de la relation :

$$(9) \quad \bar{A}_i = -\bar{A}_u \frac{\bar{Y}_L}{\bar{Y}_e}$$

où  $\bar{Y}_e$ , l'admittance d'entrée du transistor, est donnée par :

$$(10) \quad \begin{aligned} \bar{Y}_e &= \underbrace{g_{be} + j\omega \left( C_{be} + \frac{C_L C_{bc}}{C_L + C_{bc}} \right)}_{\bar{Y}_1} + \\ &+ \underbrace{\frac{1}{j\omega a C_{bc}} + \frac{C_L + C_{bc}}{a C_{bc} g_L}}_{\bar{Y}_2} \end{aligned}$$

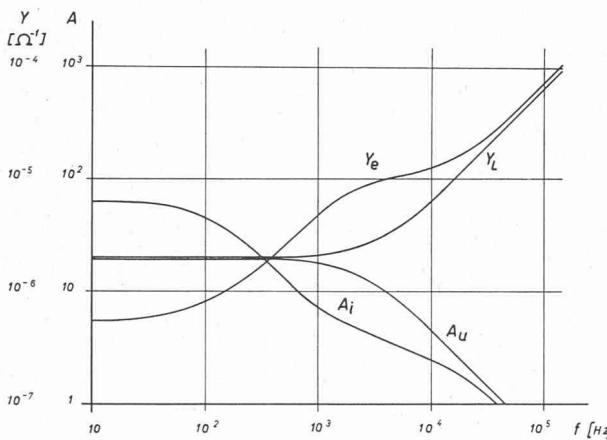

qui est la somme de deux termes  $\bar{Y}_1$  et  $\bar{Y}_2$ , dont la représentation en fonction de  $\omega$  est donnée en figure 6.3.

Les grandeurs suivantes caractérisent ces deux termes :

$$\begin{aligned} \bar{Y}_{1_0} &= g_{be} & \bar{Y}_{2_\infty} &= a g_L \frac{C_{bc}}{C_L + C_{bc}} \\ \omega_1 &= \frac{g_{be}}{C_{be} + \frac{C_L C_{bc}}{C_L + C_{bc}}} & \omega_2 &= \frac{g_L}{C_L + C_{bc}} \end{aligned}$$

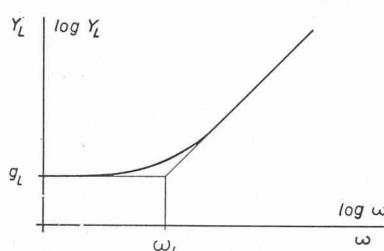

D'autre part,  $\bar{Y}_L = g_L + j\omega C_L$  est représenté à la figure 6.4 où  $\omega_L = \frac{g_L}{C_L}$ .

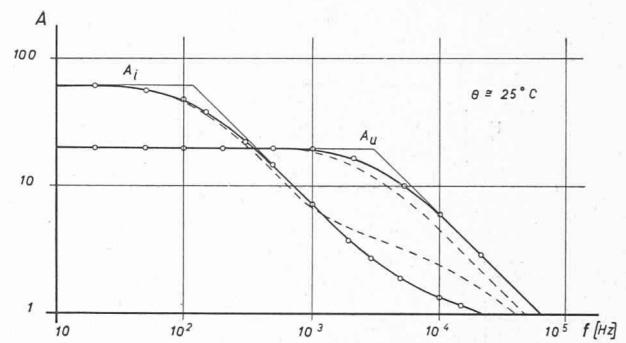

Nous obtenons alors  $A_i$  en fonction de la fréquence  $f$  à la figure 6.5 pour l'exemple d'un amplificateur, tel que celui de la figure 6.1, où les valeurs numériques seraient les suivantes :

Fig. 6.2. — Amplification de tension  $A_u$  de l'amplificateur de la figure 6.1.

a) représentation vectorielle

b) représentation logarithmique en fonction de  $\omega$

Fig. 6.3. — Admittance d'entrée  $Y_e$  en fonction de la pulsation  $\omega$  du signal appliquée ( $Y_1$ ,  $Y_2$ , voir texte).

Fig. 6.4. — Admittance de charge  $Y_L$  en fonction de la pulsation  $\omega$ .

Fig. 6.6. — Application de courant  $A_i$  et de tension  $A_u$  en fonction de la fréquence  $f$ .

— mesures

--- calculs

Fig. 6.5. — Détermination de l'amplification de courant  $A_i$  en fonction de la fréquence  $f$  du signal appliqué.

$A_u$  = amplification de tension

$Y_e$  = admittance d'entrée

$Y_L$  = admittance de charge

$$A_i = A_u \frac{Y_L}{Y_e}$$

$$I_c = 1 \mu\text{A}$$

$$h_{fe} = 65$$

$$V_{CC} = 2 \text{ V}$$

$$g_{be} = 5,5 \cdot 10^{-7} \frac{\text{A}}{\text{V}}$$

$$g_L = 2 \cdot 10^{-6} \frac{\text{A}}{\text{V}}$$

$$C_{be} = 85 \text{ pF}$$

$$C_L = 100 \text{ pF}$$

$$C_{bc} = 35 \text{ pF}$$

Les mesures des grandeurs  $A_i$  et  $A_u$  que nous avons effectuées sont données à la figure 6.6, où l'on a porté en pointillé les valeurs obtenues par calculs.

On remarque que les mesures correspondent à une capacité  $C_L$  de 70 pF et non de 100 pF.

Ces résultats justifient l'emploi de notre schéma équivalent pour les faibles courants. Ces calculs montrent les effets des diverses capacités parasites qui se font sentir à des fréquences basses pour des capacités relativement faibles.

## 7. Comportement du transistor en régime transistoire de forte amplitude

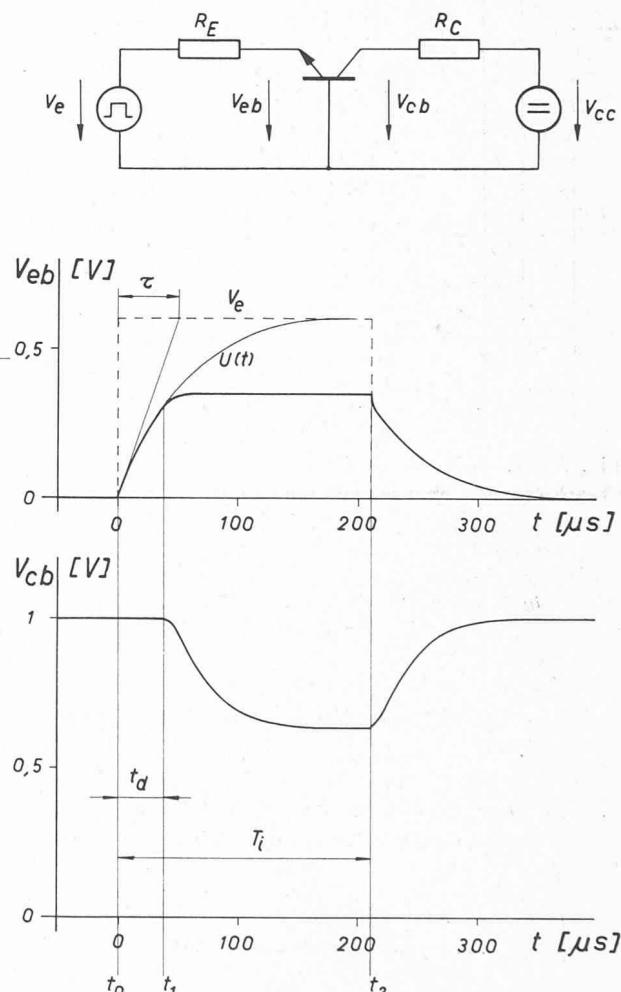

### 7.1 Mise en conduction et blocage du transistor en montage base commune

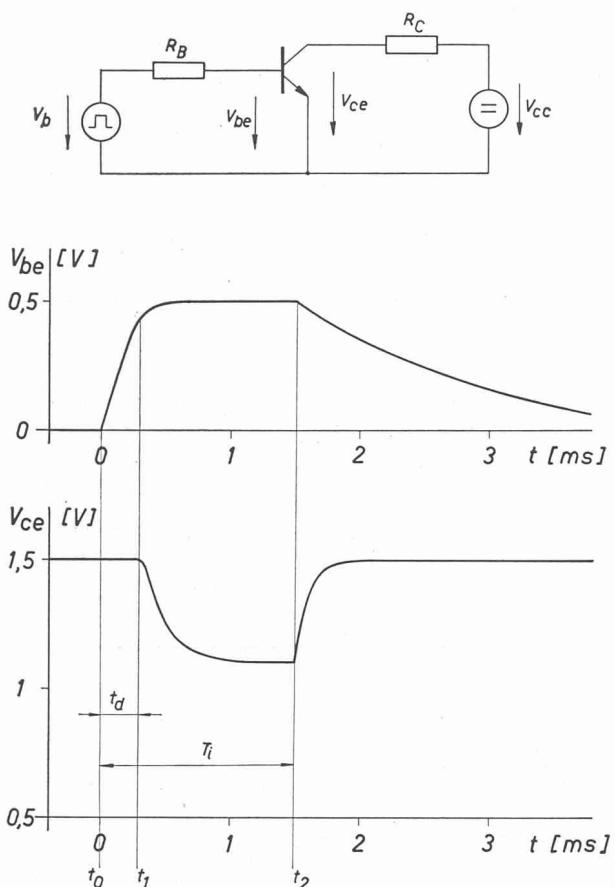

On voit (fig. 7.1) que le circuit d'entrée se comporte comme une résistance  $R_E$  en série avec une capacité  $C_{be}$  jusqu'à l'instant où  $g_{be}$  n'est plus nulle, c'est-à-dire au moment où le transistor commence à conduire.

Fig. 7.1. — Mise en conduction et blocage du transistor en montage base commune.

$$V_e = -0,6 \text{ V}$$

$$R_E = 400 \text{ k}\Omega$$

$$V_{CC} = 1 \text{ V}$$

$$R_C = 820 \text{ k}\Omega$$

$$t_i = 220 \mu\text{s}$$

$$C_{be} + C_p = 125 \text{ pF}$$

$$C_{bc} + C_L = 90 \text{ pF}$$

Le courant  $i_c$  passe de 0 à environ 1 μA.

Durant l'intervalle de temps  $t_d = (t_1 - t_0)$ , la tension varie selon l'expression :

$$(11) \quad U(t) = V_e \left( 1 - e^{-\frac{t}{\tau}} \right)$$

où  $\tau$ , la constante de temps du système est égale à  $R_E(C_{be} + C_p)$ .  $C_p$  = capacité en parallèle entre base et émetteur due aux instruments de mesure.

Fig. 7.2.1. — Mise en conduction et blocage du transistor commandé en courant en montage émetteur commun.

$$\begin{aligned} V_b &= 2 \text{ V} & R_B &= 10 \text{ M}\Omega \\ V_{CC} &= 1,5 \text{ V} & R_C &= 47 \text{ k}\Omega \\ T_i &= 1,5 \text{ ms} & & \\ i_C \text{ passe de } 0 \text{ à environ } 10 \mu\text{A}. \end{aligned}$$

Cette expression permet de déterminer  $C_{be}$ , à partir de  $V_{eb}(t)$ .

## 7.2 Mise en conduction et blocage du transistor en montage émetteur commun sans atteindre la saturation

Fig. 7.2.1 Commande en courant

Fig. 7.2.2 Commande en tension

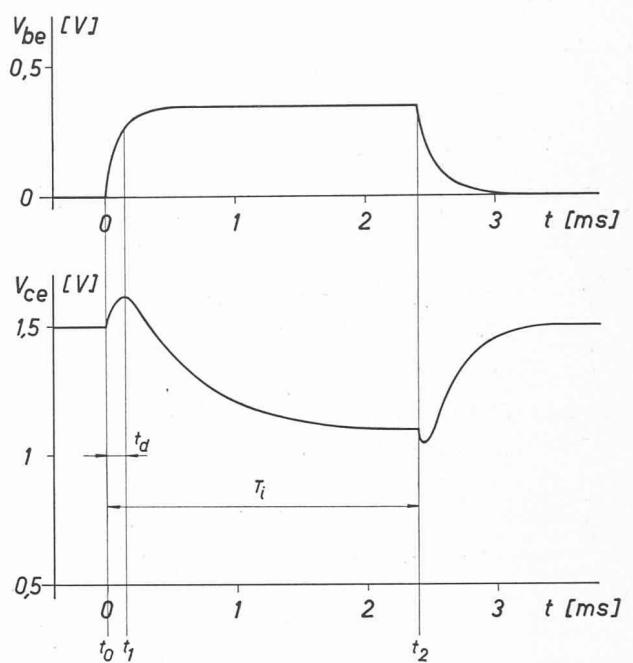

Lorsque le transistor est commandé en tension, la capacité  $C_{be}$  sera chargée plus rapidement que dans le cas de la commande en courant, et par conséquent l'intervalle de temps  $t_d$  sera plus court ; d'autre part, la conductance d'entrée du transistor  $g_{be}$  n'aura que peu d'influence sur la forme de  $V_{be}$  en fonction du temps, cette conductance étant pratiquement court-circuitée par l'impédance du générateur (dans notre exemple de la figure 7.2.2,  $R_B \approx 0,6 \text{ M}\Omega$  reste toujours inférieure à la valeur la plus faible de  $\frac{1}{g_{be}} \approx 11 \text{ M}\Omega$  atteinte pour  $I_c = 0,1 \mu\text{A}$ ).

On voit encore que, dans ce cas, les fronts des montées et descentes de la tension  $V_{be}$  seront transmis au collecteur par la capacité  $C_{bc}$ .

Fig. 7.2.2. — Mise en conduction et blocage du transistor commandé en tension en montage émetteur commun.

$$\begin{array}{ll} \text{Schéma de mesure donné sous 7.2.1} & \\ V_b = 0,37 \text{ V} & R_B = 630 \text{ k}\Omega \\ V_{CC} = 1,5 \text{ V} & R_C = 5 \text{ M}\Omega \\ T_i = 2,4 \text{ ms} & \\ i_C \text{ passe de } 0 \text{ à environ } 0,1 \mu\text{A}. \end{array}$$

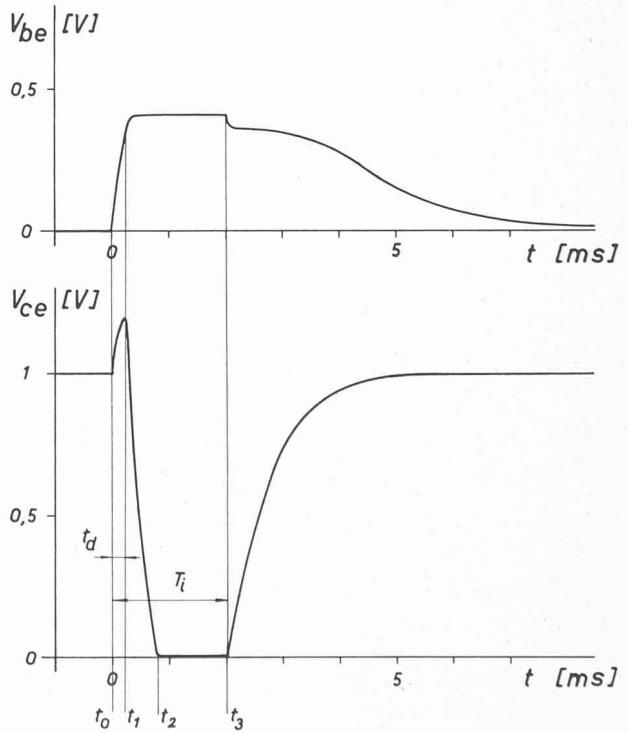

Fig. 7.3. — Saturation et blocage du transistor en montage émetteur commun (schéma, voir sous 7.2.1).

$$\begin{array}{ll} V_b = 2 \text{ V} & R_B = 13,3 \text{ M}\Omega \\ V_{CC} = 1 \text{ V} & R_C = 10 \text{ M}\Omega \\ T_i = 2 \text{ ms} & \\ i_C \text{ passe de } 0 \text{ à } 0,1 \mu\text{A}. \end{array}$$

Remarquons que les trois exemples précédents ne sont pas directement comparables, vu que les courants de collecteur varient fortement d'un cas à l'autre.

### 7.3 Saturation et blocage du transistor en montage émetteur commun

Les mêmes remarques que pour les essais précédents sont valables dans ce cas ; cependant, bien que le transistor soit commandé en courant, on voit déjà apparaître au collecteur les pointes de tension, dues à  $C_{bc}$ , car le courant de commande est beaucoup plus élevé.

Ajoutons que, pour autant que le transistor reste bien saturé, le temps de descente  $t_2 - t_1$  de la tension  $V_{ce}$  n'est que peu influencé par la valeur de la résistance de charge ; par contre, le temps de remontée de cette même tension dépend beaucoup de celle-ci.

### Conclusion

Nous constatons que l'étude de dispositifs à faibles courants, utilisant des transistors « Planar », tels que le

type utilisé comme exemple, peut se ramener à l'étude de dispositifs conventionnels, fonctionnant avec des transistors classiques.

Dans le cas présent cependant, il est possible de négliger complètement  $r_{bb'}$  et  $g_{bc}$ .

On remarque encore que les limites de fonctionnement aux fréquences « élevées » sont dues essentiellement aux capacités  $C_{be}$  et  $C_{bc}$ .

Il existe actuellement d'autres types de transistors « Planar » pour hautes fréquences (2N 708, 2N 929, ...) dont les capacités plus faibles permettent de meilleures performances.

Ces capacités restent cependant relativement élevées (de l'ordre de grandeur de 10 pF pour les transistors mentionnés), mais notons que ces transistors sont prévus pour fonctionner à de forts courants : 1 à 10 mA ou plus (2N 1711 :  $W_{max} = 3 \text{ W à } 25^\circ \text{ C}$ ). Aussi, l'idéal serait-il de disposer d'éléments prévus spécialement pour fonctionner aux très faibles courants et dont les capacités seraient nettement plus faibles que celles des transistors actuels.

## BIBLIOGRAPHIE

**Mémento technique de l'eau**, par R. Leviel, directeur technique et collaborateur de la Société « Degremont ». Edition 1963. — Un volume 12×18 cm de 644 pages, 251 figures, 245 schémas et diagrammes. Prix : relié toile, 47.30 F français.

Le succès des précédentes éditions a conduit la Société Degremont, spécialiste mondial connu du traitement des eaux, à publier une nouvelle édition. Celle-ci comporte cent pages de plus que la précédente. Tous les chapitres ont fait l'objet de remaniements importants, tenant compte des derniers progrès scientifiques et techniques. La partie « Biologie » a été fortement développée et comporte une étude nouvelle de dix-sept pages sur le plancton. Des extraits des Recommandations de l'Organisation mondiale de la Santé indiquent la tendance probable des législations nationales.

Ce livre, autant scientifique que technique, intéressera les industriels, les ingénieurs-conseil et les employés de laboratoire et des services intéressés à la distribution et à l'évacuation des eaux. Ils y trouveront les enseignements pratiques pour mettre en œuvre les techniques anciennes et nouvelles concernant les analyses et le traitement des eaux.

#### Extrait de la table des matières :

La chimie de l'eau. — Dosage des réactifs. — Décantation. — Filtration. — Stérilisation. — Neutralisation. — Défermentation. — Démanganisation. — Echangeurs d'ions. — Epuration chimique des eaux. — Epuration et conditionnement des eaux de chaudières. — Traitement des eaux de piscines. — Procédés divers. — Epuration des eaux résiduaires. — Législation et réglementation des eaux. — Formulaire.

**Les grues à tour. Nécessité et dangers de leur utilisation**, par le professeur Victor Raymond, médecin-conseil de l'« Organisme professionnel de prévention du bâtiment et des travaux publics ». Paris, Eyrolles (1962). — Un volume 16×25 cm, 72 pages, 13 photographies, 3 figures et 8 tableaux. Prix : broché, 9,50 F.

Les grues à tour se sont multipliées durant ces dernières années, au point qu'elles constituent maintenant un élément courant du paysage urbain. Mais, si ces appareils de levage présentent des avantages évidents pour la mécanisation des chantiers, leur emploi a mal-

heureusement amené des accidents particulièrement spectaculaires. En quatre années, on a en effet déploré 133 victimes, dont 47 décès.

C'est la raison pour laquelle l'OPPBTP a étudié les problèmes posés pour l'utilisation généralisée des grues à tour. Il a rappelé aux utilisateurs les règles et recommandations techniques dont l'observation est apparue indispensable afin de prévenir les accidents. Les études entreprises ont fait apparaître la primauté du facteur humain dans cette question, en apparence purement matérielle. Dans la pratique courante, il s'agit généralement d'accidents mixtes. En effet, si bien conçue que soit une grue à tour, et quels que soient ses perfectionnements, c'est une machine complexe nécessitant une manipulation délicate. Il ne suffit pas de disposer d'une grue idéale ; il importe essentiellement que sa manœuvre soit confiée à un grutier expérimenté et averti des risques d'accidents, de leurs causes et de leur prévention.

C'est à ce problème que s'est attaché l'auteur de cette étude, en reproduisant in extenso toutes les observations d'accidents analysées par l'OPPBTP durant ces dernières années. Cet exposé a pour but de conduire le lecteur à se faire une opinion personnelle basée sur une variété très étendue de cas judicieusement choisis, étudiés et commentés en détail.

A ce titre, le travail du professeur Raymond intéressera les ingénieurs, les entrepreneurs, les chefs de chantiers, les préventeurs, les médecins du travail, les grutiers...

#### Sommire :

Nécessité de l'utilisation des grues à tour. Accidents de montage et de démontage. Chutes de grues. Chutes de flèches. Vent. Chutes d'objets ou de matériaux. Ouvriers déséquilibrés par la grue. Accidents dus à l'électricité. Prévention. Le grutier : étude de poste. Synthèse et conclusions.

**Vocabulary of foundry practice**. Pergamon Press, 1963.

— Un volume 18×25 cm, 307 pages, 117 figures. Prix : relié sous jaquette, £ 6.

Ce vocabulaire en six langues : *anglais, allemand, français, tchècoslovaque, polonais et russe*, contient 1269 termes avec définitions, ainsi que 117 illustrations concernant la technique de fonderie, métallographie et des domaines apparentés.

Ce vocabulaire contient en particulier : les notions générales de fonderie, les termes appartenant à la fusion